Arrow Lake, des tuiles sur PC de bureau !

Alors qu’Intel a, pendant ses nombreuses années de domination, mis au point ses finesses de gravure en les fiabilisant sur des CPU hors de prix à destination des professionnels ; avant de réutiliser ces lithographies une fois compétitives sur le segment grand public, cette ère est définitivement enterrée. En effet, les bleus sont désormais à la traîne en ce qui concerne les technologies de confection de circuits imprimés miniatures, si bien que le géant de Santa Clara se bat à armes quasi égales avec son concurrent de toujours, AMD — comprenez par là que les deux emploient TSMC pour graver le silicium qui, ultimement, est intégré dans leurs puces. Cependant, les solutions techniques employées diffèrent entre un Zen 5 ayant recourt à des chiplets et Arrow Lake basé sur des tuiles : le premier passe directement par le substrat pour relier ensemble ses dies (moins coûteux, mais moins performant), là où le second emploi un interposer (la seule partie fabriquée directement en interne) pour relier des bouts de silicium empilés en 2,5 D par la technologie maison Foveros.

Si cela est une première pour les joueurs et autres aficionados du PC fixe, la chose a déjà été étrennée côté laptops avec Meteor Lake et Lunar Lake. Ainsi, dans une logique de rationalisation des coûts, Intel se doit de partager au maximum les dies (unités physiques de silicium), mais aussi les IP (unités logiques telles que les cœurs CPU) sur Arrow Lake, arrivant à un tout qui peut sembler paradoxal puisque, en regardant de plus près, toutes les briques à l’œuvre dans cette génération ont déjà été introduites sur des microarchitectures plus ou moins anciennes. Rien de mal à cela — toutes les autres générations mobiles des bleus étaient déjà directement dérivées des gammes desktop —, cependant nous vous conseillons de suivre nos analyses précédentes si vous souhaitez plus de détails sur certains blocs logiques (pas de panique, les liens hypertextes sont là pour ça !).

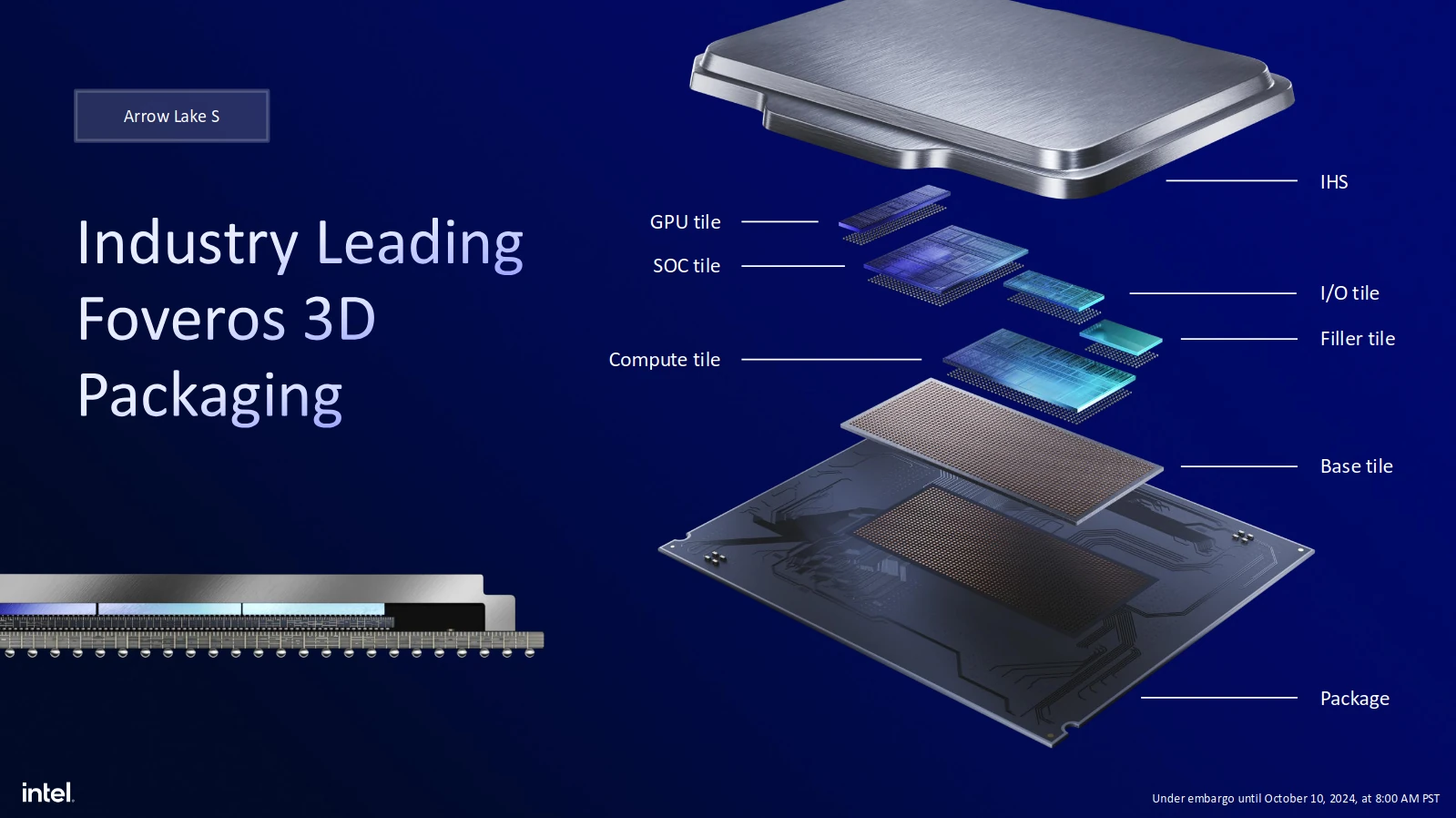

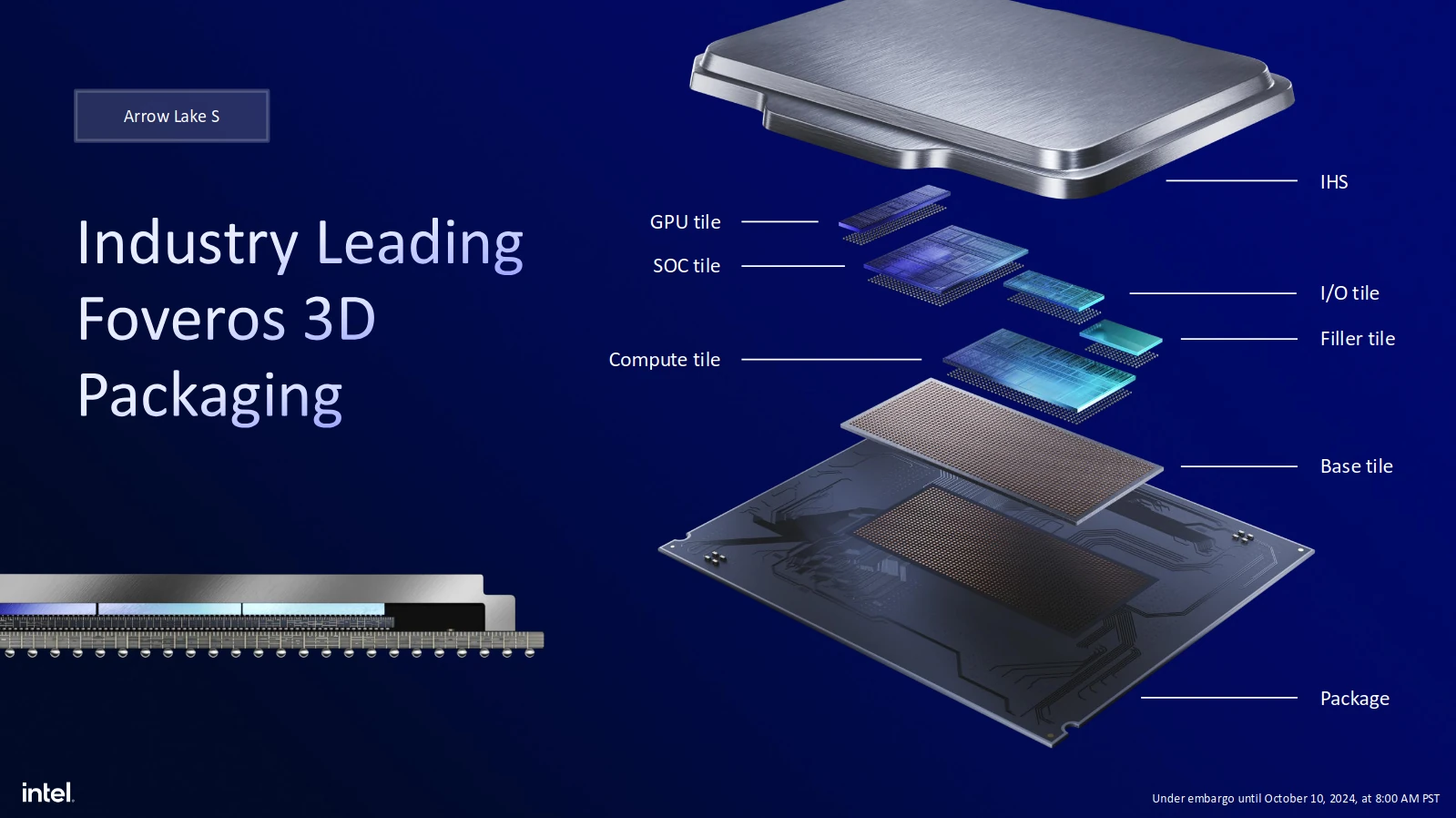

Cette mise en contexte effectuée, que nous apporte Arrow Lake ? Pas moins de 4 dies (et un filler permettant de former un joli rectangle) remplissant chacun un rôle qui lui est propre, manufacturés avec une technologie adaptée à leur niveau de performance dans le but de revenir à une consommation raisonnée :

- Une Compute Tile en N3B

- Une GPU Tile, en N5P, pour la partie graphique

- Une SoC Tile (incluant l’accélérateur d’IA) et une I/O Tile, toutes deux en N6

- Une base Tile passive (pas de transistor, que de l’interconnect) en Intel P1227.1 ; de la même manière que Lunar Lake, il est question des metal layers de l’Intel 4 en version optimisée pour le SoC/communications)

Avec autant d’éléments distincts, le delta de fonctionnalités par rapport à Raptor Lake Refresh se doit d’être vertigineux : détaillons ainsi tour à tout ce que renferme chacune de ces tuiles.

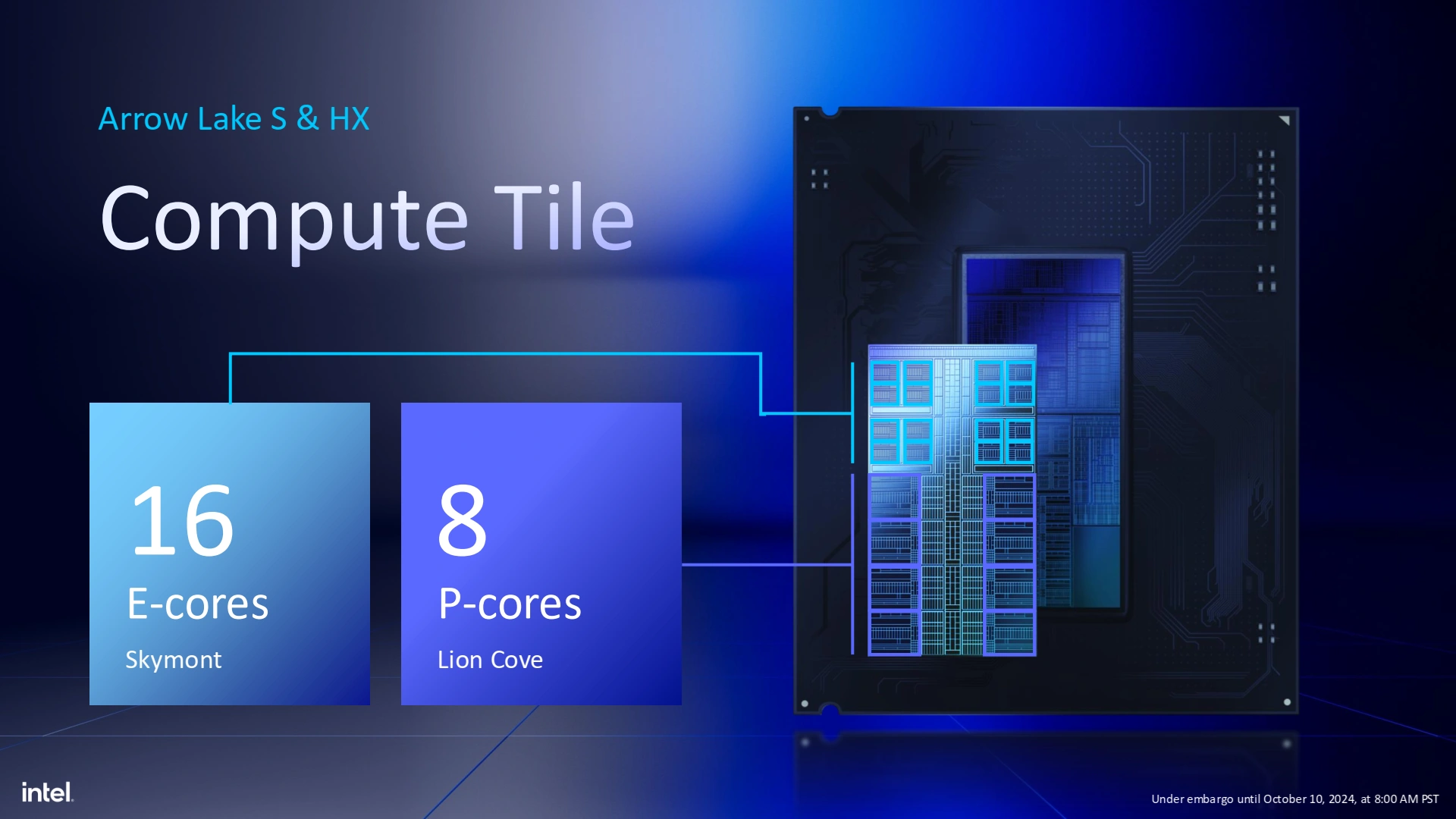

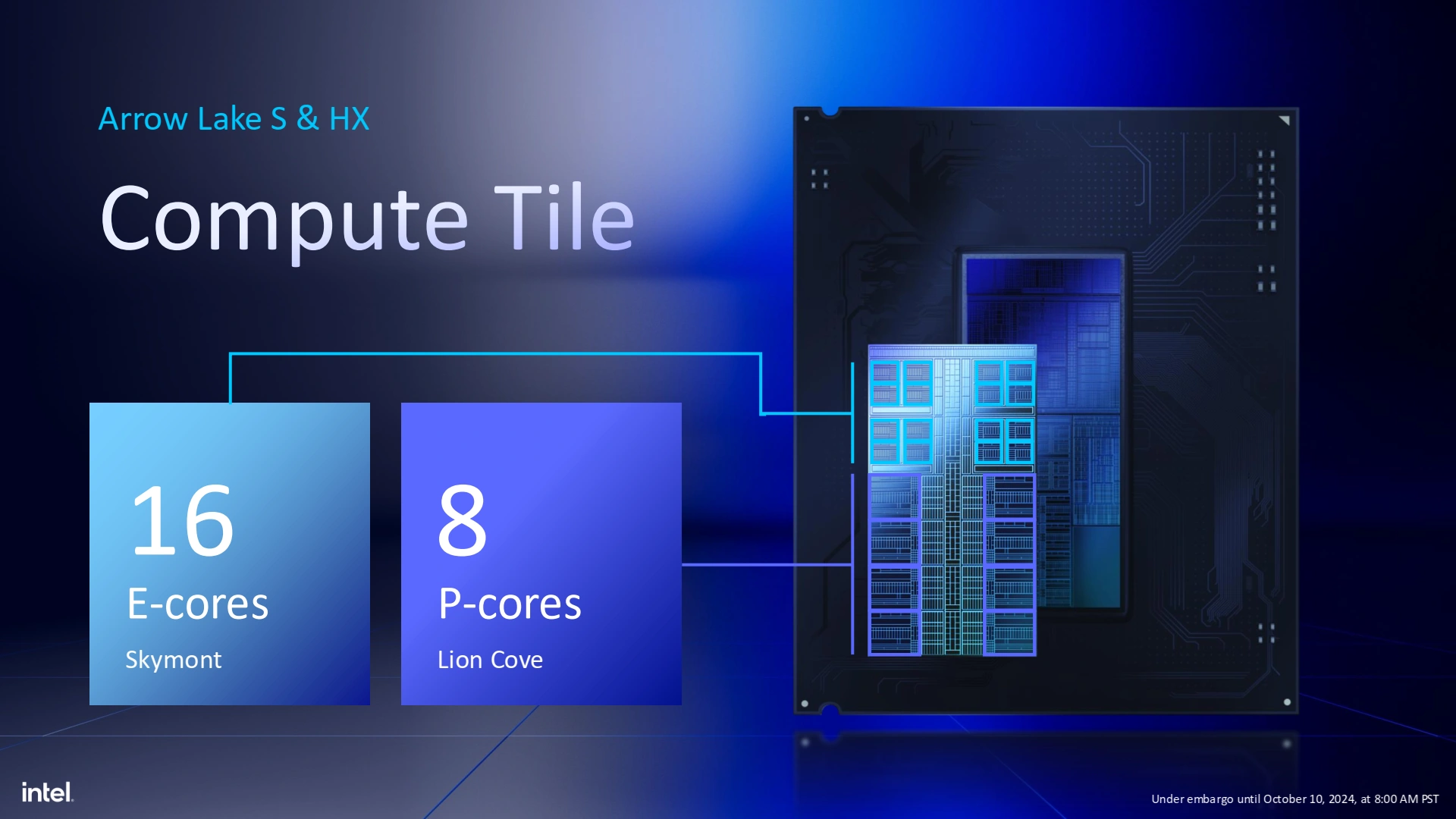

Tuile CPU : Lion Cove et Skymont, version haute performance

Comme tout processeur grand public sur socket des bleus, Arrow Lake se doit de briller avant tout pour sa partie CPU. Ici, Intel y consacre logiquement une tuile complète, gravé à l’aide du procédé le plus avancé disponible actuellement, le N3B de TSMC. Au niveau micro-architectural, nous retrouvons un assemblage hétérogène de 8 cœurs « Performance », aussi appelés P-Core et 16 cœurs « Efficient » — E-Core — adaptant sur un TDP de 100-200 W les designs testés sur Lunar Lake : le performant Lion Cove et l’efficace Skymont. En piste !

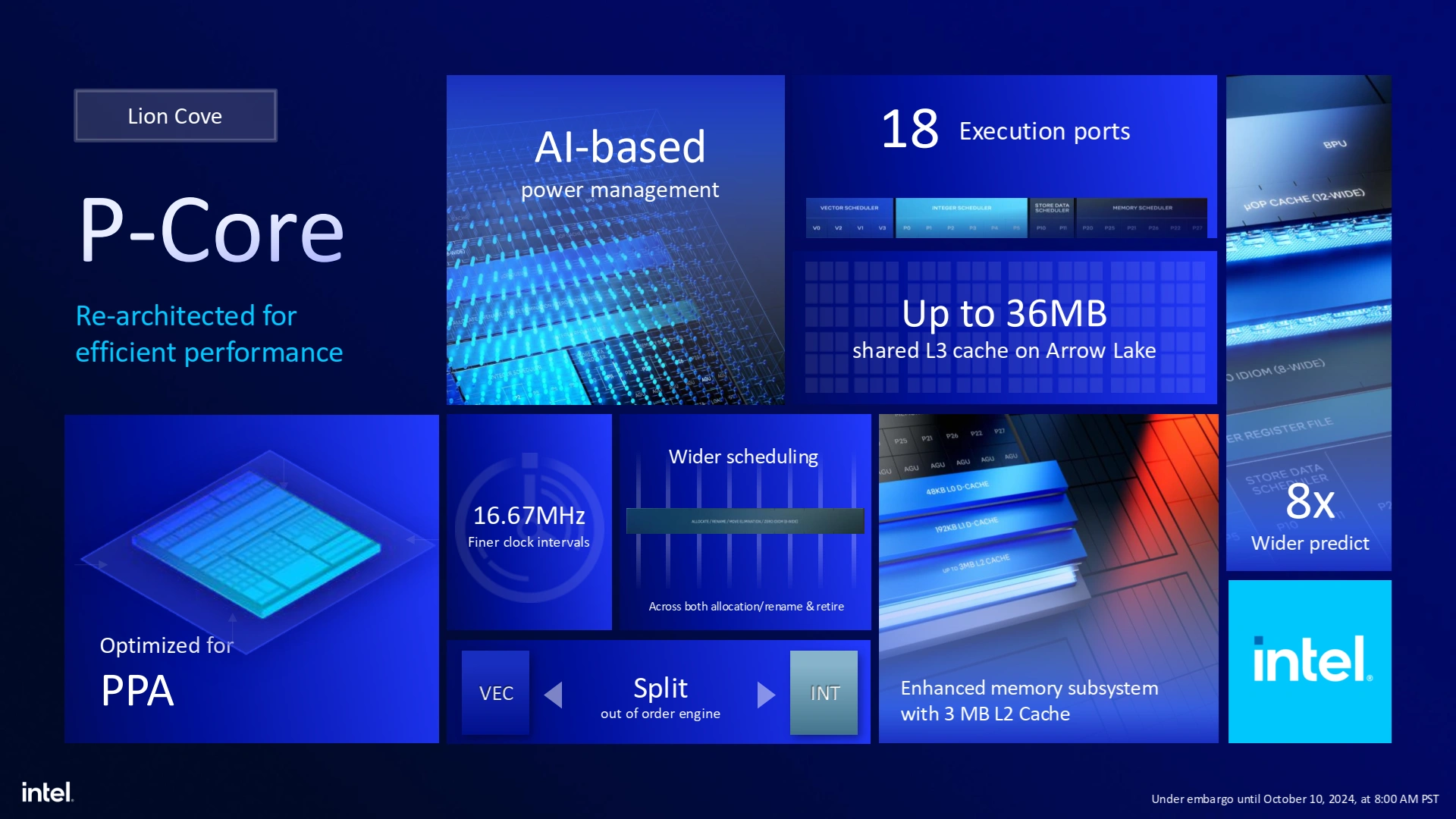

Similairement à la version de Lion Cove utilisée sur Lunar Lake, le premier changement visible par l’utilisateur côté P-Core (microarchitecture Lion Cove) est la disparition de l’Hyperthreading. En effet, si la technologie permet d’obtenir la meilleure performance par unité de surface (comprendre, performance/prix de production), cela s’effectue également au prix d’une consommation sensiblement plus élevée. Or, sur le segment grand public ou la plupart des logiciels/jeux ne bénéficient que très peu de plus de 8 cœurs, retirer cette technologie permet de conserver un niveau de performance haut tout en revenant à des TDP plus raisonnables : le credo d’Arrow Lake.

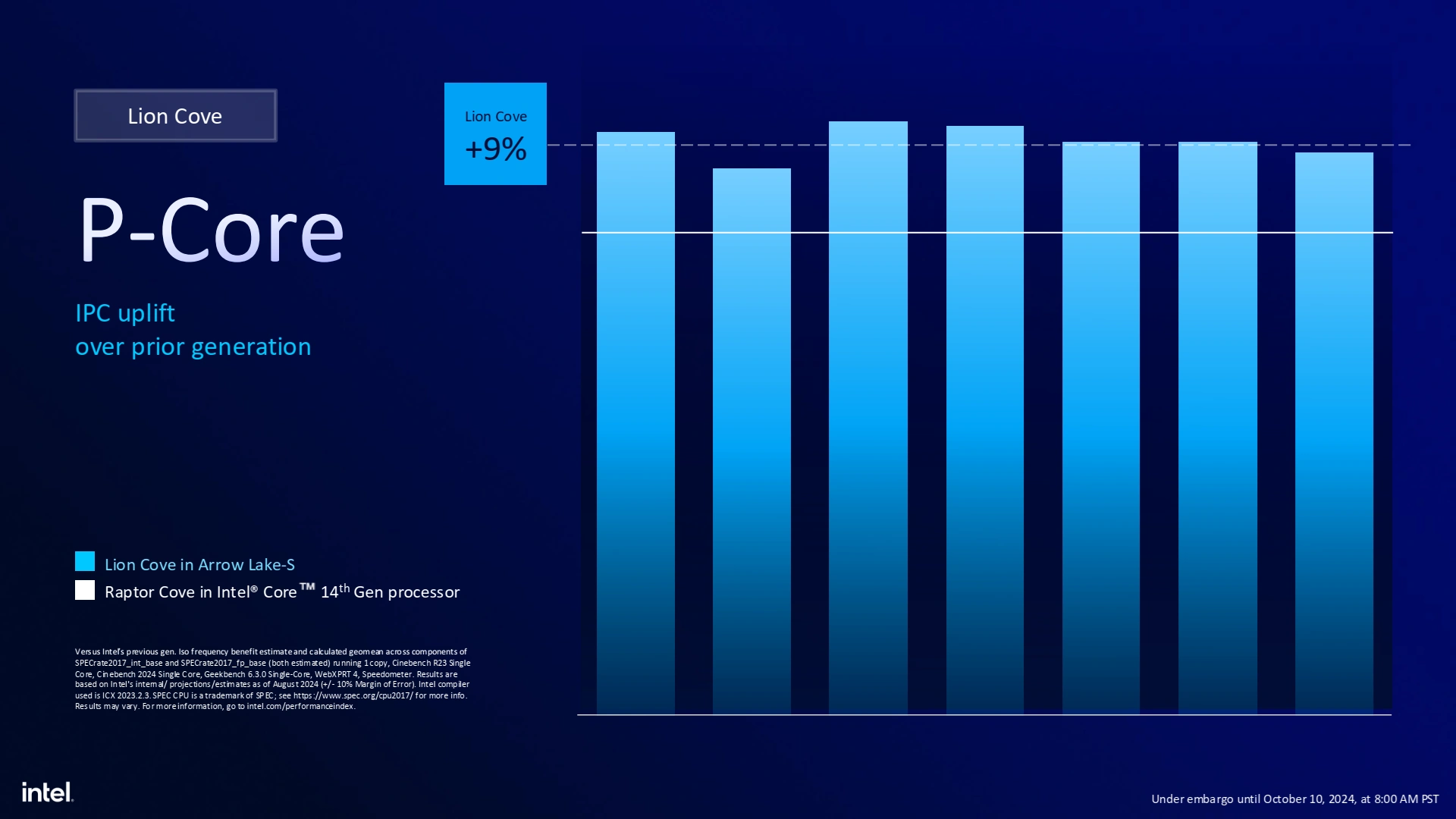

Heureusement, Lion Cove ne s’arrête pas là et bénéficie d’une mise à niveau complète de tout son pipeline d’exécution : le Front-End, chargé d’alimenter les unités de calculs en opérations, est gonflé par une prédiction de branchement opérant sur des blocs plus larges, un cache des instructions décodées toujours plus grand et une bande passante vers le L1-I également en hausse. Du côté du Back-End, le pipeline d’exécution l’élargit lui aussi en passant de 12 ports sur Raptor Cove à 18, de quoi booster les performance aussi bien des instructions de calcul entier, mais aussi pour le calcul SIMD et flottant (désormais séparé), et les chargements-rangements. Pour le détail exact, rendez-vous sur notre couverture de Lunar Lake !

Autrement, nous notons l’arrivée d’un cache L0 de 48 kio portant à 4 le nombre de niveaux de cache (L0, L1, L2, L3), le L1 explosant à 192 Kio, le L2 à 3 Mio maximum et le L3 cube à 36 Mio dans la configuration la plus musclée. De côté du jeu d’instructions, l’AVX-512 n’est toujours pas de mise (la faute incombant aux E-Core), cependant le VNNI (extension pour le machine learning) est présent en version 256-bit, c’est-à-dire au-dessus de l’AVX2.

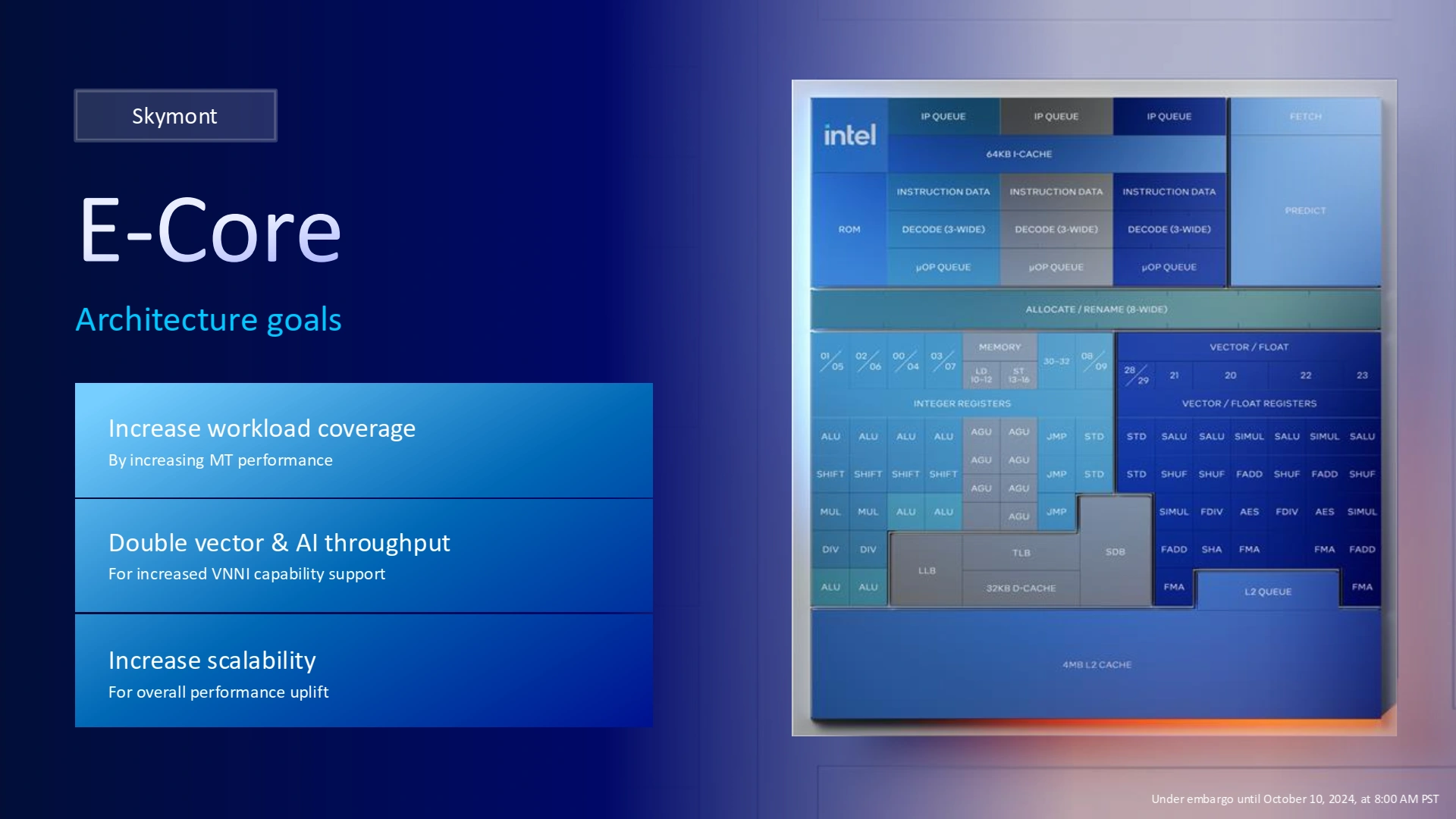

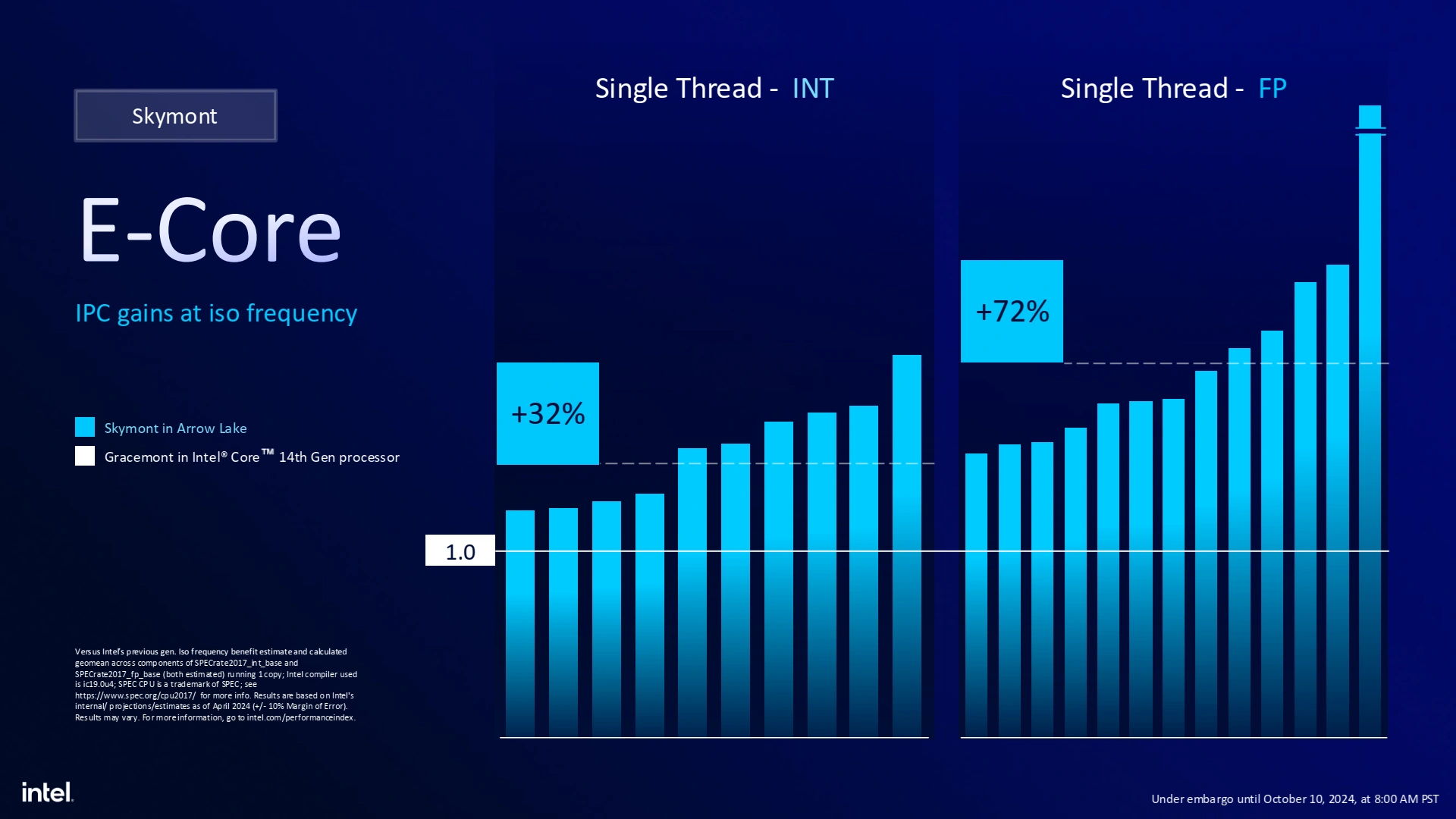

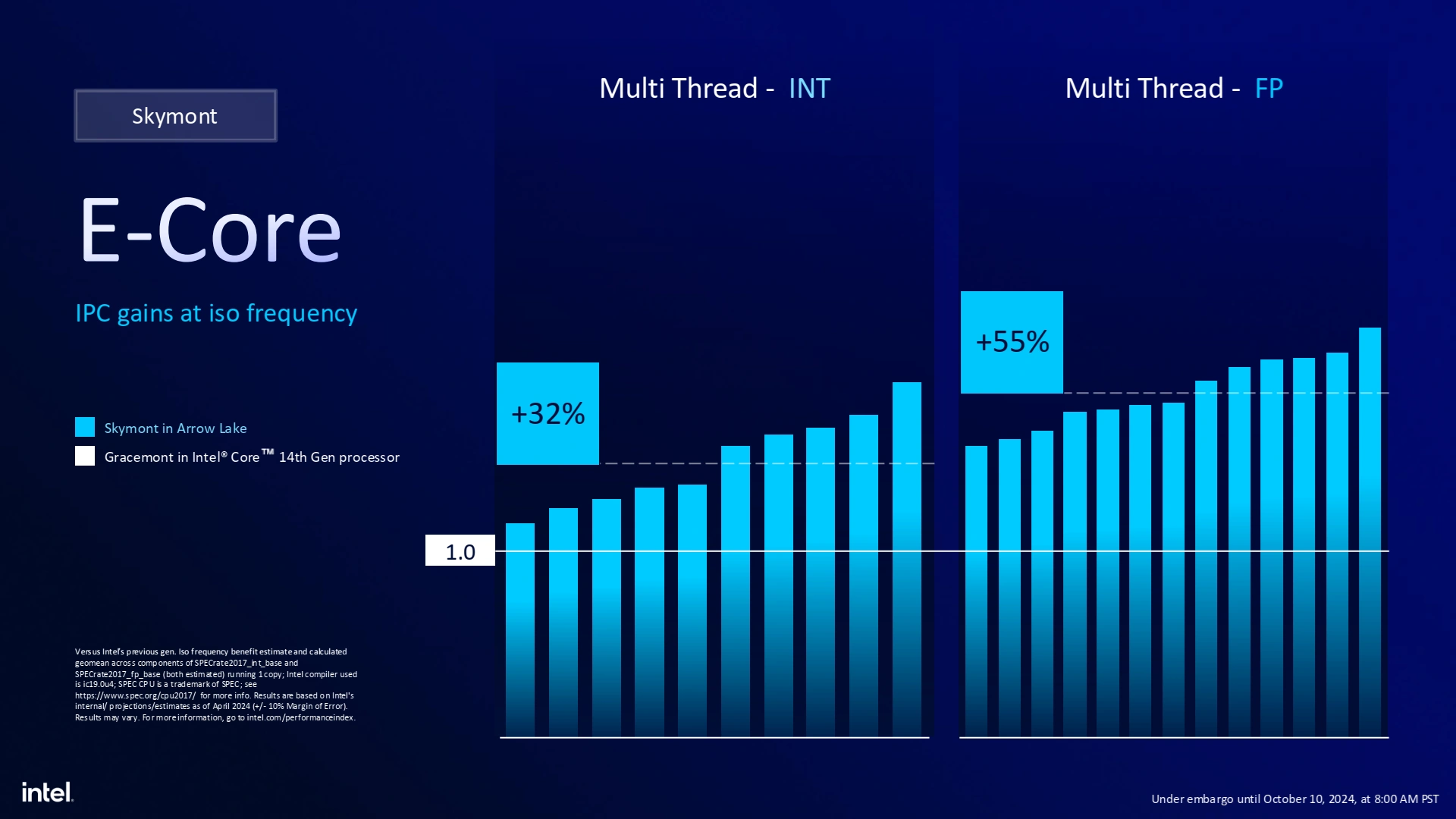

De côté des E-Core — microarchitecture Skymont —, l’histoire est sensiblement différente de Lunar Lake, puisqu’il faut cette fois-ci non pas limiter la consommation de batterie dans les tâches de tous les jours, mais être un accélérateur de performance dans les applications multithreadées, usuellement de productivité. Heureusement, ces deux impératifs se rejoignent dans la conception du cœur, puisqu’ils convergent vers un seul objectif : extraire le maximum de performance dans le minimum de place.

Pas question de rajouter de l’Hyperthreading ici non plus — trop coûteux en surface pour les composants à dupliquer ou étendre —, mais l’intérieur se voit modifié de manière similaire à Lion Cove : le Front-End est en double progression, à la fois sur la prédiction de branchement et le décodage, qui passe à un fonctionnement à trois clusters. Côté Back-End, pas moins de 26 ports d’exécutions sont présents, un nombre plus important que pour les P-Core, non pas pour les surpasser en performance, mais dans le but de simplifier la logique chargée du scheduling des instructions. Ici aussi, de nouvelles unités de chargement-rangements font leur apparition, mais le plus gros changement se situe au niveau des unités AVX2 qui doublent de puissance pour culminer à du débit de 4 instructions 128-bit ou 2 instructions 256-bit par cycle — retrouvez ici notre analyse plus complexe si cela manque de détail ! Enfin, la mémoire se limite à un L1-D de 32 kio et un L2 partagé par cluster de 4 Mio : inutile de trop perdre en surface ici ! Tout comme le coeur performant, Skymont fait l'impasse sur l'AVX-512 (qui aurait pourtant bien performé sur ce type de microarchitecture au front-end encore simpliste) et se contente du VNNI sauce AVX-2 pour le machine learning.

Faire tourner tout cela ensemble

Nous vous le racontions quelques paragraphes au-dessus, une des différences majeures entre Lunar Lake et Arrow Lake se situe dans l’emploi des E-Core. Pour le premier, il s’agit d’un cluster autonome permettant d’exécuter les tâches du quotidien de manière efficiente ; et pour le second, il est question d’un accélérateur d’applications multithreadées. Cela se ressent sur la hiérarchie des caches : sur Arrow Lake, P-Core comme E-Core ont accès à un L3 commun de 36 Mio faible latence, alors que Lunar Lake devait passer par un System Cache plus lointain de 8 Mio pour assurer la cohérence de l’ensemble. L’inconvénient de ce système réside dans l’impossibilité d’éteindre complètement le cluster de P-Core tout entier, un souci qui n’en est pas un sur le segment des PC de bureau.

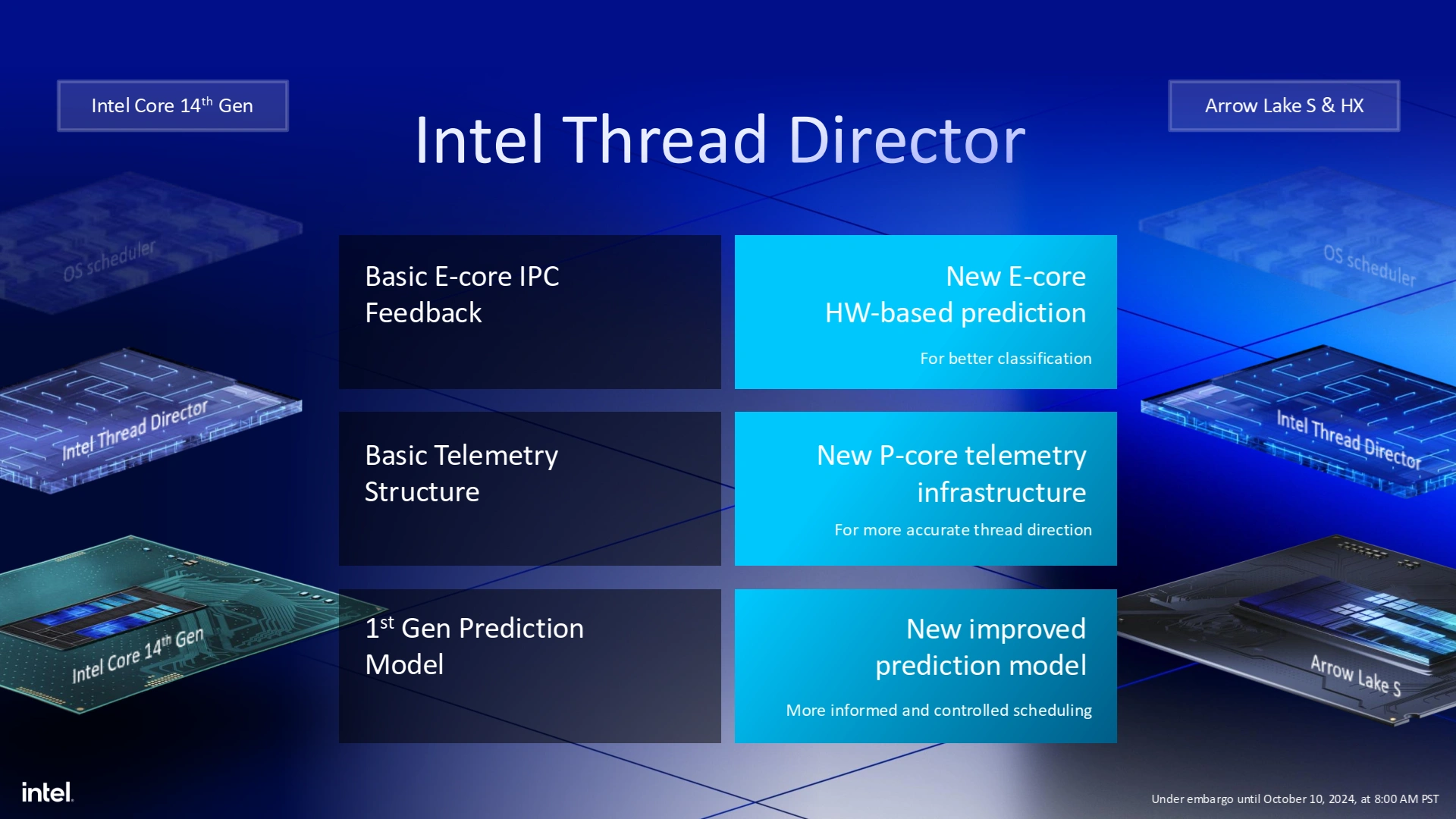

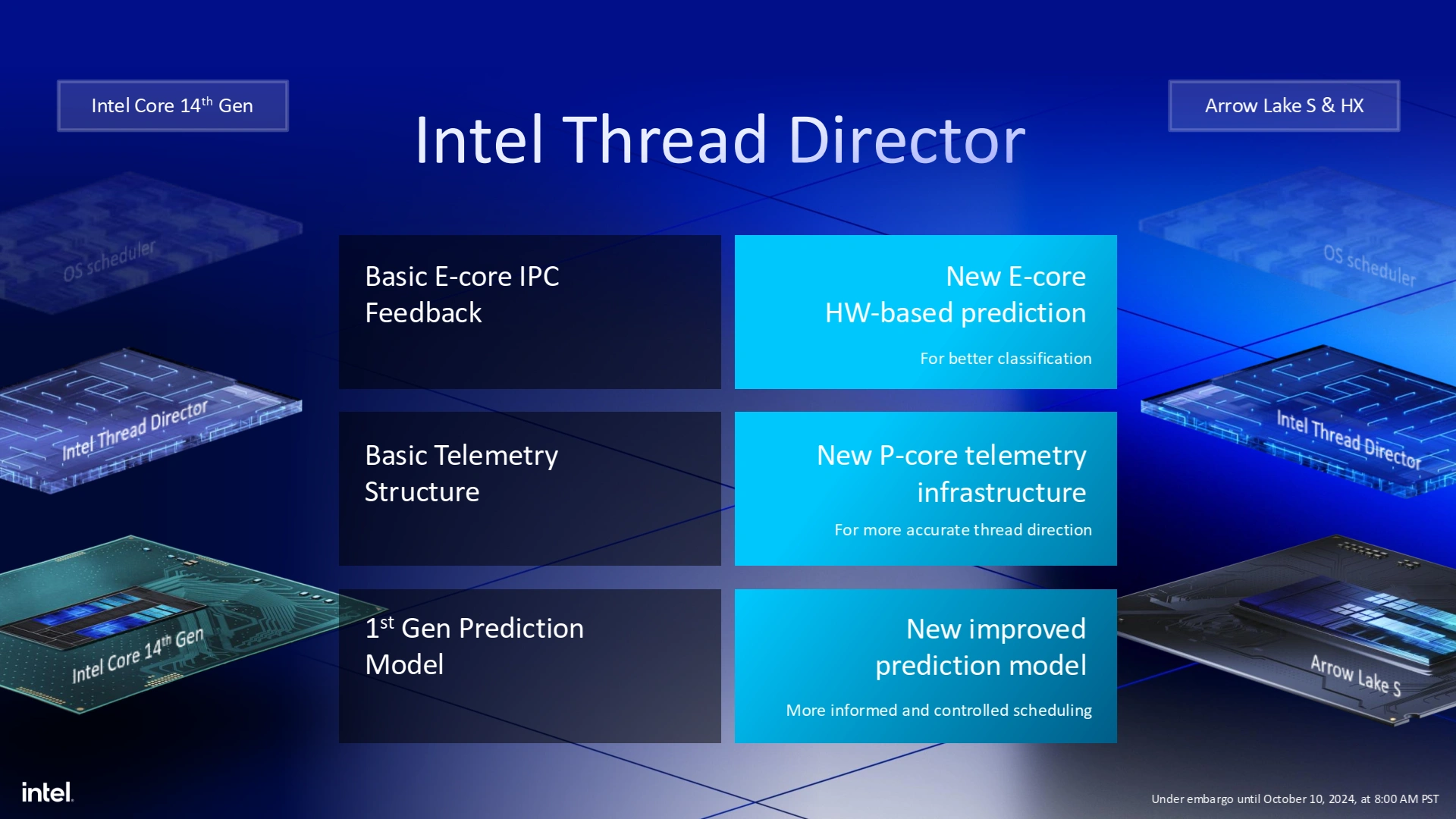

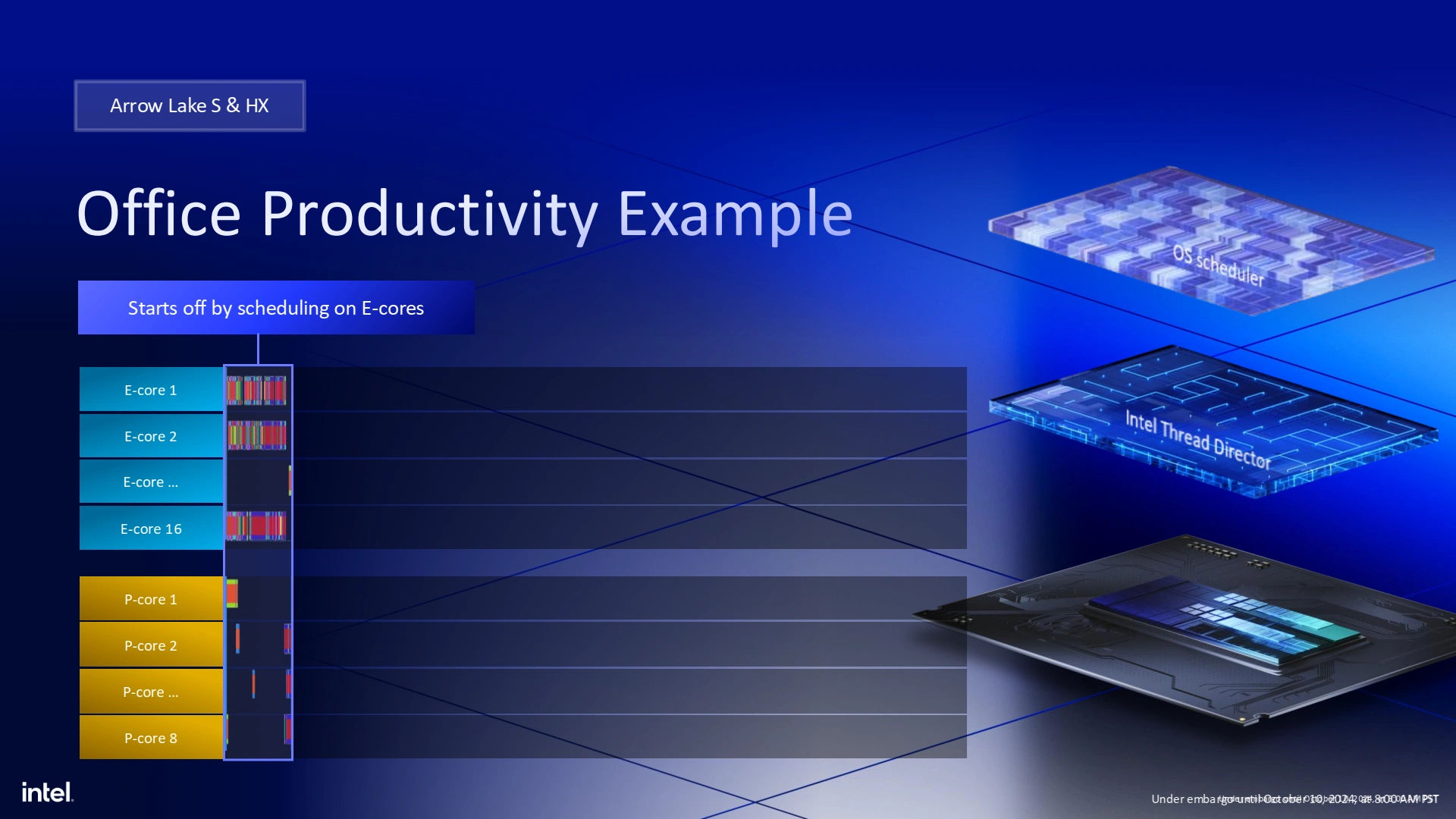

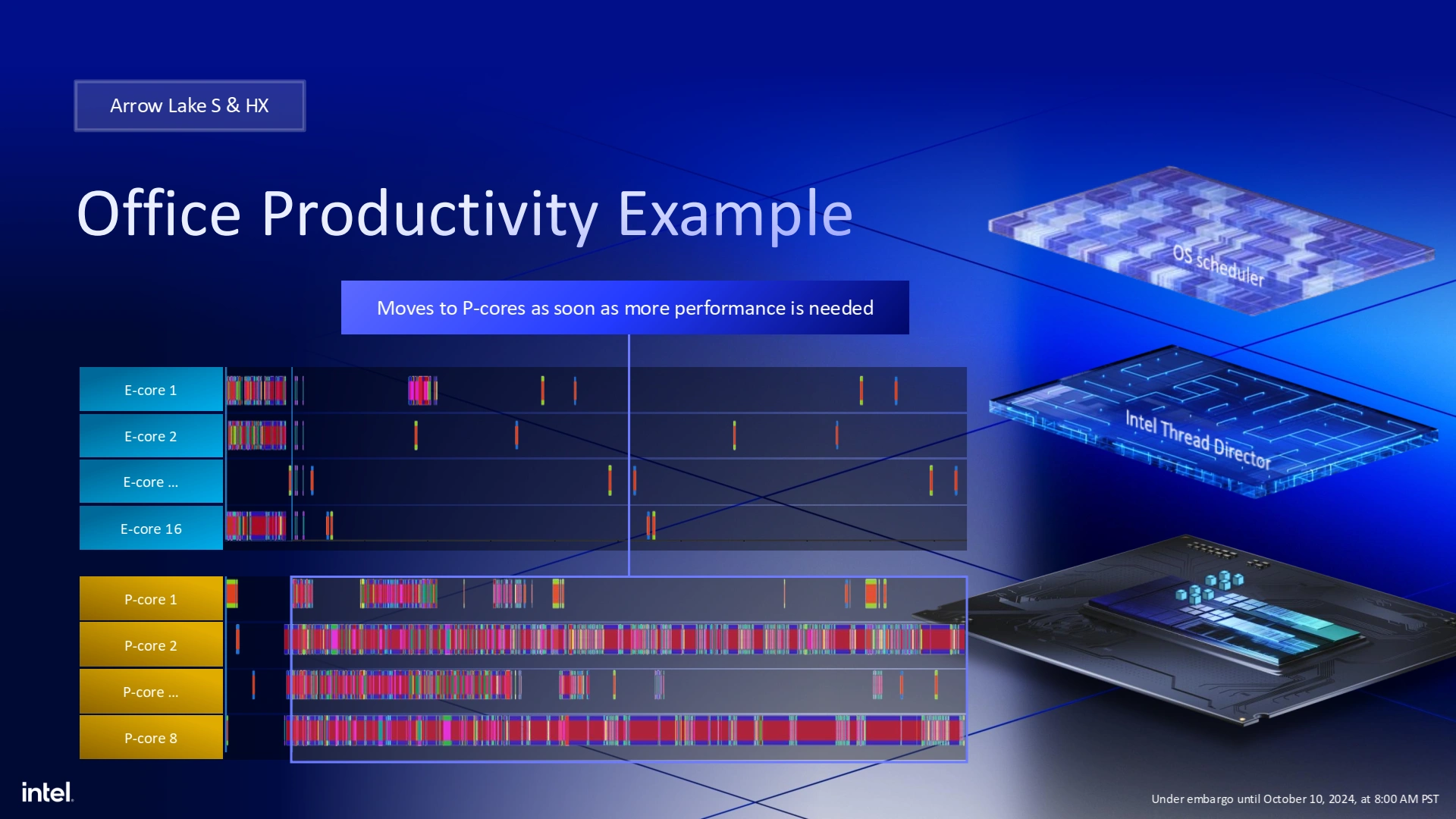

Cependant, qui dit hétérogène dit complexification du scheduler, puisque l’OS doit alors choisir sur lequel des P-Core ou E-Core placer les programmes lancés par l’utilisateur. Cette tâche est assistée en hardware par l’Intel Thread Director (ITD, qui offre des conseils — à Windows de les écouter ou non — sur le positionnement des processus logiciel sur les cœurs matériels.

Déjà présent depuis Alder Lake, l’ITD se voit mis à jour pour utiliser davantage d’informations des P-Core en reposant toujours en majeure partie sur l’IPC, mais également en prenant en compte la constitution du mix d’instructions : les tâches demandeuses de machine learning seront ainsi envoyées en priorité sur les P-Core, alors que la politique standard des applications à faible IPC demeure de rester sur les E-Core, jusqu’à ce que le programme requiert plus de performance. Pour rentrer plus en détail, les applications sont classifiées en 4 catégories qui possèdent chacune leur politique, que nous détaillons plus amplement ici.

Du nouveau pour l’overclocking !

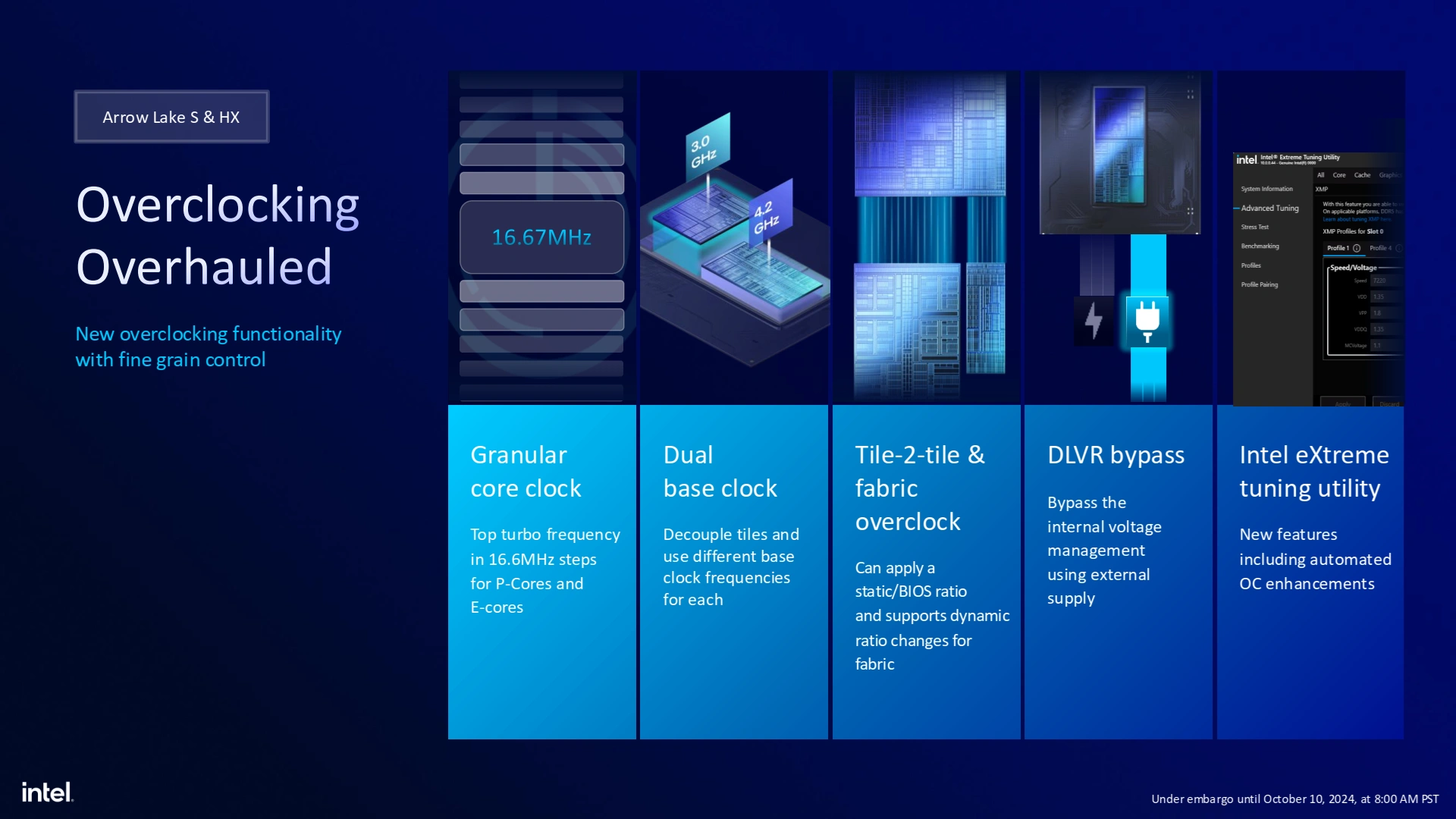

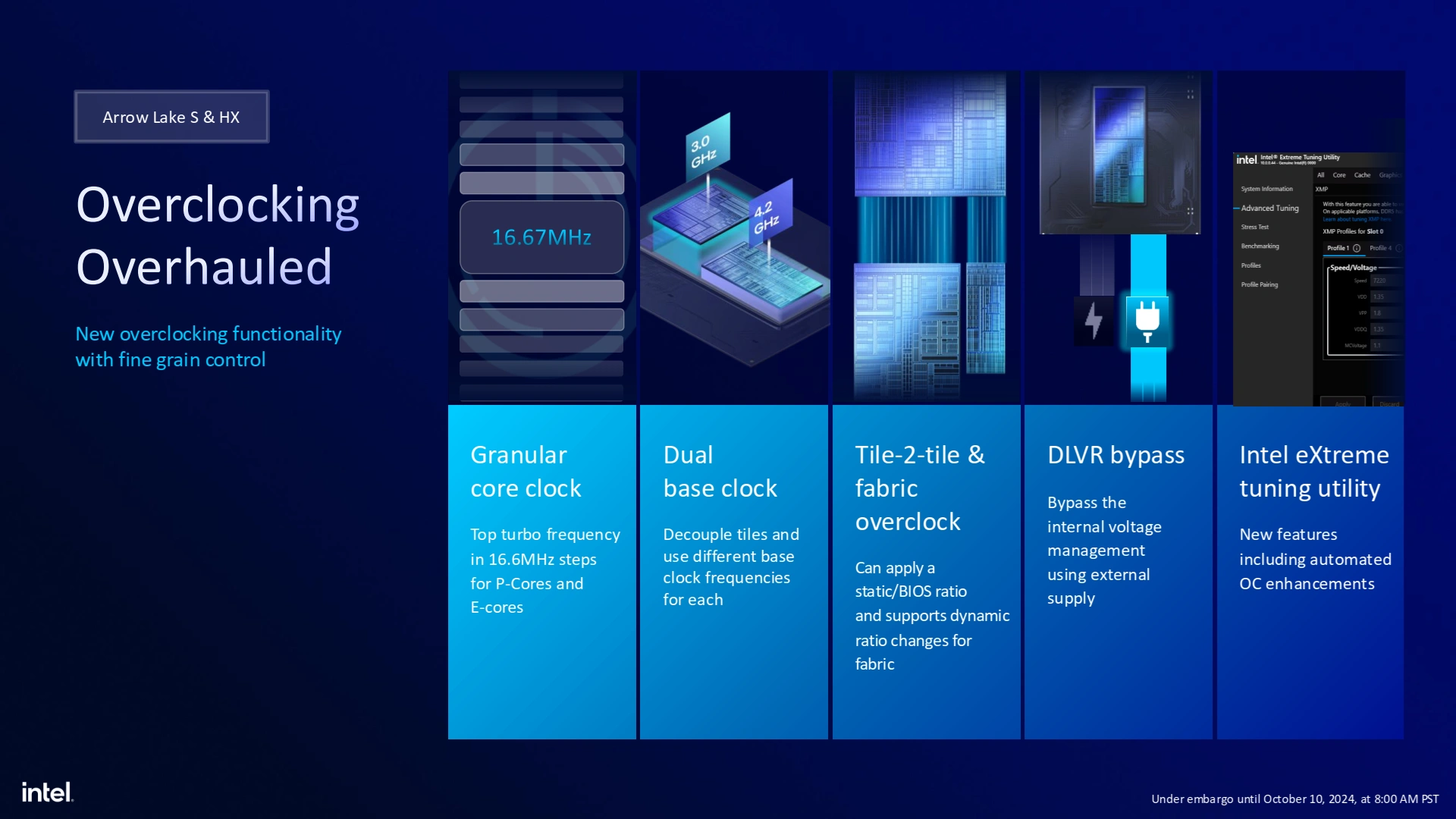

Bien que proposant des gains de plus en plus marginaux auprès des acheteurs, l’overclocking continue d’être un sport pratiqué par les geeks afin de donner un petit coup de boost à une configuration vieillissante. Avec Arrow Lake et l’apparition des tuiles, nous avions de quoi nous ronger les ongles quant à la pérennité de la chose ; mais Intel nous rassure à ce sujet. La montée en fréquence d’Arrow Lake a été un point retravaillé, notamment en offrant une horloge au pas de réglage de 16,67 MHz plus fin, la possibilité de court-circuiter les unités de contrôle des tensions pour les surcadençages extrêmes, ainsi que la possibilité de modifier les ratios des horloges de chaque tuile histoire que votre OC ne se trouve pas instable à cause d 'une tuile de SoC un peu moins prompte à tenir ses fréquences que la tuile CPU principale.

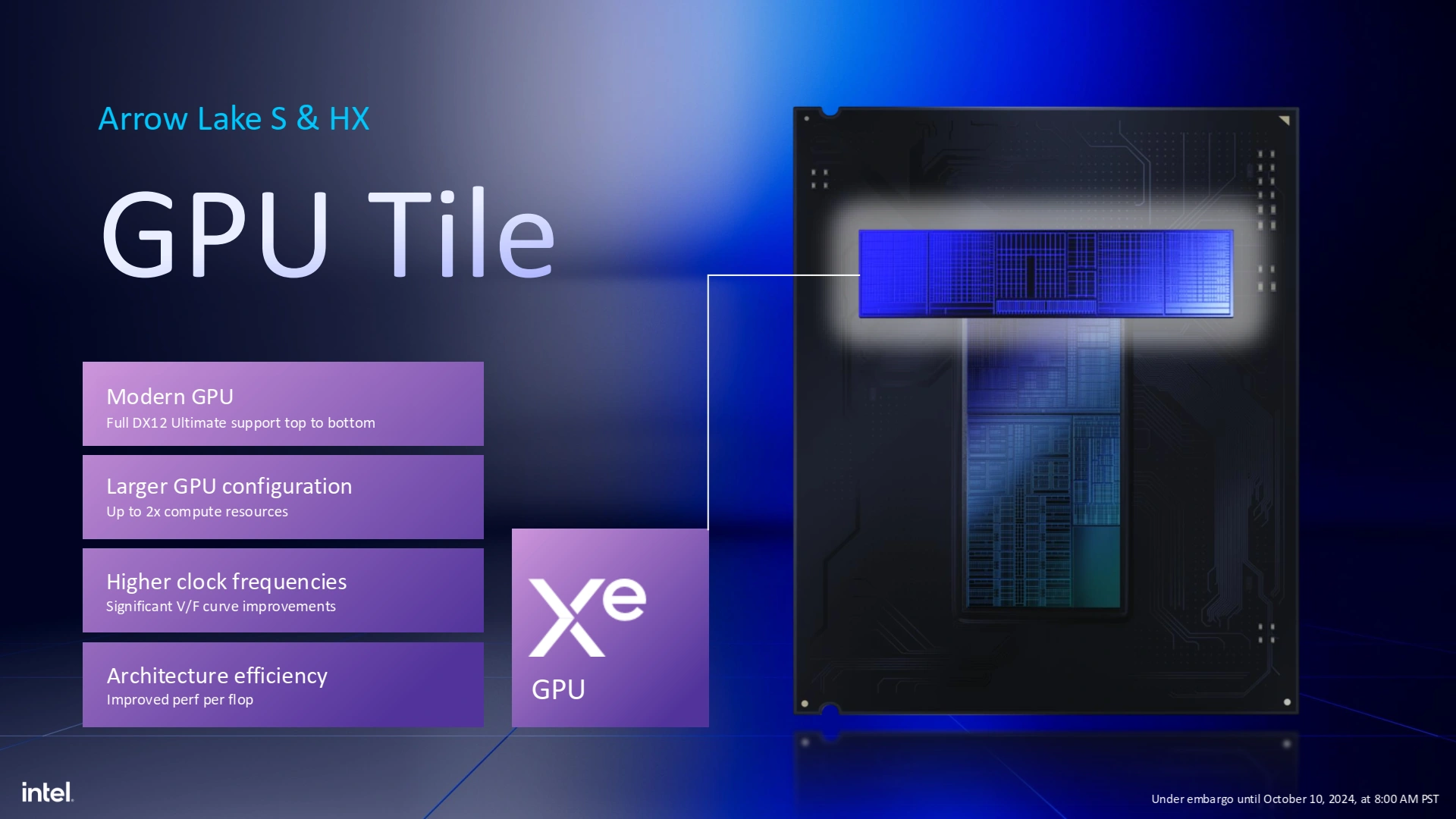

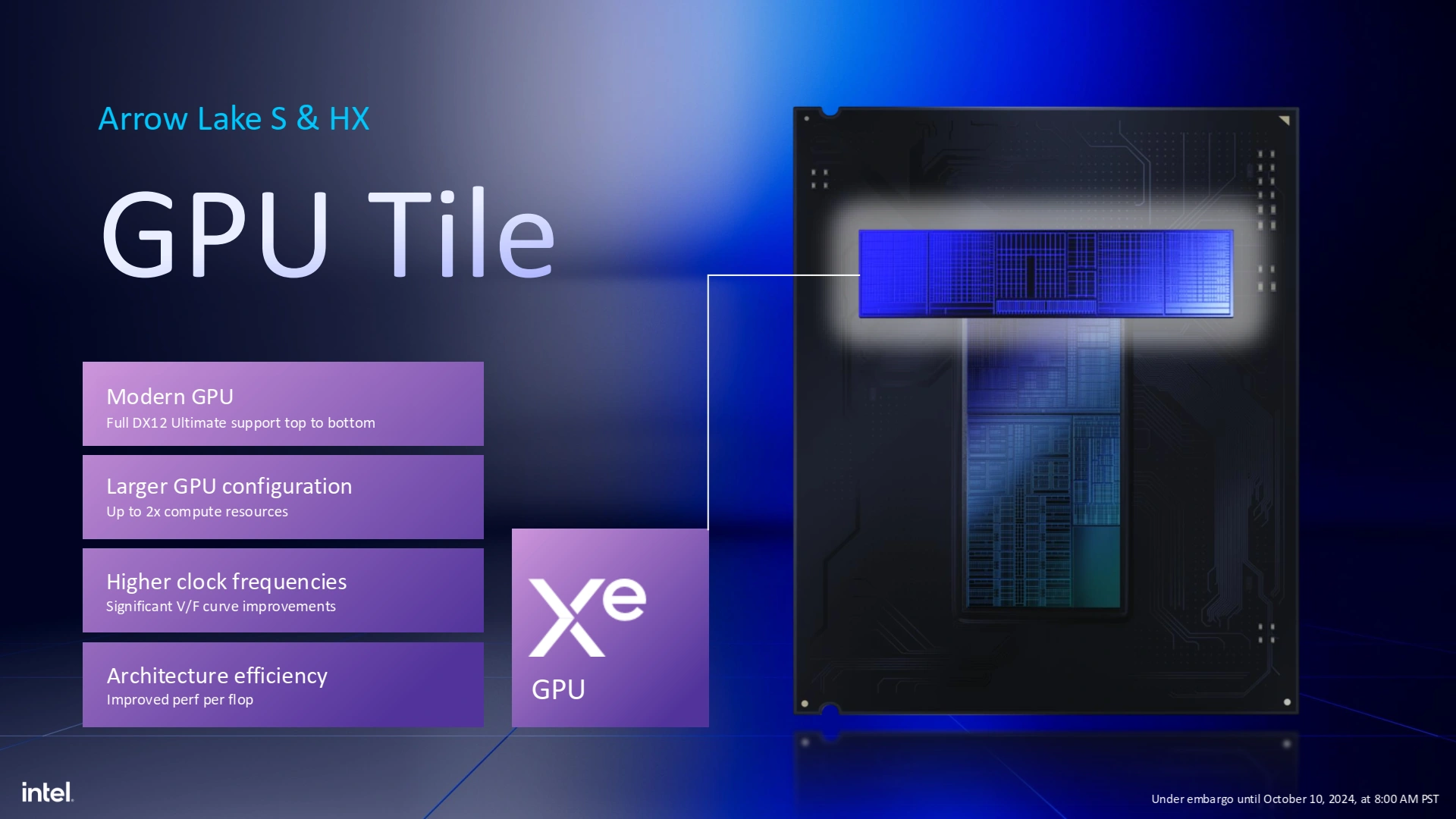

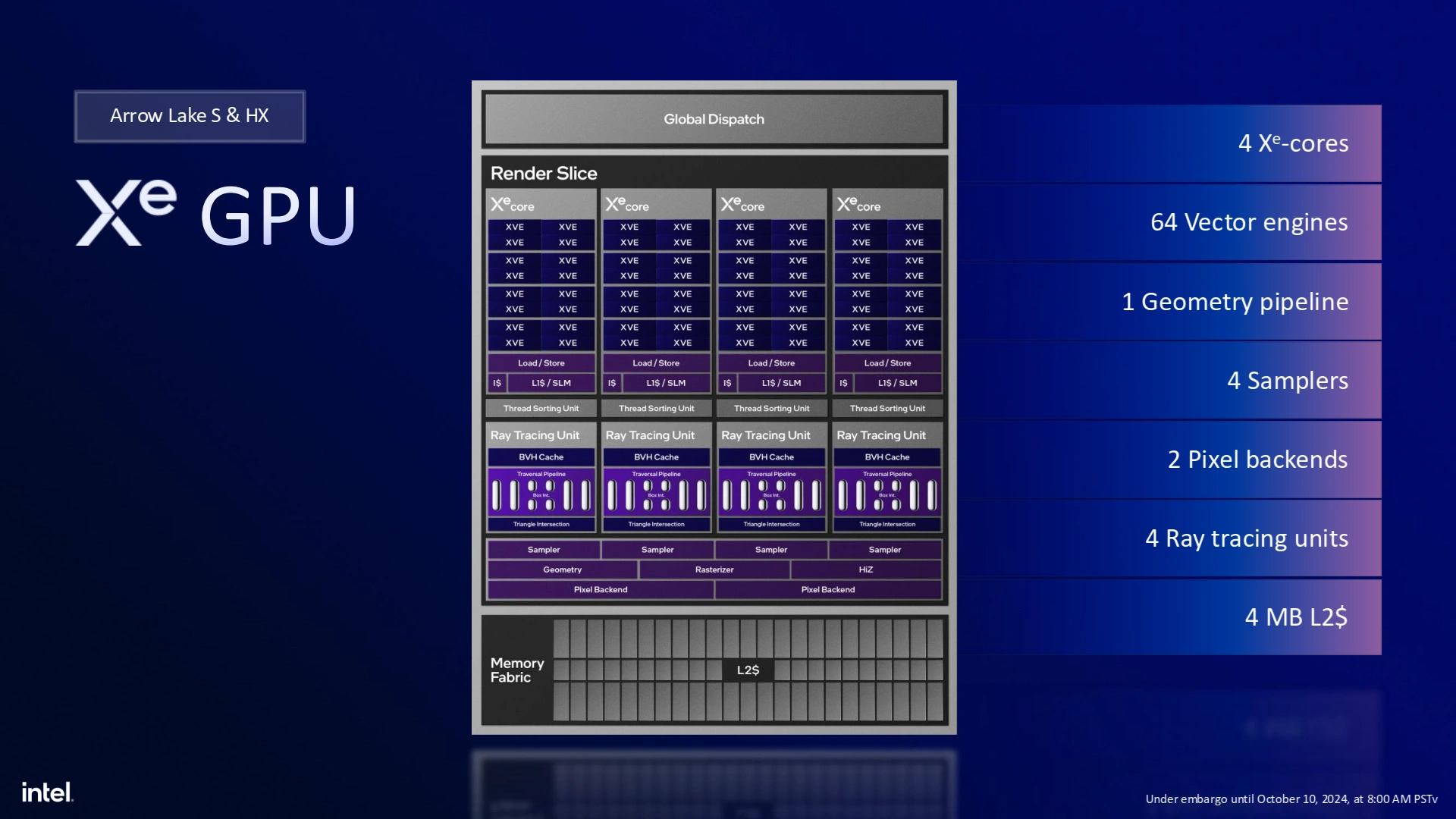

La tuile GPU : Xe, encore et toujours

Malheureusement pour les amateurs de PC compact, les APU ne seront toujours pas de la partie sur Arrow Lake. L’iGPU, heureusement présent, continue sur la lignée des puces graphiques présentes pour de la bureautique, sans plus. En témoigne sa microarchitecture Xe de première génération, qui est toutefois deux fois plus puissante que sa prédécesseure Raptor Lake Refresh (14ème Gen). Il faut dire que cette dernière était une mise à jour mineure de Raptor Lake (13ème génération), elle-même issue d’une optimisation d’Alder Lake pour monter en cadence.

Ainsi, au lieu de 32 EUs de Xe-LP, nous retrouvons 4 Xe Core (le bloc fondateur de Xe HPC/HPG), soit l’équivalent de 64 EUs : voilà d’où provient le gain annoncé d’un facteur 2 en performance — d’autant plus qu’un petit overclock devrait aider à la chose. Bienvenue, la mise à jour l’est certainement, mais le manque d’unités XMX (pourtant bien pratiques pour accélérer la mise à l'échelle par IA d’Intel, XeSS) ne permettant d’utiliser que le DP4a pour les calculs de machine learning, et la comparaison avec les 96 EUs maximum de Raptor Lake-H et les 8 Xe2 Core de seconde génération de Lunar Lake n’est pas à l’avantage du nouveau venu.

La raison à tout cela est évidente : les joueurs ont principalement une carte graphique dédiée (qui plus est lorsque les seuls modèles à la vente sont les Core Ultra les plus haut de gamme), mais nous aurions apprécié avoir une déclinaison pour PC de bureau reprenant la tuile GPU de Lunar Lake et la tuile CPU d’Arrow Lake. Pour une prochaine fois, Intel ?

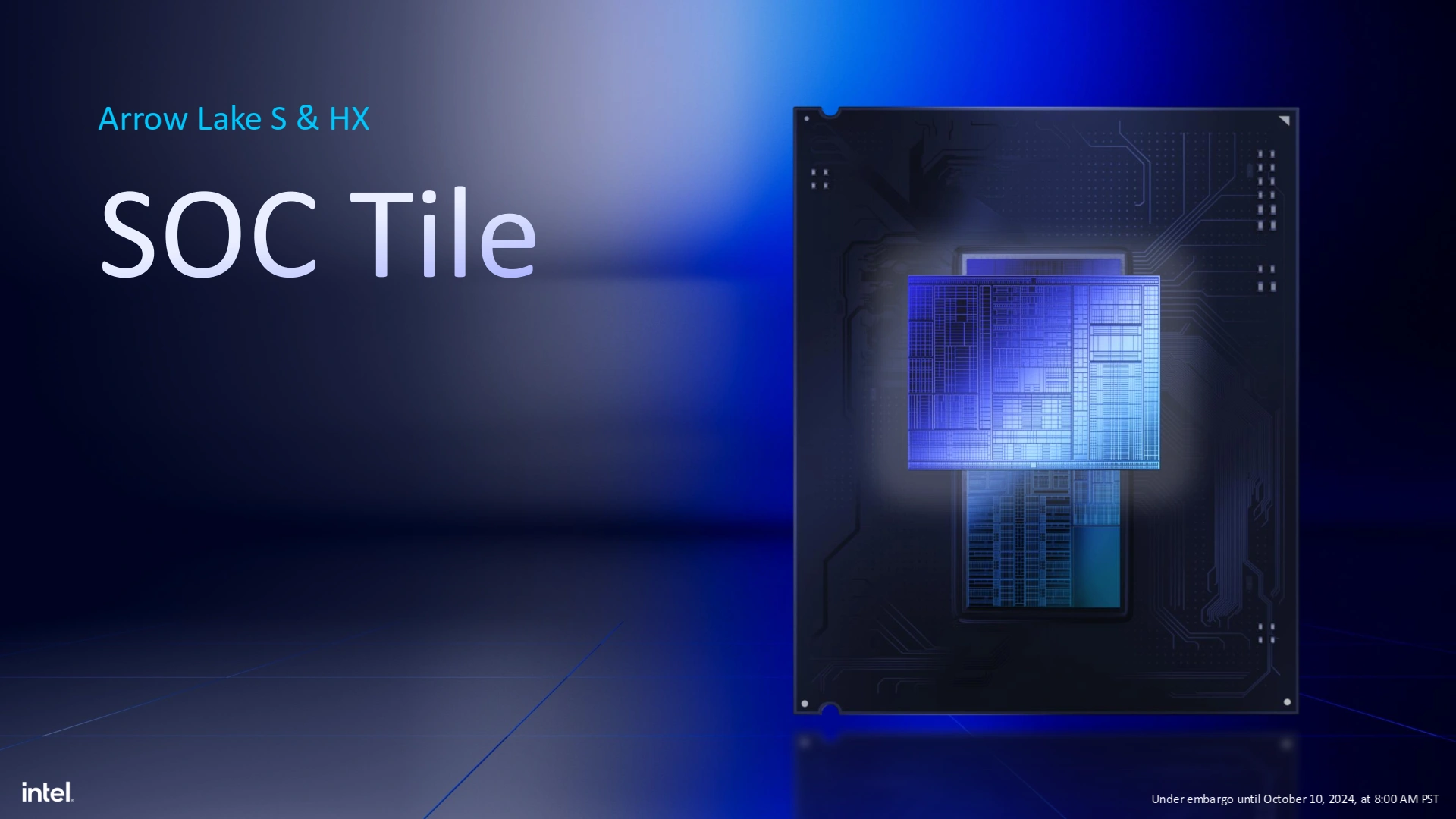

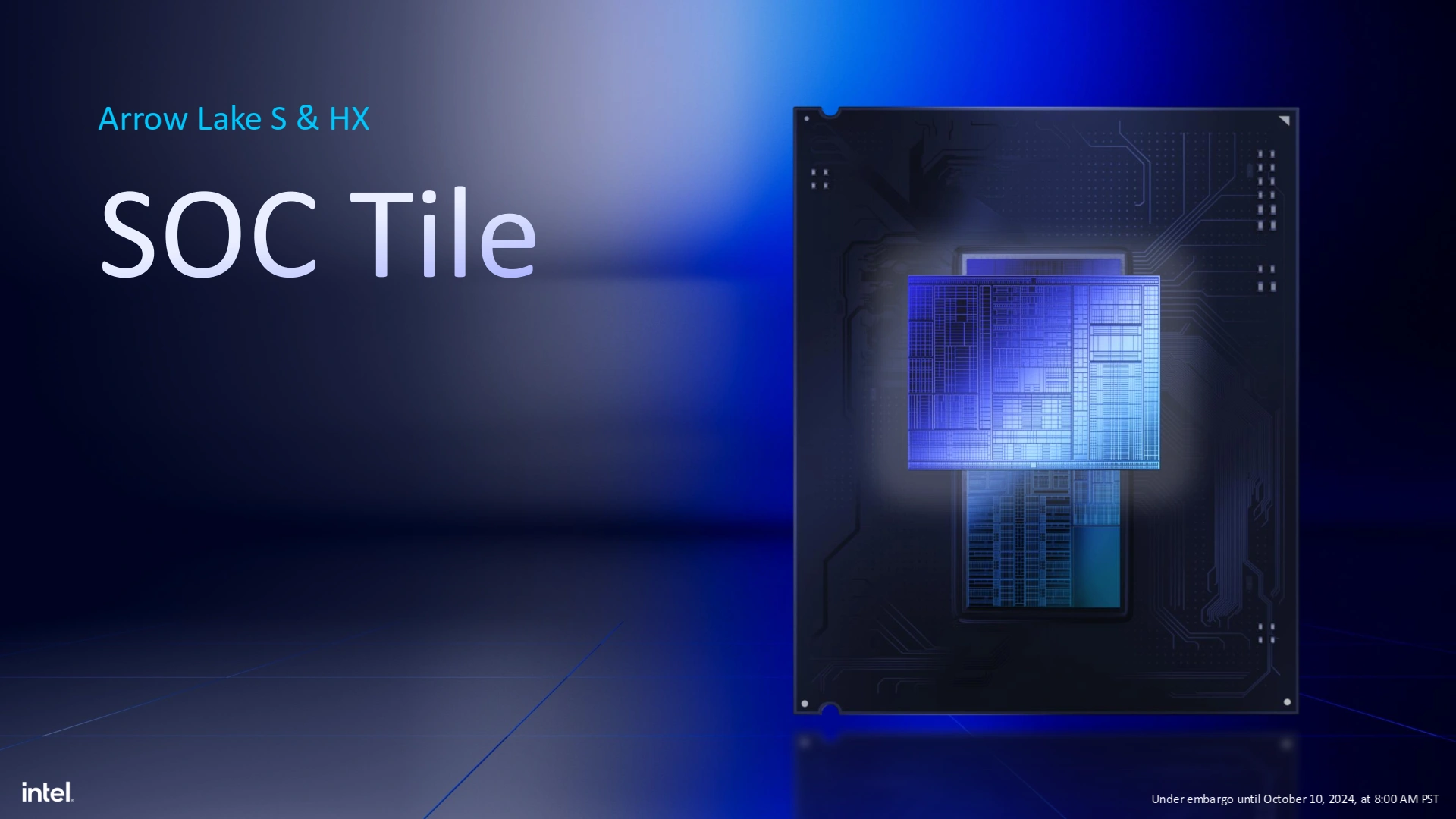

La tuile SoC : Meteor Lake, es-tu là ?

Si les tuiles de CPU et de GPU étaient jusque là inédites, ce n’est pas le cas de la tuile SoC, reprise de Meteor Lake. Intel n’a ici guère le choix vu le coût que représente la conception d’une tuile — nous pourrions même dire qu’Intel se prendrait une… tuile à ce niveau, vu sa santé financière actuelle — mais, fort heureusement, cette dernière possède déjà tous les éléments que nous attendions au niveau des connectiques offertes. Ne cherchez cependant pas de LP E-Core, bien présent dans ladite tuile sur Meteor Lake, puisque ceux-là sont incompatibles du fait de leur microarchitecture Crestmont. En interne, cette tuile intègre dans un procédé de gravure moins coûteux tous les blocs logiques dont la performance ne justifie pas un procédé de gravure avancé : connectiques (PCIe 5.0 / 4.0 / DDR5), encodeurs de média matériels, et (évidemment…) accélérateur de machine learning.

Du Machine Learning : quelle surprise !

Pour la petite histoire, sachez que des discussions houleuses ont eu lieu en interne chez Intel à propos du NPU. Fallait-il reprendre celui de Lunar Lake, quitte à délayer la production de nombreux mois et tirer le prix vers le haut ? Rester sur celui de Meteor et faire une croix sur les 40 TOPS et les Copilot+PC ? De notre point de vue, Intel a fait le bon choix en conservant son accélérateur de ML de troisième génération et un prix contenu. Explications.

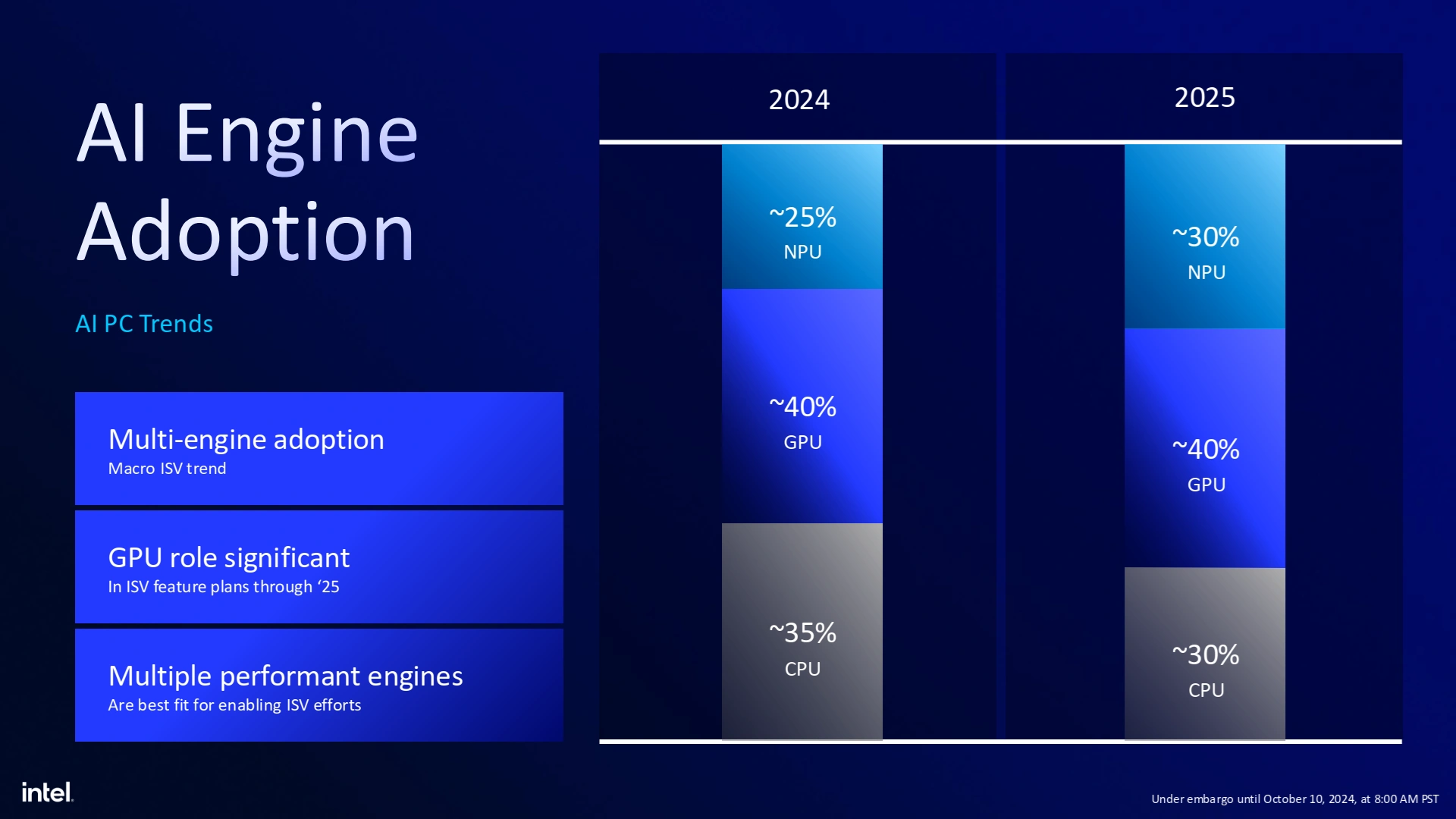

Il parait qu’un NPU sur desktop est utile… en tout cas, selon les projections des bleus.

Avec 13 TOPS, le NPU de Meteor Lake peut sembler à première vue hors de propos, d’autant plus que même le CPU et ses 15 TOPS le surpasse. Cependant, avec l’avènement des « PC IA », l’utilisation du NPU dans l’écosystème logiciel est pressentie pour grimper, si bien que certaines applications (au hasard, pour des effets de floutage d’arrière-plan sur OBS !) pourraient requérir sa présence pour un bon fonctionnement. D’autant plus que le NPU fonctionne indépendamment du CPU, ce qui permet de libérer de précieuses ressources de calcul : dans un monde où l’HyperThreading a été retiré, une telle hétérogénéisation des CPU est assez naturelle.

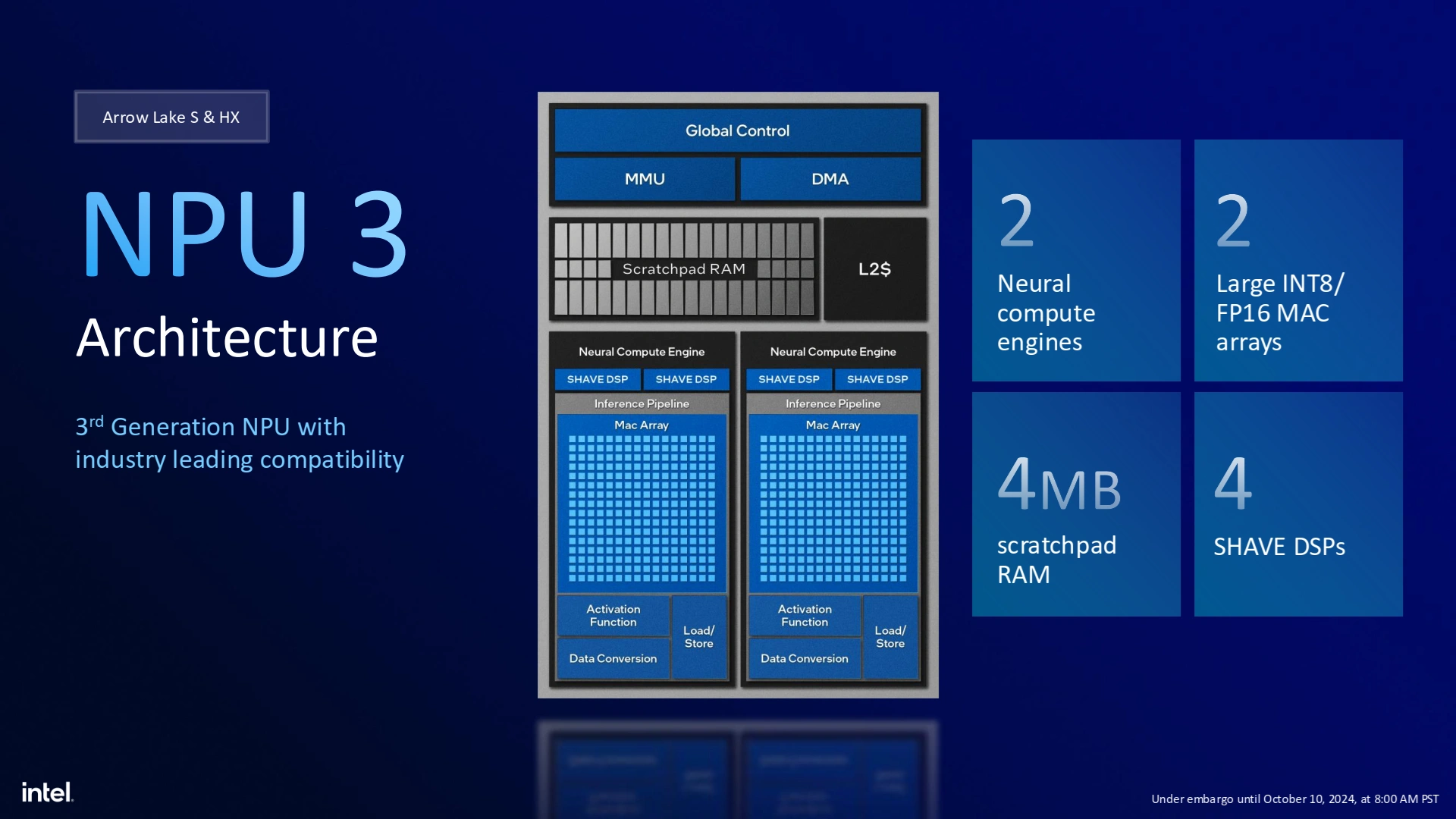

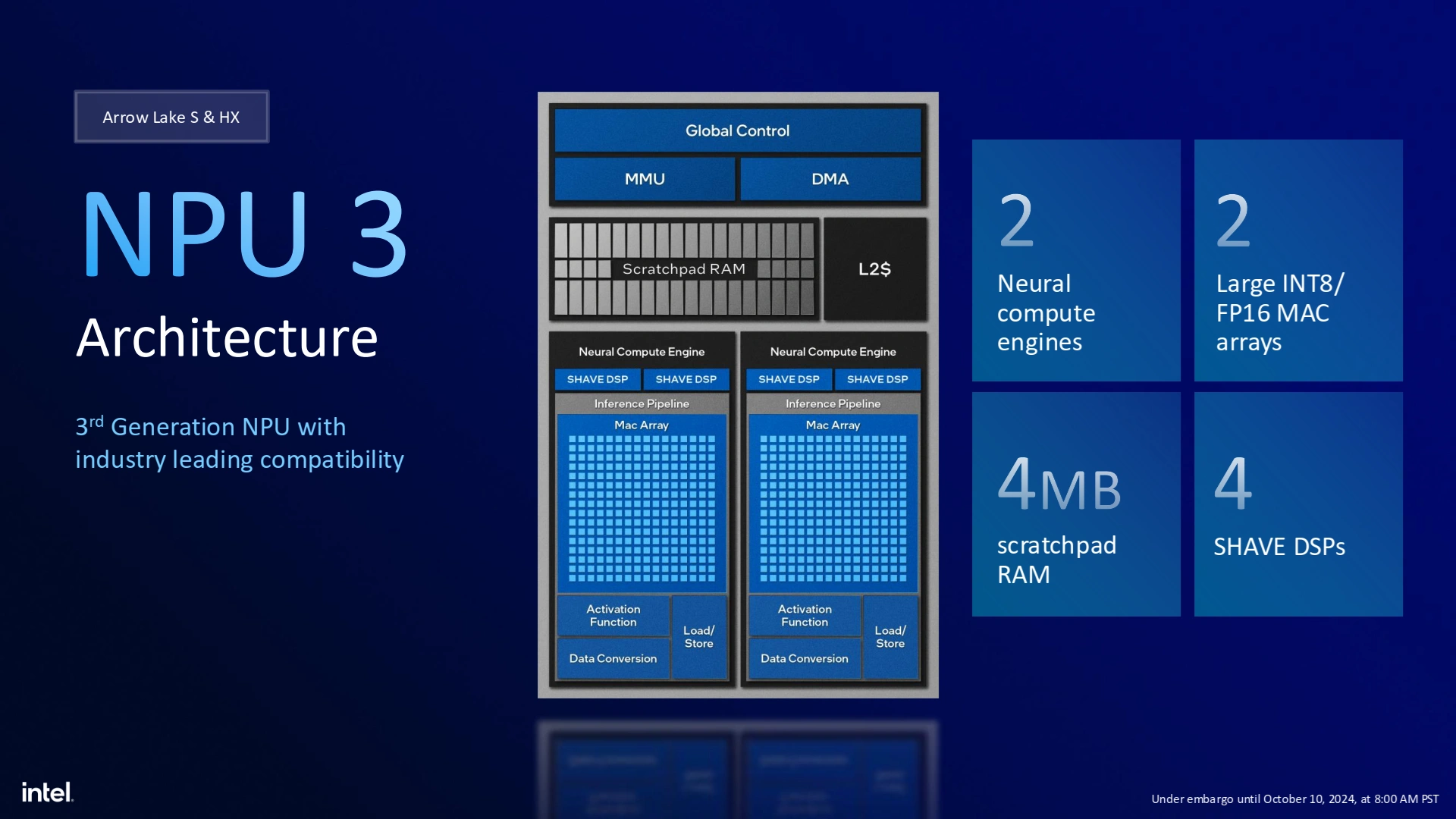

En interne, le NPU de troisième génération est un accélérateur de machine learning, composé de deux unités nommées « Neural Compute Engine ». Très classiques dans leur conception, ces dernières intègrent un tableau d’unités de multiplication-accumulation (le nerf de la guerre IA !) fonctionnant en INT8 ou FP16, deux DSP SHAVE chargés de calculer diverses fonctions customizables afin d’apporter un peu de généralité à l’accélérateur, et des modules classiques d’accès à la mémoire et de conversion de données. Avec 4 Mio de cache configurable localement, le NPU est taillé sur mesure pour manger de l’IA de manière efficace, c’est-à-dire sans aller tailler dans l’enveloppe thermique du CPU et du GPU. Et c’est d'autant mieux : sur un PC de bureau, c’est tout ce que nous lui demandons !

Des évolutions côté média et encodeurs matériels

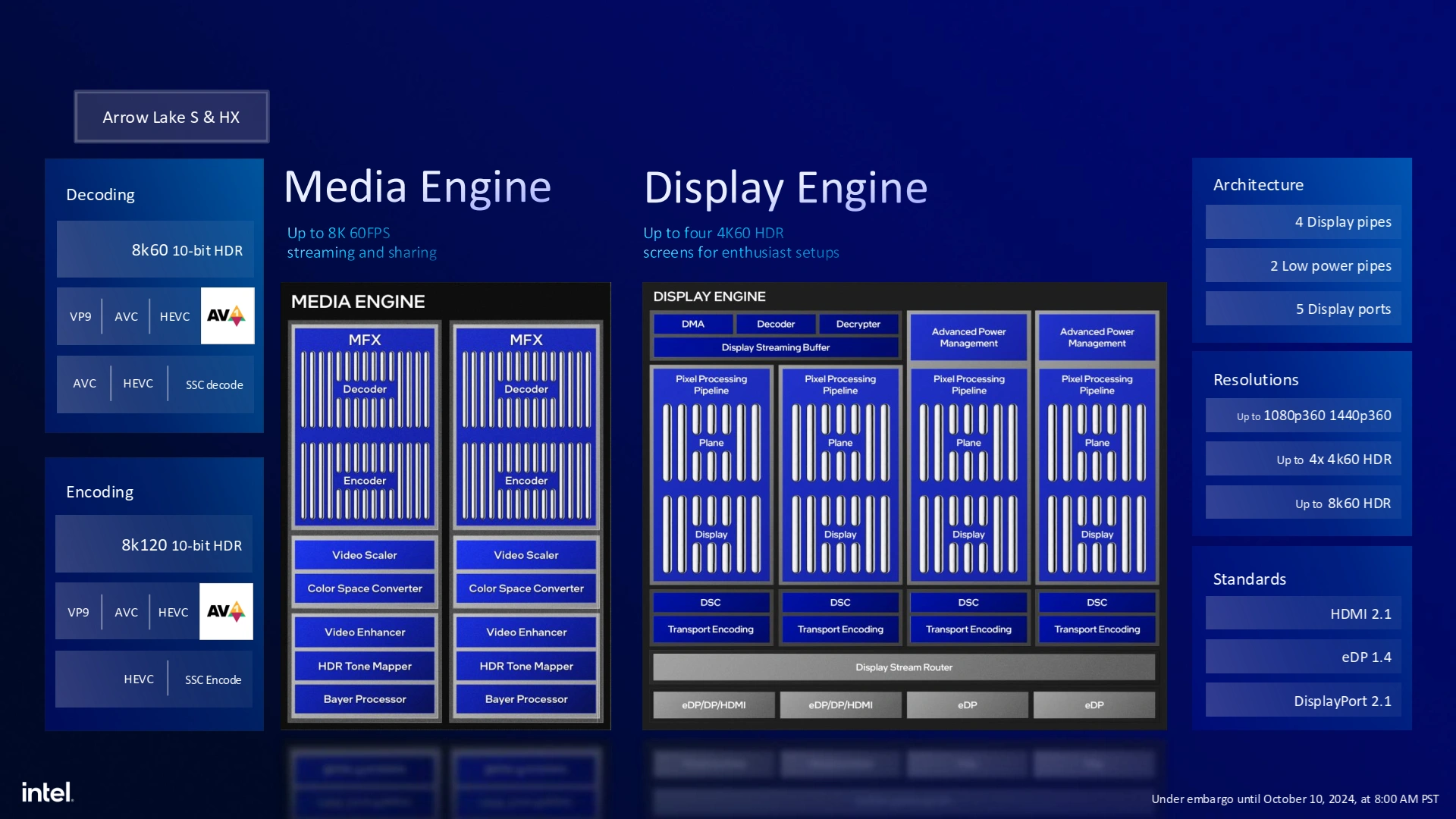

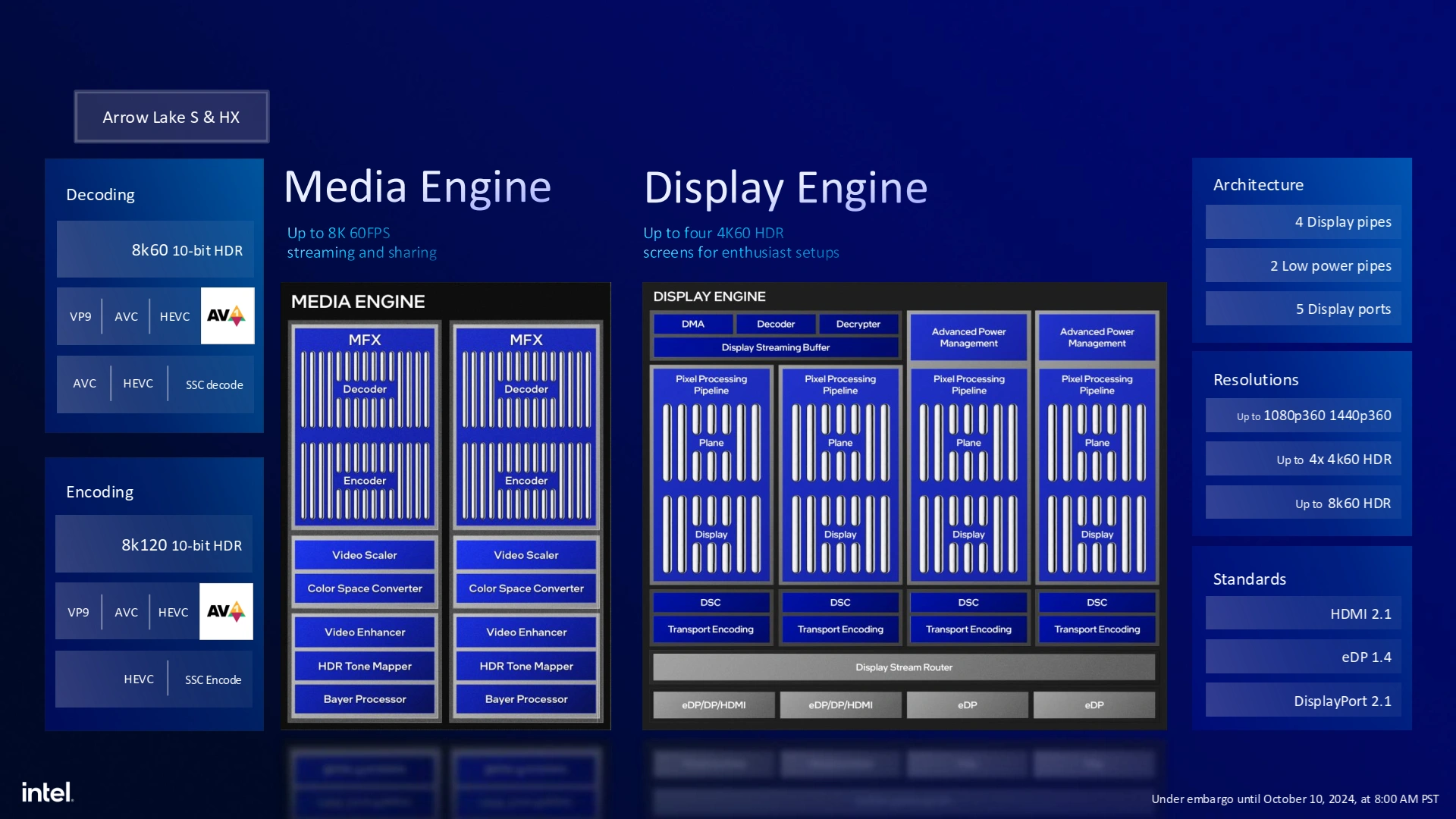

Au sein de la tuile SoC se trouvent également les Media Engine et Display Engine, des unités spécialisées pour l’encodage vidéo pour les premiers cités — à la manière de ce que NVDIA propose avec NVENC —, et le contrôle de/des écrans pour le second.

Du côté de l’encodage, Intel se met à niveau en intégrant toute la salade de codecs habituelle de la firme : VP9, AVC, HEVC, mais surtout AV1, la dernière avancée en matière de compression vidéo. Les bleus communiquent sur une prise en charge de la 8k à 120 FPS pour l’encodage — quatre pipelines étant disponibles sur la puce —, et la 8k 60 Hz pour le décodage via deux pipelines de décodage : voilà ce qui s’appelle être future-proof ! Ainsi, il sera possible de brancher jusqu’à 4 écrans 4K 60 Hz sur Arrow Lake sans avoir recours à un GPU externe, et ce en HDMI 2.1, en eDP 1.4 ou en DP 2.1. Dans la pratique, rares seront les cartes mères à proposer cela — quoique, avec le DP alt mode de l’USB-C, rien n’est impossible — mais la chose sera fortement appréciée des utilisateurs de machines portables une fois Arrow Lake-H sur les étals, c’est-à-dire en 2025.

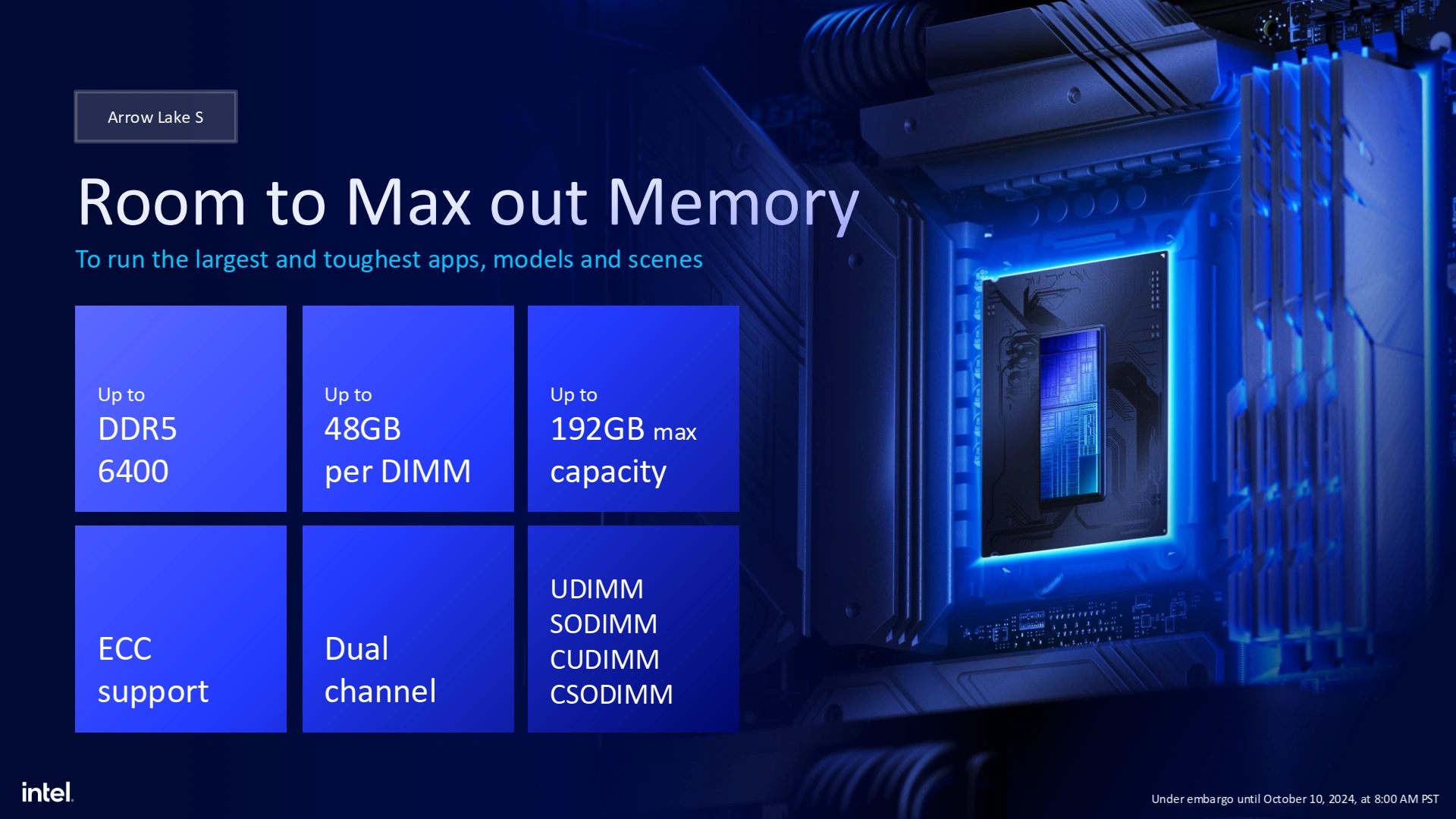

Enfin, les entrées/sorties ne seraient pas complètes sans la DRAM. En 2024, la DDR5 est de mise, avec un maximum de 192 Gio, le support de l’ECC (bien que cela dépendra du fabricant, et l’on nous a bien fait comprendre que cela serait davantage réservé à des déclinaisons pour les professionnels), mais surtout de la CUDIMM, c’est-à-dire de barrettes intégrant leur propre pilote d’horloge afin de maximiser la stabilité sur les hautes fréquences. Certes, Intel communique sur un support de la DDR5-6400 maximum, mais il est monnaie courante d’overclocker ce dernier une fois les barrettes compatibles disponibles dans le commerce.

Une petite tuile d’IO supplémentaire

Pour finir, Arrow Lake ne pouvait pas se présenter au grand public sans apporter une mise à niveau des connexions, que la tuile SoC n’est pas en capacité de fournir au vu de sa filiation. Ainsi, la tuile d’IO — un beau copié-collé de la tuile utilisée pour Meteor Lake-H — vient complémenter la connectique de ces Core Ultra 200S en rajoutant le support de 2 interfaces Thunderbolt 4, ainsi que 8 lignes PCIe 5.0 (et donc 12 sur la tuile SoC, en croisant les doigts pour que cela ne pose pas de soucis pour les GPU en x16) supplémentaires pour culminer à 20 lignes de ce type, pour un total de pas moins de 48 lignes PCIe 4.0 et PCIe 5.0 en incluant celles provenant du chipset.

Maintenant que vous savez tout ou presque sur l’architecture Arrow Lake, voyons les processeurs qui utilisent cette dernière, direction la page suivante !

Très bon test comme toujours

Petite question pas d oc ? ( curieux de voir d'où vient le choix de 5.7 ghz )

Pour le test ram pourquoi "que" 8200 mhz ? Il faut passer en gear 4 ensuite ?

Possible de savoir combien il consomme en jeux ?

Quel est le prix des nouveaux kit cudimm ?

Merci d'avance

Pas le temps de faire plus avec les soucis que j'ai rencontrés, on verra ce que je peux ajouter par la suite.

Ok je comprends

Je trouve bizarre qu'avec architecture et gravure différente amd et intel se retrouve avec la même fréquence max

Quand Intel avait la maîtrise du procédé et un design monolithique, aller monter en conso pour gagner en fréquence était plus facile. Avec TSMC, les contraintes doivent être différentes (et c'est souvent qu'une nouvelle finesse de gravure monte moins haut que l'ancienne), et comme l'IPC n'est pas toujours exploitable dans toutes les tâches, on observe sur certains bench une stagnation.

Cedt certainement un mélange de tout ça

Excellent test : en plus de prendre le temps de décrire chaque strate qui compose le CPU, il couvre tout le spectre des métriques qu'on attend, et les remarques sont de qualité.

Déçu par le CPU of course, mais ça n'entache en rien la qualité du test :)

🙏 Il y a encore quelques fautes en cours de correction, on a fini un peu à l'arrache avec Nicolas.

Miam la lecture ! Merci Riton, Nico & Co pour ce test. ❤️

Top le test merci

Le 245 est vraiment intéressant, j'ai pas de regret sur mon choix d'une plate-forme AMD en AM5 après plus de 20 ans chez Intel , mais si je devais faire une machine aujourd'hui il y aurait des doutes sur mon choix! Le tarifs aurait été seul juge au final.

Attention le socket 1851 n'est pas évolutif une seul gen dessus apparemment ça compte aussi

Alors ce n'est pas un facteur déterminant pour moi. Mais je peux comprendre que ça l'ai pour certain.

A partir de quel fréquence il faut passer en gear 4 pour la ram sur cette gen ?

J'attendais mieux en consommation mais il semble qu’Intel ai encore du mal avec le fait de ne pas dépasser les 200w 😬

Les performances elles seront a revoir après les indispensables optimisations logicielles a venir, la latence de la ram parait extrêmement haute et doit bien plomber les scores en jeux.

Mais c'est au moins un pas dans la bonne direction 😄

Merci pour ce test d'excellente facture que je n'ai pas encore fini de parcourir. Intel va dans le bon sens, c'est bon pour la concurrence et donc pour l'acheteur final. Je pense que la prochaine mouture corrigera les "erreurs de jeunesse" de cette nouvelle archi.

Je viens de vérifier des info sur la cudimm elle sert à quoi en fait ?

On trouve des kit "normaux" à 8000-8400 mbps

En cudimm ca démarre vers 8000 on a plus haut mais à quel prix ? La puce en plus faudra la payer

Les perfs aussi au bout d'un moment il va falloir activer le mode gear 4 et comme la latence pose déjà problème ça sera pire ensuite

Donc pour cette gen je doute de son utilité