Une plateforme pour décrocher la Lune !

Depuis l’Intel Architecture Day 2018, le géant bleu a fait de la transparence technique un pilier de sa communication médiatique. Détails des progrès (et des retards) en matière de finesse de gravure, présentations détaillées des microarchitectures, tables rondes sur les directions futures de la firme en matière de design de puces : un cocktail chargé de noyer la presse d’informations et, ainsi, rester sur le devant de la scène. Et on en redemande ! Ainsi, dans l’immédiate précédence du Computex, Hardware & Co a été convié à Taiwan pour apprendre en détail les secrets de la de la conception architecturale de Lunar Lake… sans mention directe de performance, le SoC ne se retrouvant pas actuellement dans des produits accessibles à l’achat — il faudra attendre plus tard ce trimestre pour cela.

Pour autant, Lunar Lake n’est pas dénué de modifications croustillantes, bien au contraire : absence totale d’Hyper-Threading, arrivée d’un NPU massif, intégration Foveros de dies manufacturés en quasi-intégralité par TSMC, un renouveau architectural à la fois côté E-Core et P-Core mais, surtout, un focus sur l’efficacité énergétique chassant sur le terrain des processeurs Arm et cherchant à prouver que, définitivement, le jeu d’instruction n’a rien à voir avec la consommation d’un CPU. Bref, une puce difficile à imaginer il y a encore cinq années. En quelles décisions de design se transcrit cette philosophie ? C’est ce que nous allons voir tout au long de ce dossier… sans fréquences ni benchmarks, alors que c’est bien sur ce terrain-là que la bataille va se jouer une fois les belligérants déployés. En avant ? Marche !

De quoi qu’on cause ?

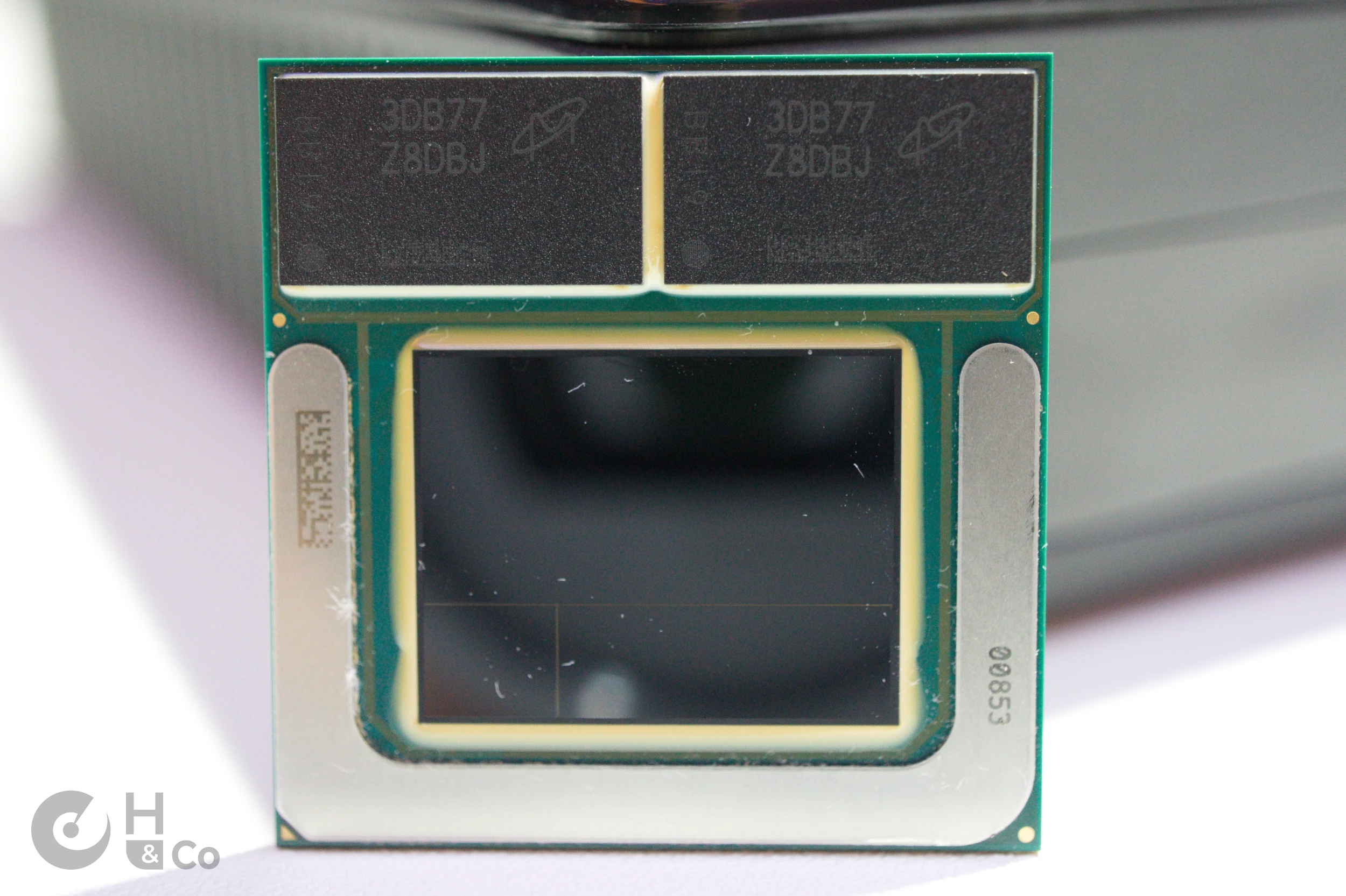

Si, il y a quelques années encore, un processeur comprenait des cœurs d’architecture identiques et, souvent, un iGPU, les besoins de consommation restreinte du segment des ultraportables ont poussé à l’intégration commune de ces composants dans un même package, c’est-à-dire un unique composant à souder sur les cartes mères des produits finaux. Avec Lunar Lake, deux étapes supplémentaires ont été franchies avec l’intégration de la RAM sur ce package, réduisant ainsi la taille minimum des PCB des machines qui en font usage, et l’intégration d’un NPU dont la taille est comparable à celle du GPU. Au niveau des caractéristiques et des divers nom de code que vous retrouverez tout au long de cet article, nous avons à faire à une puce composée de 4 morceaux de silicium :

- Une tile de calcul, qui intègre tous les modules listés ci-après ainsi que le contrôleur LPDDR5, gravée en N3B de chez TSMC

- Une tile gérant les entrées/sorties contrôlant également différents bus (Wi-Fi 7.0, Bluetooth 5.4, PCIe Gen5 / Gen4, Thunderbolt 4), gravée en N6 de chez TSMC

- Une tile d’équilibrage non gravée pour éviter une faiblesse structurelle

- Une tile en P1227.1 jouant le rôle d’interposer (aucun transistor n’y est intégré, il s’agit en fait des metal layers de l’Intel 4 en version optimisée pour le SoC/communications), située en dessous de tout ce beau monde grâce à Foveros sauce 25 µm (contre 36 sur Meteor Lake).

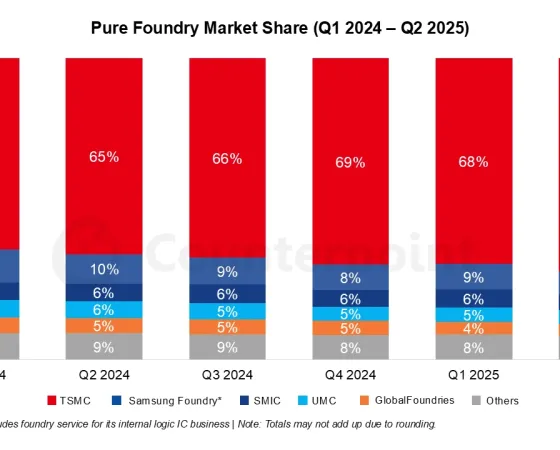

Oui, vous avez bien lu, les parties actives du Lunar Lake ne sont pas manufacturées par les usines d’Intel — bien que le packaging et le die passif le soient. De quoi voir une évolution positive de la stratégie des bleus dans le recourt à un prestataire externe pour la lithographie — annoncée par l’axe « expand » de la stratégie IDM 2.0 ? Le choix est en tout cas rationnel, et permet (enfin) de proposer au consommateur une technologie adaptée aux besoins en matière de mobilité (c'est-à-dire optimisée pour la basse consommation) : toute l’idée du découplage de la conception et de la fabrication est justement d’avoir recourt au procédé adapté à la plateforme, pour ensuite y porter les IP (block logiques constituant un SoC). Et, si la mise au point des lithographies d’Intel est encore approximative, la firme a clairement de l’expertise architecturale à revendre : vous le verrez dans les pages suivantes !

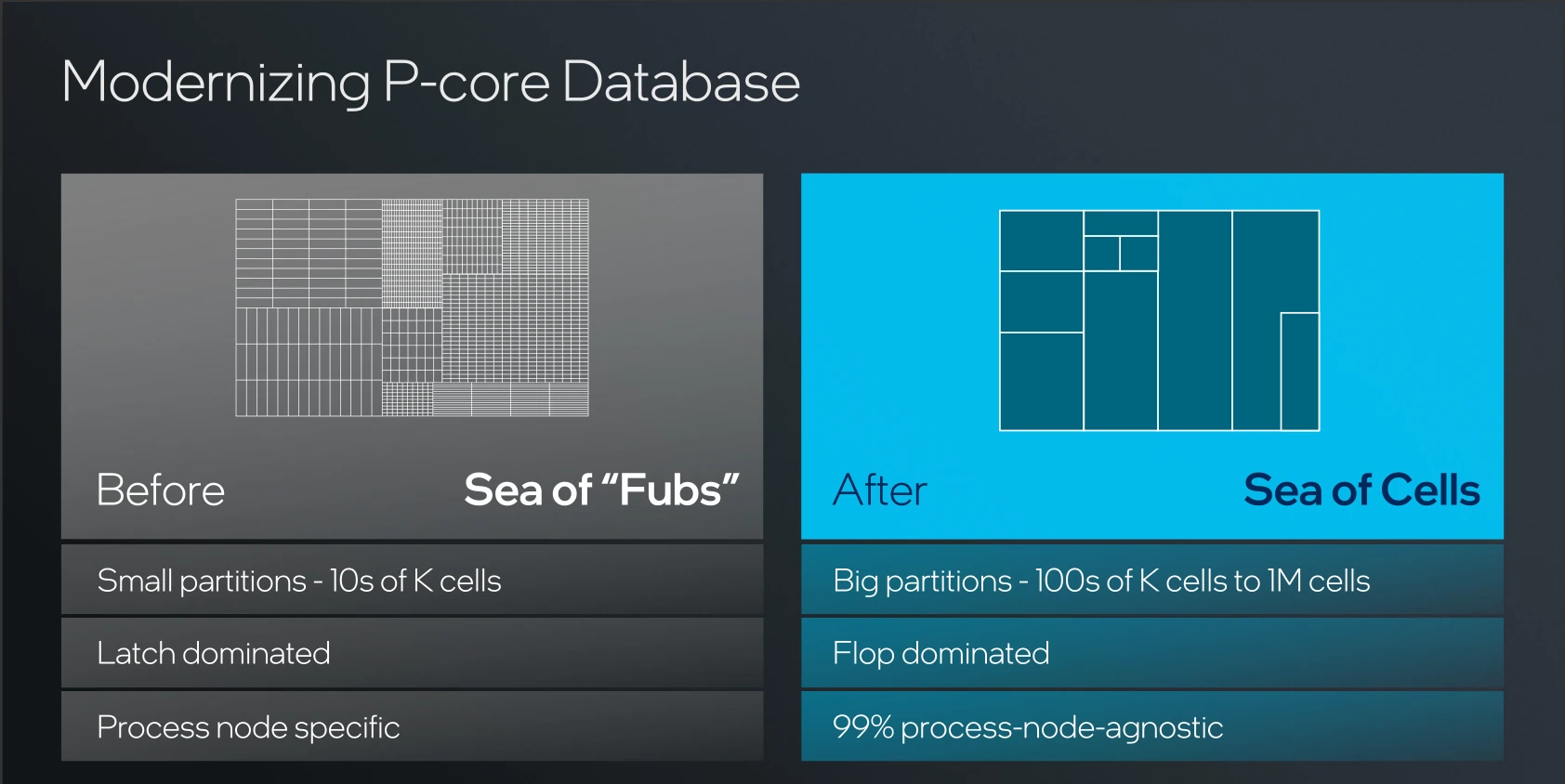

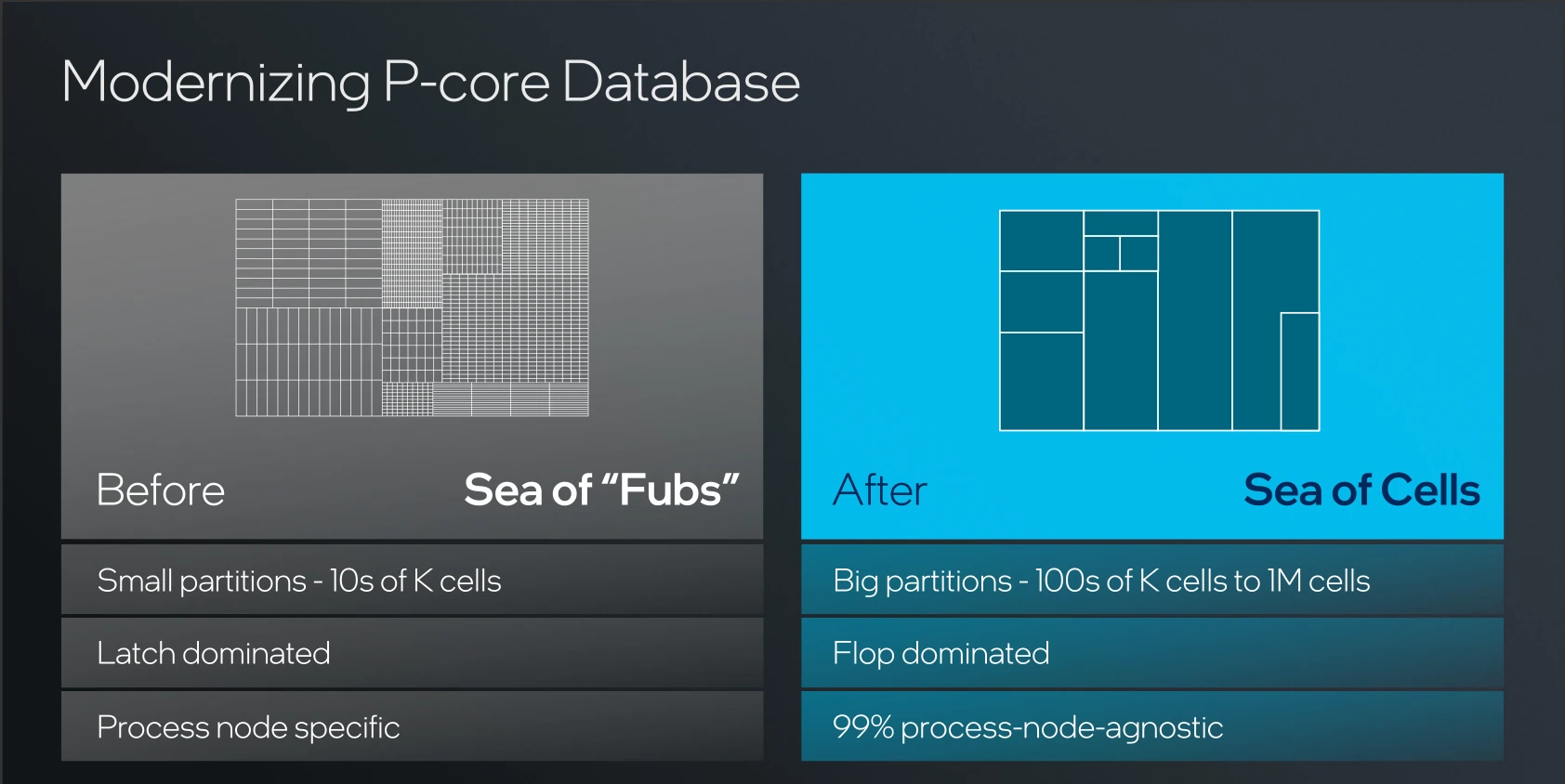

Pour porter le P-Core sur de multiples procédés de fabrication, il a fallut transitionner d'un modèles basé sur des blocks fonctionnels (Fubs, liés de près ou de loin au procédé) à des partitions regroupant des unités de taille bien plus grandes.

Pour revenir au SoC, le bousin intègre 2 puces de LPDDR5 (4x16 bits de bus chacune pour un total de 128 bits en utilisant le dual channel) pour 32 Gio de RAM maximum moulinant à 8500 Mtr/s : yabon le débit ! Nous nous doutons qu’une version 16 Gio sera également proposée vu l’architecture du bousin, quant au 24 Gio… difficile de se prononcer. Côté cœurs, la configuration complète comprend 4 P-Core non hyperthreadés, 4 E-Core non hyperthreadés, 8 cœurs Xe de seconde génération et un NPU rassemblant 6 Neural Compute Engine : pas de panique, tout cela sera détaillé dans les pages suivantes ! Les premiers appareils équipés étant prévus pour plus tard sur ce Q3 2024, les fréquences ne sont pas connues, mais la quantité de cache, elle, l'est : 12 Mio de L3 partagé sur les P-Core, 4 Mio de L2 sur les E-Core, et un System cache de 8 Mio assimilable à un L4, de type victime, permettant une communication plus rapide entre P et E cores.

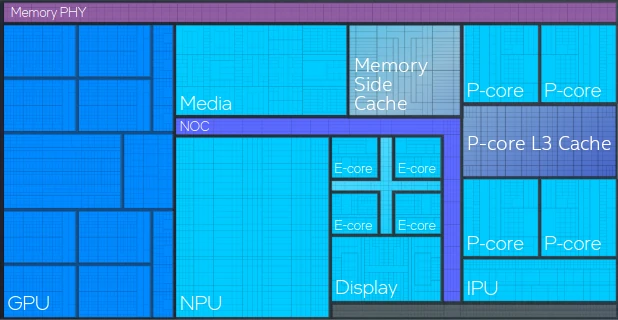

En zoomant sur la tuile de calcul (la plus grande, et la plus passionnante au niveau technique), nous trouvons :

- Des P-Core de nouvelle génération : Lion Cove

- Des E-Core également de nouvelle génération : Skymont

- Un GPU Xe de seconde génération

- Un NPU culminant à 48 TOPS justifiant la mention with Intel AI (soit 3 TOPS de plus que la prévision d’AMD… qui reste toutefois leader avec 50 TOPS)

Le compute die de Lunar Lake, découpé en blocs logique. La partie grise est l'interconnect permettant de dialoguer avec le die d'IO.

Appétissant ? C'est parfait, c'est justement ce que nous allons détailler dans ce dossier ! Tournez vite la page pour découvrir le secret des P-Core.

Tout cela est très intéressant

Ça peut paraître bizarre qu intel produit un cpu pas avec ça gravure

Le n3b est le die le plus efficient et le plus dense actuellement en plus intel est mauvais en transistors gpu ( haute densité ) voulant faire ultra compact et efficient c'est une bonne idée

A l'inverse le die soc en n6 me surprends

Pas besoin du n3b pour ce die il est ultra cher pour un gain très réduit ( les transistors hors ceux pour la logique progresse très peu voir quasiment pas vs le n5 )

Le n6 est "vieux" maintenant alors oui il est moins cher mais j'aurais plus vu n5 ou un de ses dérivé piur gagner en taille et en consommation

Bon après lecture approfondie j'ai l'impression que intel est revenue en arrière sur un point

Meteor lake avait explosé en mcm

La on revient comme avant Meteor lake le compute die intègre se qu'avait le die gen 13/14 et le second due c'est le chipset qui était côté

C'est la même chose mais emballé en 2.5d avec une nouvelle gravure

Le SMT s’avère surtout être une faille de sécurité perpétuelle, entre les fix et les patchs pas sur que ce soit vraiment une perte de performances de le virer 😅

Intel avec son lunar lake, qualcomm avec son xlite, amd machin truc et nvidia cpu machin truc... windows qui va devoir jongler avec les 4 ... Et tous les logiciels qui ne sont pas en natif et sans oublier tous les dell, asus et autre qui vont faire des variantes matérielles de leur ordinateur....

Quelle horreur la complexité des variantes et la fragmentation infinie que ça va engendrer et les bugs que Windows ne sait pas gérer...

Bonne chance pour que ça fonctionne sans accroche.... Faudrait songer à utiliser apple

Passez chez Apple, ils ont peu de variantes matérielle, ils créent leur propre puce, Ils font leur propre OS, tous les logicielles suivent Apple.

Amd et intel c'est du x86 donc pas de soucis et arm il y a emulateur apprement aussi performant que rosetta 2

Donc ça devrait aller

Apple ces gens qui décident arbitrairement quand ton ordinateur est obsolète en arrêtant de le mettre a jour, non merci 😬

Article beaucoup trop "technique" pour moi et mes maigres connaissances néanmoins je suis sûr que cela a fait plaisir à d'autres lecteurs qui ont du apprécier votre expertise et c'est bien là l'essentiel.

J'ai eu l'impression de relire certains articles de HFR !

C'était le bon temps hfr

J'avoue c'est complexe mais c'est aussi complet du coup

Après il y a les slides et les graphiques d intel plus simple à comprendre

Je ne cache pas que HFR ça a été notre référence et que c'est le type de contenu que nous visons. Le souci c'est qu'il faut vulgariser 20 ans de progrès hardware avant de lister les changements de la nouvelle génération ; dur dur pour quelqu'un qui débarque ! Cependant, avec un format récurrent expliquant certains mécanismes CPU peut etre une bonne idée pour pouvoir les référencer à divers endroits du dossier :-)

Moi jai compris les autres ..... 🤣

Super analyse très détaillée! En effet ça semble prometteur, faudra voir la réalité dans les produits.

La suppression de l'HT va forcément avoir un coût sur certains workloads, notamment ceux orientés I/O (stockage ou réseau) où il est possible d'avoir les drivers bindés sur les threads pairs et le userland sur les thread impairs, partageant ainsi le cache L2 avec une ultra-faible latence. Intel avait déjà fait ça sur les core2 en disant "meuh non de toute façon ça servait à rien" puis ils l'avaient réactivé sur les Core en disant "regardez ce qu'on vous a ajouté, c'est bien non?".

Pour le coup, la suppression de l'AVX512 est une ânerie. Ils ont investi plein d'extensions là-dedans, encouragé les clients à s'en servir, et au moment où leur concurrent préféré l'adopte de manière assez fûtée, ils baissent les bras. Pour moi ils auraient dû faire comme leur concurrent, et splitter les instructions 512 sur 2 ports 256 et n'en faire qu'une par cycle, et éviter ainsi d'affecter la consommation et la fréquence de fonctionnement. Ca permettrait au moins de profiter de certaines fonctionnalités utiles comme l'IFMA, très utile pour la crypto asymétrique.

A suivre...

Avx 512 va revenir avec avx 10

L'avx-512 reviendra pour les pro, mais ca fait depuis Alder Lake que ça n'est plus sur les proco grand public car les E-Core sont anémiques en calcul flottant (cest ~ du SSE derrière) et l'OS ne supporte pas des extensions différentes sur un même cpu

Pourquoi donc? Et le Thread Director, il n'est pas fait pour ça?

Non, Thread Director apporte un conseil sur un coeurs possiblement optimal pour placer. Un conseil n'est pas une contrainte !

Il faudrait que tous les processus déclarent en avance si ils utilisent de l'AVX512, et ça cassera la rétrocompatibilité (pour le moment c'est "tu lis un bit dans un registre interne, et si c'est une certaine valeur, alors tu as l'AVX-512", or si l'OS dit que tu est compatible, et que tu te fais scheduler sur un coeur dépourvu... boum). En plus, l'AVX-512 est très peu utilisé par le grand public et prend quand même un peu de place : sur un SoC basse conso, l'avoir est moins d'être une nécessité