Décidément, les temps sont durs pour Intel : après le départ (Abandon ? Licenciement ?) surprise de son PDG, une nouvelle information vient rajouter du plomb à l’aile du géant bleu. Selon Chosun, un média coréen, les rendements du prochain procédé développé en interne — le 18A, suite à l’abandon du 20A — seraient en deçà des attentes avec seulement une puce sur 10 fonctionnelle, soit 10 % de rendement. Aïe !

Début septembre, des échos relayaient que des négociations entre Broadcom et Intel avaient échoué du fait des performances insuffisantes du 18A, voilà qui nous apporte ici un possible élément de réponse… voire une explication au départ précipité du PDG ? Nous n’irons pas jusque là, bien que la tentation soit grande !

Car la concurrence des fonderies de second rang n’est pas si mieux loti que cela — enfin, hors TSMC pour qui la place de leader permet visiblement des mises au point plus rapides — car les soucis sont similaires chez Samsung avec son 3 nm de seconde génération donné à 1 puce sur 5 utilisable (ce qui est mieux, mais loin d’être mirobolant !). Reste que le 18A est censé entrer en production l’an prochain soit en 2025, ce qui laisse encore un peu de temps à la firme pour améliorer ce nombre.

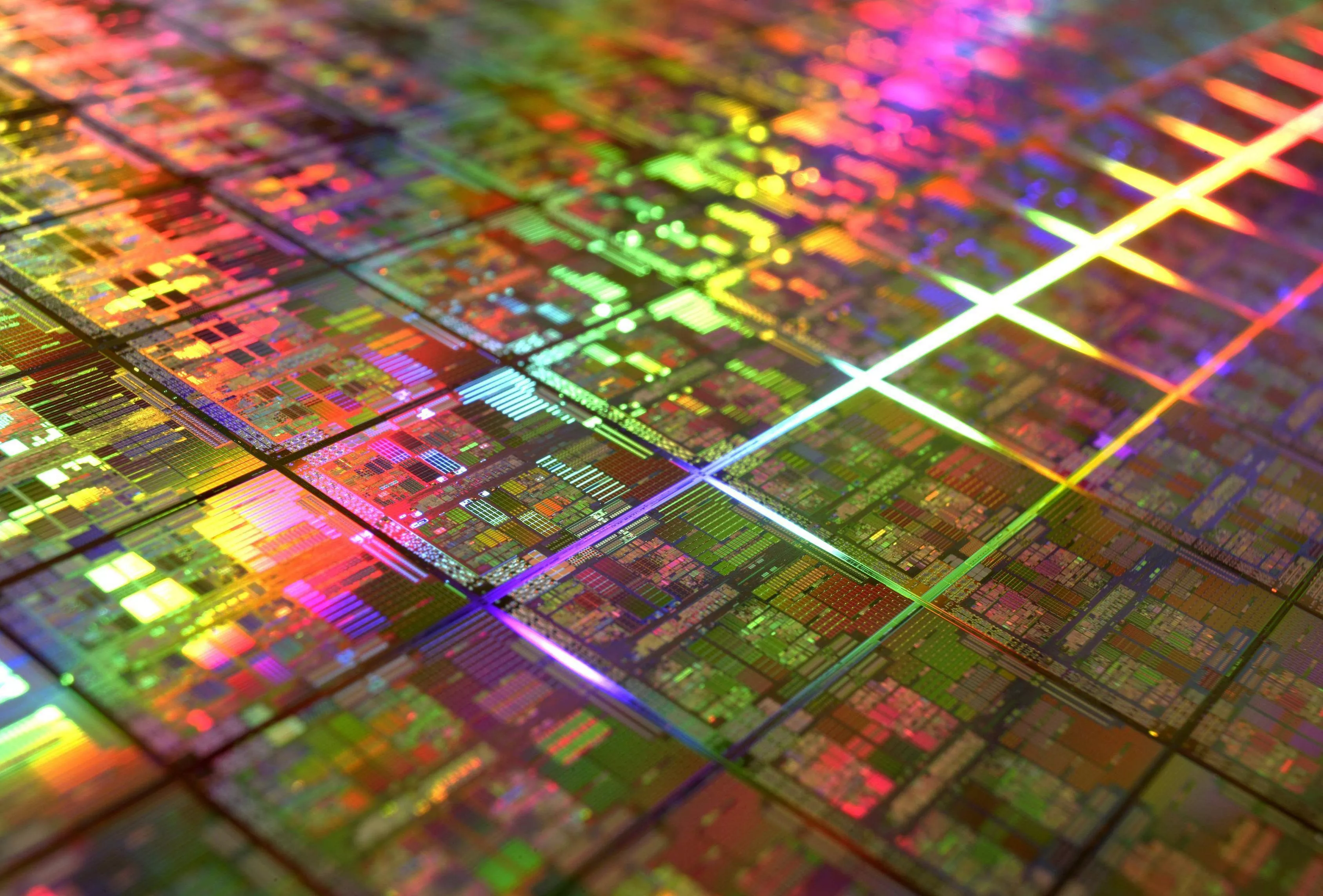

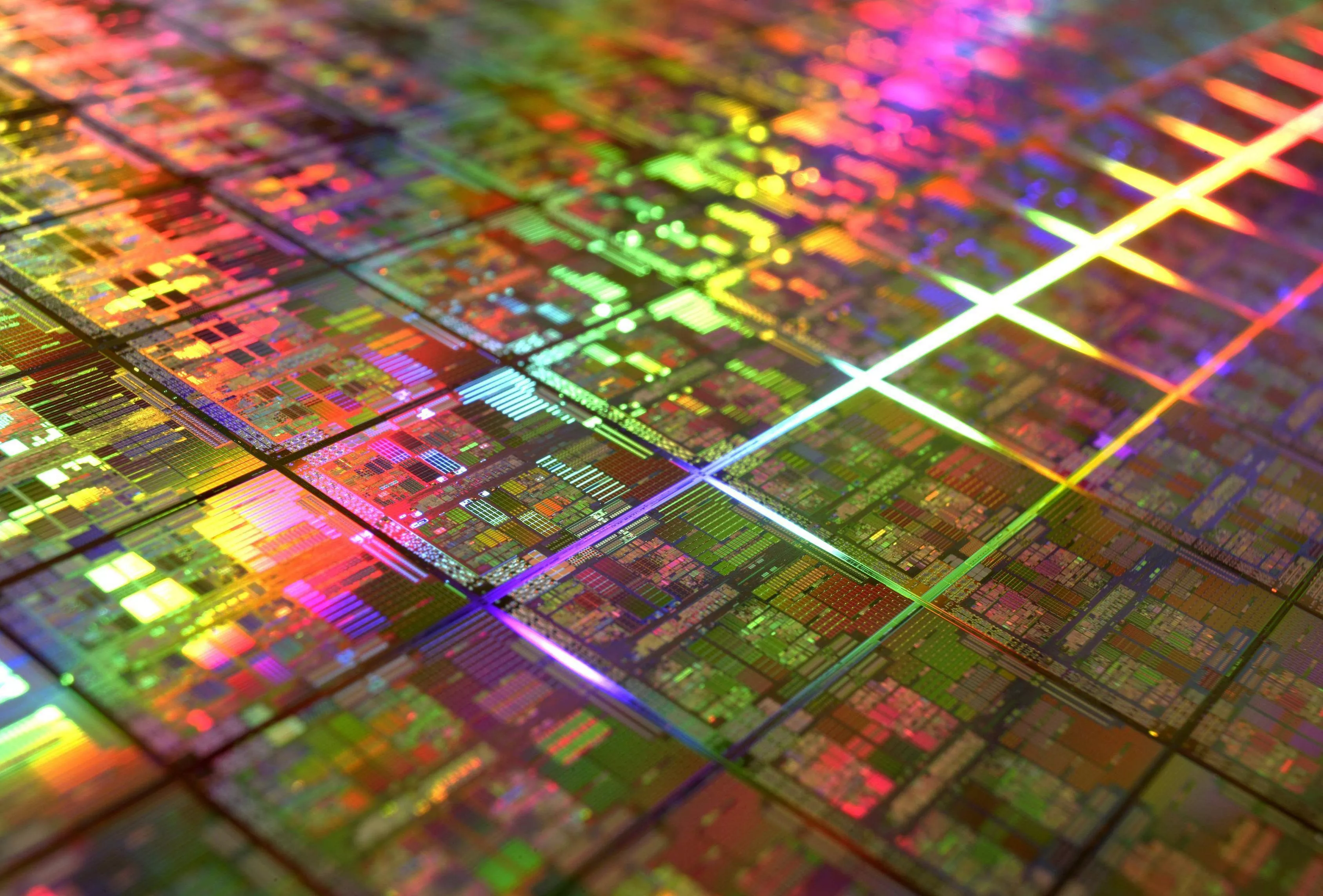

En théorie, ce nouveau node de gravure devrait propulser les puces serveurs Clearwater Forest ainsi que la prochaine génération de CPU mobile Panther Lake, tout en offrant des innovations de taille par rapport à l’état de l’art, à savoir la technologie des transistors GAAFET (nommé Ribbon FET chez les bleus) et l’alimentation des puces découplée du signal en arrivant par-derrière (Backside Power Delivery). Voilà qui explique en partie les difficultés de mises au point rencontrées par les bleus ! Rajoutez que les méthodes de gravures sont constamment améliorées, ce qui favorise l’émergence d’une entreprise leader unique (taïwanaise en l’occurrence…), mais encourage également la fabrication de dies à perte le temps de fiabiliser le bousin, surtout si la commercialisation est en avance sur la concurrence. Enfin, comme le rappelle notre confrère Ian Cutress (ex-AnandTech), le rendement dépend de la taille de la puce : 10 % sur des gros CPU ou GPU, cela est mauvais, mais peut également correspondre à plus de 60 % de puces de téléphones, bien plus petites. Et, avec les chiplets, les dies d’Intel sont justement de très petite taille… Rendez-vous l’année prochaine pour évaluer tout cela ? (Source : NotebookCheck)

J'aime beaucoup "l’alimentation des puces découplée du signal en arrivant par-derrière" en traduction de "Backside Power Delivery" même si je n'ai rien compris !

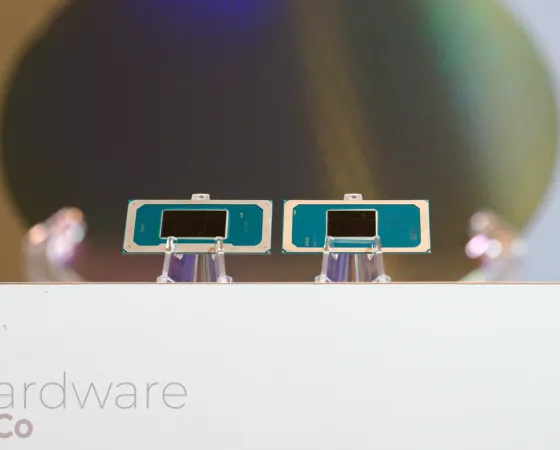

Au lieu d'avoir courant et données qui arrivent par la même face de la puce, le courant arrive de l'autre côté :) ; on l'a expliqué (un peu) plus en détail ici !

Le même jour on apprend que les phases de test du 2nm chez TSMC donne 60%+ de rendement. Pauvre Intel 😅

10 %, ok, mais avec quel type de puce ? Quelle taille ? 🧐

C'est LA question.

Si c'est des puces de 1m² c'est pas si mal 10% de rendement !

De ce que j'avais compris du contrat entre Intel et Broadcom c'était pour de belles grosses puces, dans les 600+ mm². 10% de yield serait alors cohérent avec les 0,4 défaut par mm² annoncés par Intel.

Pour des puces de la dimensions des CCD Zen4/5 ou Compute d'Arrow Lake ça ferait du 65~75% de yield. C'est pas dingue mais bien moins catastrophique.

Intel veut aller trop vite et ça ne marche pas

Le 10 nm est allé trop loin en densité et ça n'a pas marché

La gaa + alimentation arrière et en plus il y a apparemment plusieurs version de l'alimentation arrière intel lui lance directement la plus évolué

Tsmc réussi ils n'ont pas une façon miracle de faire les choses ils sont juste plus prudent une seul technologie à la fois le 2 nm est "juste" gaa l'alimentation arrière sera pour le a16

Ils sont même capables de retour en arrière le n3e est moins dense que le n3b pour améliorer les rendements et les performances