Intel est, certes, un concepteur de puces — dans le sens que la firme invente des designs, des nouvelles architectures afin de repousser les limites des performances CPU —, mais est aussi un fondeur, c’est-à-dire une boite qui fabrique physiquement ses puces à partir de grandes galettes de silicium. Une dualité qui lui est spécifique dans le monde de l’informatique haute performance, face à AMD et NVIDIA par exemple (seul Samsung effectue lui aussi une partie du design CPU et sa propre production, c’est dire à quel point la chose est rare !). Si cette caractéristique lui a valu longtemps la place de leader incontesté ; les choses ont changé ces 5 dernières années du fait de difficultés de mise au point de finesse de gravures plus avancées. Sous la houlette de Pat Gelsinger, la firme semble mettre les bouchées doubles pour rester compétitive, et cela se ressent au niveau des publications scientifiques.

En effet, à l’occasion de l’IEEE International Electron Devices Meeting 2023 (IEDM 2023), une conférence de chercheurs et autres ingénieurs barbus qui ouvre ses portes en ce moment même à San Francisco, spécialisée dans le domaine des semiconducteurs (et plus précisément de leur fabrication), Intel a publié quelques papiers dévoilant d’un peu plus près ce qui se cache dans ses laboratoires de R&D. Pour le néophyte, cela ressemble grosso modo à cela : "Hey, on va continuer à vous offrir le scaling de Moore, les gars !". Plus précisément, Intel tient à nous expliquer trois choses : quoi qu’il y aura après les Power Via, comment qu’on fait des puces en 3D, et quels matériaux du futur qu’on va mettre dans les processeurs plus tard.

Power Via : au delà du back-side power delivery

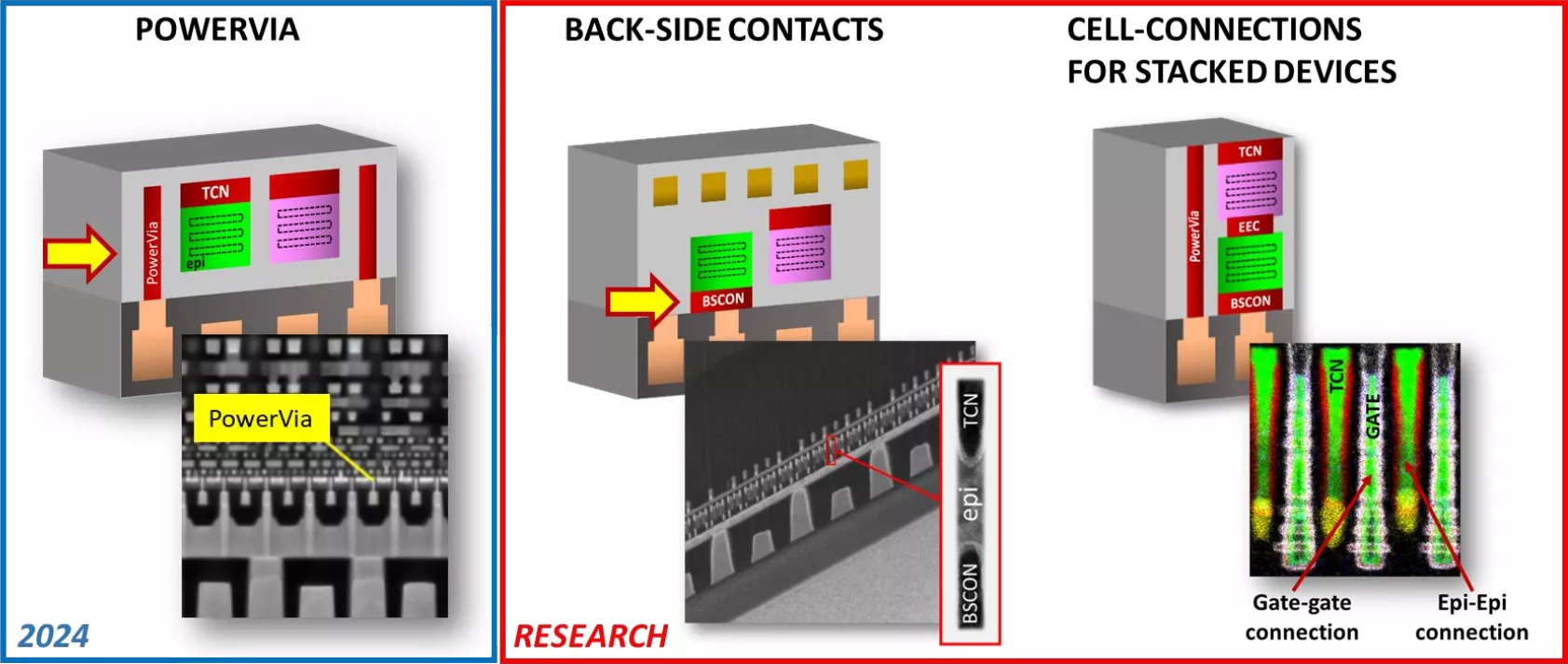

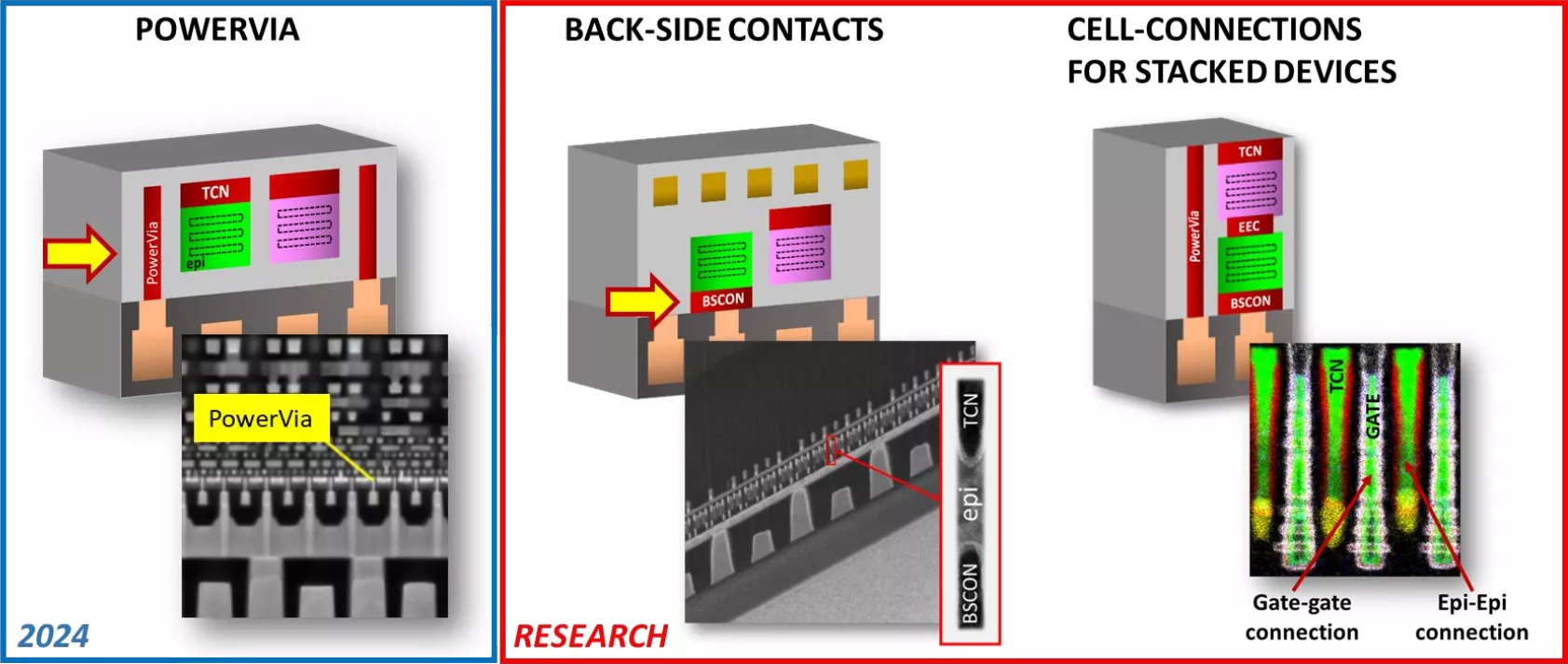

Commençons par les PowerVia. Actuellement, l’alimentation et l’interconnect (c’est-à-dire le dispatch des données entre unités du CPU) sont entremêlés dans les metal layers des puces : des couches situées au-dessus des transistors. Avec PowerVia, vos soucis disparaissent ! L’alimentation est découplé et passe sur le dessous des transistors, ce qui limite les interférences tout en autorisant un routage plus efficient : tout bénèf', chef. Cette technologie sera intronisée avec Arrow Lake en 2024 dans le procédé Intel 20A, à en croire les ingénieurs de la firme.

@1 h 2 pour l’illustration des PowerVia

Sauf que, si cette technologie est prévue pour 2025, c’est bien qu’elle a déjà quitté le labo de recherche. Ainsi, Intel présentait à l’IEDM des idées permettant d’aller au-delà de cette innovation (qui, au passage, sera également présente chez tous ses concurrents à terme). Qui dit nouvelle technologie, dit innovations encore relativement simples à comprendre. Un des soucis de l’implémentation PowerVia à venir réside dans la nécessité de passer l’énergie jusqu’aux couches supérieures, pour le moment très peu flexible. Hé bien, Intel est en train de bûcher sur un moyen de mettre de l’interconnect directement au-dessus de l’alimentation, mais sur la face "de-dessous" : il s’agit des back-side contacts — de quoi avoir toujours plus de possibilités de placement des diverses unités du CPU. Notez qu’il sera ainsi possible de connecter un transistor par le haut, par le bas ou les deux à la fois si besoin. Produit en interne par la firme sur des puces de démonstration, le procédé offrirait des caractéristiques physiques similaires des deux côté des transistors : prometteur ! D’un point de vue plus général, la technologie permet des gains en consommation ou en surface : le classique en semiconducteurs ; reste à voir ce qu’il en sera au niveau du coût de fabrication. Autre direction de recherche : un moyen d’interagir via les PowerVia dans le cas d’empilements 3D de transistors au moyen de connexions gate-gate et epi-epi.

Mentionnons également rapidement une technique permettant d’aligner les structures des deux côtés des wafers, ce qui permet ainsi d’éviter les défauts de gravures liés à désalignement de contacts, et, ultimement, le rendement.

CFET : c’est parti pour des transistors en 3D ?

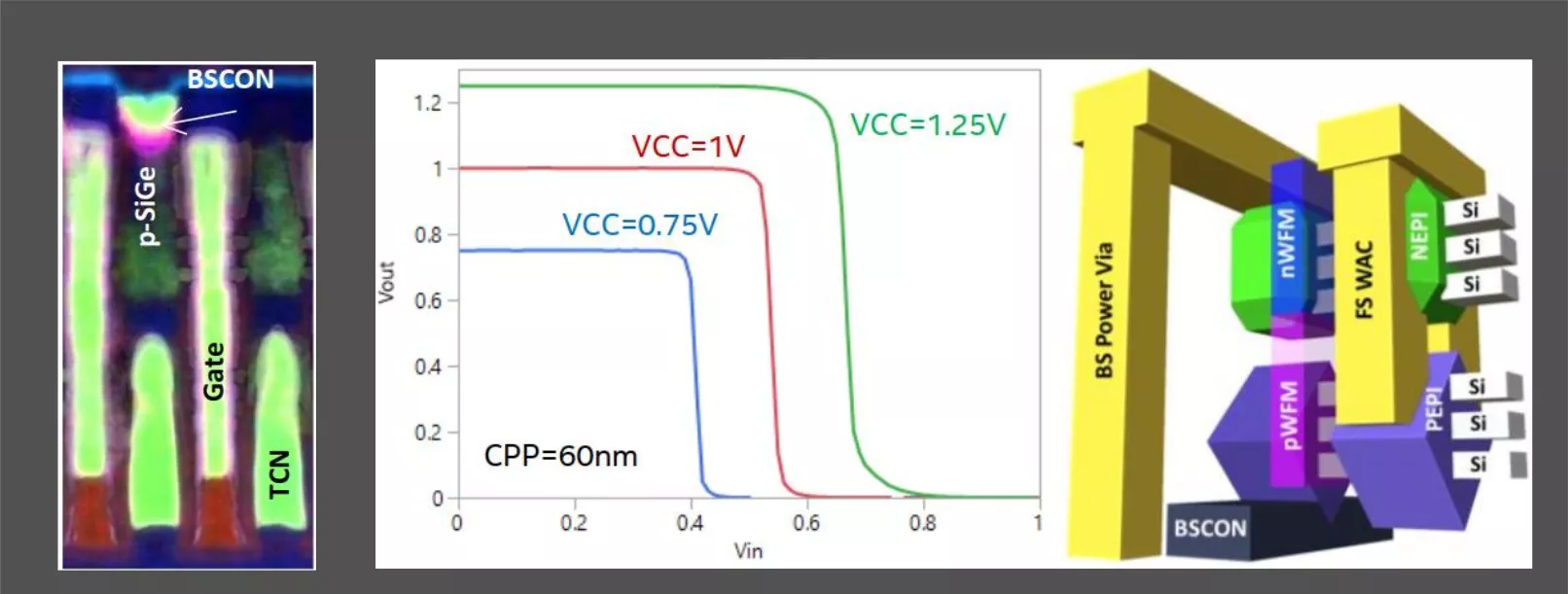

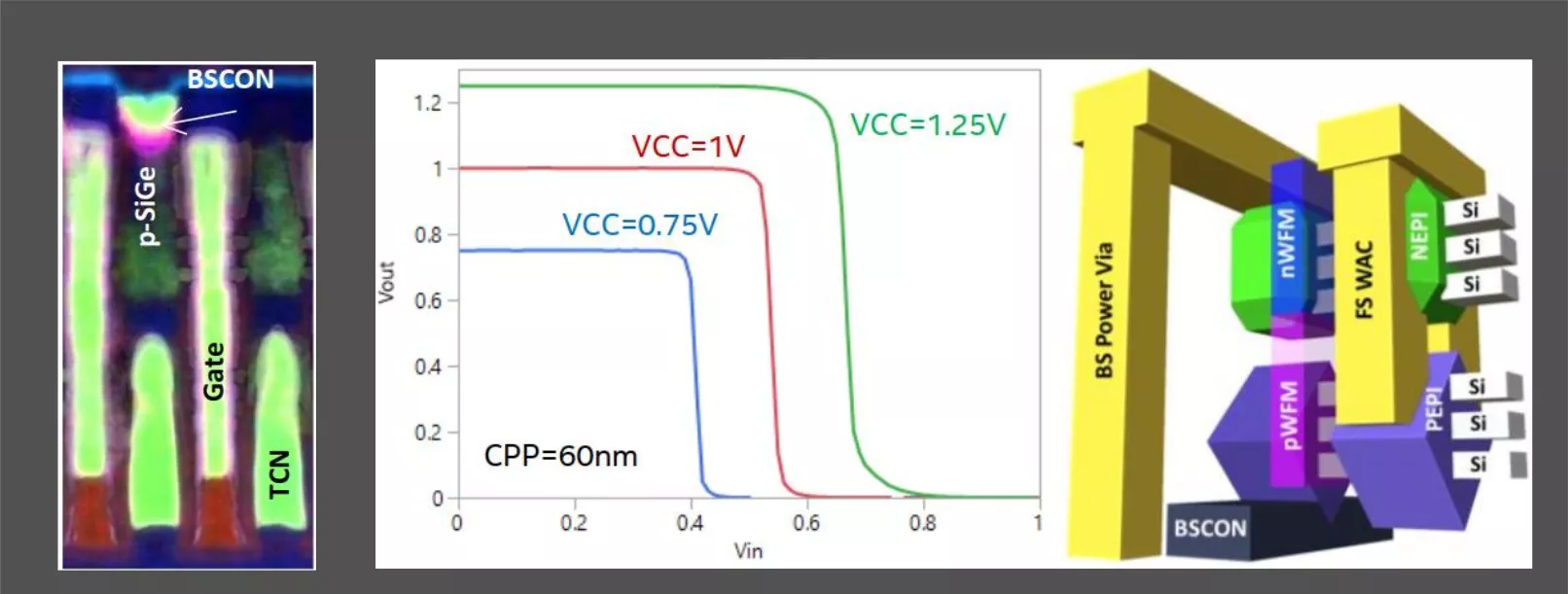

Si vous avez pensé à un empilement de type Foveros à la mention des empilements 3D de transistors, vous vous êtes mis le doigt dans l’œil ! En effet, il n’est pas question ici de coller deux dies séparés, mais bien de superposer deux transistors sur une seule galette de silicium, formant ainsi des CFET (Field-Effect Transistor). Présenté à gauche sur l’image ci-dessous, Intel a réussi à empiler deux transistors GAAFET (les fameux RibbonFET du Intel 20A) à 3 rubans... ce qui est bien plus visible sur le schéma de droite ! Difficile cependant de décrire l’intégralité des structures, sachez donc seulement que cela rassemble tout le beau monde vu jusqu’ici : PowerVia, Backside Contacts et connexions epi-epi. Au niveau des résultats, même conclusion qu’à l’accoutumée : le bousin permet une réduction de la tension d’opération, ce qui améliore la densité ou baisse la consommation, au choix selon le bon désir du designer.

Du gallium dans nos CPU !

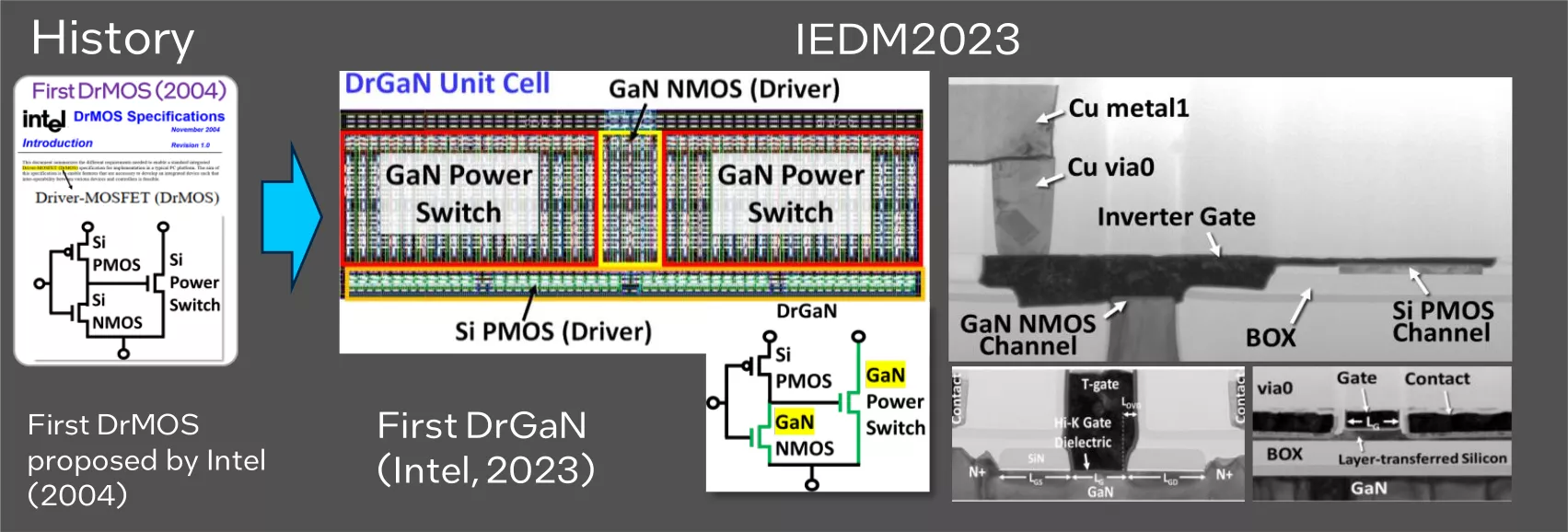

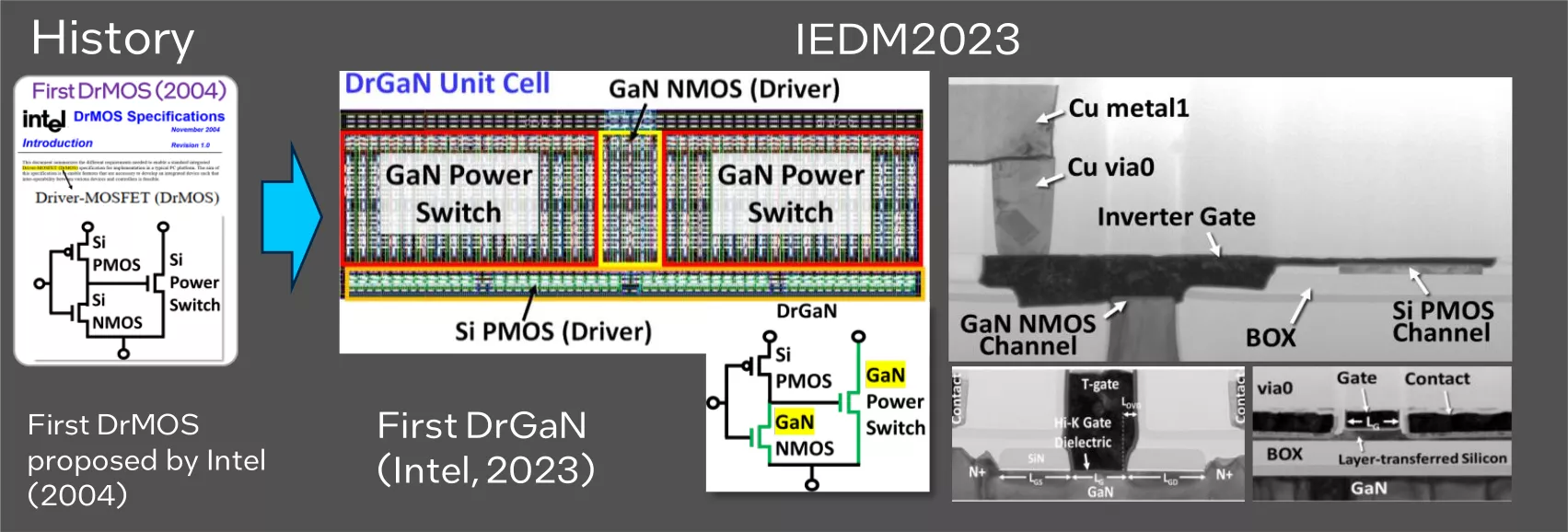

Si les GAN actuels réfèrent le plus souvent aux Generative Adversarial Neural networks, une technologie d’IA permettant des résultats impressionnants en matière de génération d’image, ici, il n’est rien de commun ! En effet ce GaN (notez la casse) correspond à du nitrure de gallium, un matériau qui a le vent en poupe pour ce qui est des semiconducteurs d’alimentation chez Samsung. Du côté d’Intel, la firme présente le premier DrGaN monolithique (pour "Driver GaN", même si "Docteur GaN" sonne quand même bien plus classe !), gravé à partir d’un unique procédé : une première mondiale. Késako ? Tout simplement un certain type de VRM supportant toujours plus de courant de manière toujours plus efficace. Si cela semble anodin, il faut savoir que le DrMOS, maintenant présent dans les phases d'alimentation sur l’écrasante majorité des composants, est également originaire des laboratoires d’Intel en... 2004 ! À voir si cette nouvelle génération saura rencontrer le même succès, mais pour cela, il faudra encore passer l’étape de la production de masse.

Merci pour cet article très technique. J'aime ça 😃

Alors on partage, on clique zou zou zou !

Blague à part, merci beaucoup, et moi aussi. Ça n'est jamais facile d'avoir des gens de la recherche qui expliquent ce qu'ils font, et encore moins les conséquences que cela peut avoir à grande échelle (d'autant plus que ce n'est jamais certain, à ce stade !). Même si c'est "mis en scène" par Intel pour leur faire de la pub', je trouve l'initiative géniale.

C'est couillu leurs CFET. J'ai hâte de voir leurs derniers développements dans leurs produits. Plus généralement ça donne vraiment l'impression que pour le moment on est à bout en 2D pour augmenter la densité, et que le passage en 3D se fait dans le désespoir.