Une mise à jour timide de la microarchitecture CPU

Si vous espériez une revue en profondeurs des blocs présents dans les cœurs, alors vous risquez d’être déçu. En effet, les modifications de l’intérieur des P-Core comme de E-Core tiennent davantage de l’évolution que de la révolution. Il faut dire qu’après la remise à niveau architecturale modifiant en profondeur le pipeline sur Lunar et Arrow Lake, Panther Lake devrait se contenter des gains liés à la lithographie uniquement si la firme suivait la stratégie du célèbre tick-tock — alternation d’une amélioration de la gravure et d’une révision architecturale chaque nouvelle génération. Heureusement pour nous, les transistors se sont quand même faits tripatouiller, de quoi faire grandir ça et là certains caches et autres algorithmes internes pour toujours plus de performances. Voyons cela ensemble.

Cougar Cove : la digne lignée des P-Core continue

Bien qu’Intel soit récemment revenu sur son abandon de l’HyperThreading, Cougar Cove en demeure dépourvu, tout du moins la version intégrée dans Panther Lake. Pour les autres… Il va falloir encore patienter un peu ! En revanche, au niveau des changements, nous retrouvons un TLB en forte augmentation avec 1,5 fois plus d’entrées (soit un passage de 128 à 192 entrées pour le D-TLB… mais pas seulement celui-là !), ce qui permet d’améliorer les performances lors de l’utilisation de la virtualisation ; ce qui comprend la technologie VBS de Microsoft, active par défaut sous Windows 11.

Les heuristiques de désambiguïsation de la mémoire sont également améliorées, ce qui permet de court-circuiter le L0 dans le cas où un chargement suit un rangement encore non terminé — typiquement dans le cas de spilling. Comme leur nom l’indique, il est question d’heuristiques, c’est-à-dire pari effectués sur la base d’informations incomplètes : dans le meilleur des cas, la valeur est bien la bonne et l’exécution est rapide, sinon, il faut attendre quelques cycles de plus et annuler l’opération. Ainsi, en peaufinant cette désambiguïsation de la mémoire, Intel permet une exécution à la fois plus rapide et mieux prédictible, ce qui est apprécié des programmeurs de bibliothèques (partiellement) en assembleur.

Enfin, la prédiction de branchement est également revue, mais, comme beaucoup des présentations bleues, les détails ne sont pas explicités. Essentiellement basé sur celui de Lion Cove, cet étage est à la fois peaufiné au niveau algorithmique — c’est-à-dire que les tags, métadonnées des branches déjà prises, contiennent plus d’information — mais aussi au niveau de la taille des structures… sans pour autant donner de chiffres. Le tout résulte en une prédiction plus précise et plus rapide en matière de latence : bingo ! Notez qu’Intel assure avoir travaillé à d’autres endroits du processeur, mais de manière trop fine (ou trop secrète ?) pour communiquer sur tous les points.

Pour le reste, nous vous invitons à relire notre page Lion Cove du dossier relatant la microarchitecture précédente : nous retrouvons en effet les 18 ports d’exécution, la hiérarchie L0/L1/L2/L3, avec un maximum de 18 mégas pour le dernier cité soit une augmentation de 50 % — bien que cela soit essentiellement lié à la présence de clusters de E-Core partageant également ce dernier niveau de cache.

Darkmont : les E-Core ont aussi droit à leurs évolutions

Similairement aux P-Core, les E-Core se voient également revus, toujours en légère évolution par rapport au Skymont précédent. Ainsi, les 26 ports d’exécutions sont toujours de la partie, le pipeline restant également inchangé sur sa profondeur. En revanche, le nanocode (microcode stocké sous la forme de tableaux programmables [PLA], capables d’être accédés en parallèle par plusieurs des trois décodeurs) progresse et couvre plus de cas et d’optimisation dans lequel le CPU passe par le (plus court) chemin du nanocode. Au niveau du sous-système mémoire, le preftech est plus précis du fait d’une télémétrie accrue — merci le machine learning de pouvoir analyser toutes ces données !

Tout comme Cougar Cove, la prédiction de branchement est revue pour augmenter la taille de certaines mémoires et retoucher ça et là les algorithmes, mais, une fois encore, impossible de savoir comment ! En revanche, Intel communique sur la présence de divers modes de fonctionnement de l’étage de décodage, qui peut aller jusqu’à s’éteindre complètement dans un but d’économie d’énergie lorsque le processeur détecte que toutes les instructions sont issues des caches — typiquement dans le cas de courtes boucles reconnues par le Loop Stream Detector. Enfin, les heuristiques de désambiguïsation de la mémoire sont elles aussi en progrès, car le composant est partagé entre les cœurs P et E. Pour plus de détails, retournez à la section du Cougar !

Et… alors ?

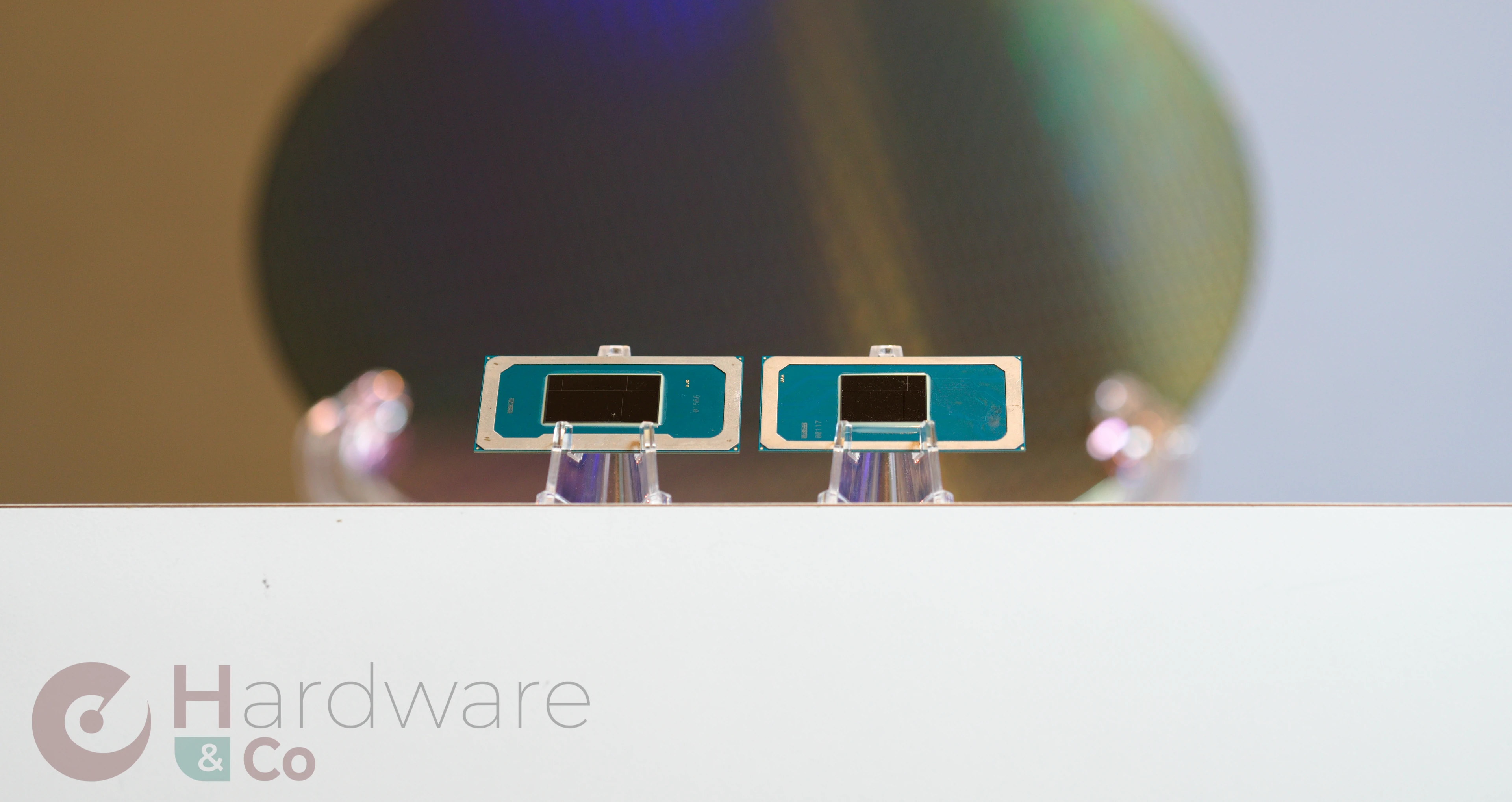

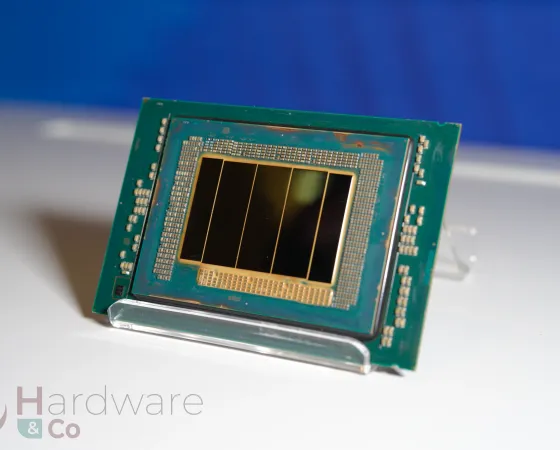

Individuellement, les changements sont alléchants, mais limités. Or, Panther Lake est une génération de SoC, pas seulement de cœurs, qui s’inscrit dans le sillage d’Arrow Lake pour ce qui est de la versatilité. Ainsi, pour couvrir tous les segments de TDP, deux configurations du die de calcul ont été retenues. La première est de configuration identique à Lunar Lake, avec 4 P-Core, 4 LP E-Core et rien de plus : de quoi peupler le segment des ultraportables. La véritable nouveauté se situe sur le second die de calcul, obtenu en rajoutant 8 E-Core sur le ring du L3 à son petit frère. En effet, la progression y est large par rapport à Arrow Lake : doublement des LP E-Core pour passer à un cluster complet, ce qui double aussi son L2 pour atteindre 4 Mio, et passage à la microarchitecture Darkmont, véritable révolution tant les Crestmont accusant déjà une génération de retard (conséquence du jeu de réutilisation de la tuile SoC de Meteor Lake) étaient limités.

Notez que le Memory-side cache est bel est bien sur la Scalable Fabric : le L3 y est bien relié, mais la gestion de la priorité / éviction favorise le cluster LP dans une logique d’efficacité énergétique.

En pratique, Intel se garde bien (comme à son habitude) de clamer des chiffres absolus du côté des performances, mais évoque des améliorations par rapport à la génération précédente. Et, comme rien n’est simple, cette dernière est ou bien Lion Cove (commun à Lunar Lake et Arrow Lake, pour les performances en single thread), ou bien Lunar Lake (pour le rendement énergétique) ou bien Arrow Lake (pour la performance multithread). Ainsi, Panther Lake — Cogar Cove, quoi — apporterait 10 % de performances ST à isoconsommation, mais surtout 40 % de consommation en moins à isoperformances (attention, il s’agit du SoC complet !). Du côté des performances multicœurs, cette génération serait en progrès de 50 % à isoconsommation (par rapport à Lunar Lake, donc pas le cador du genre) et 30 % de gain en consommation à isoperformance (cette fois-ci par rapport à Arrow Lake, donc, encore une fois pas l’élite du genre). Notez les conditionnels, les dires d’Intel à ce niveau-là n’engageant qu’eux : rendez-vous d’ici quelques mois pour les premiers tests indépendants !

Intel Thread Director, toujours dans la place !

Une des raisons de l’échec de Meteor Lake et Arrow Lake sur le plan de l’autonomie se situait dans le scheduling, ou ordonnancement en bon français, c’est-à-dire l’art d’associer à chaque processus actif un cœur. En effet, dans les tâches d’utilisation courantes, l’ordonnanceur était censé utiliser uniquement les 2 LP-Core, ce qui s’est avéré insuffisant et, en réveillant le gros cluster, la consommation augmentait drastiquement. Avec Lunar Lake et Panther Lake, ces LP E-Core ont été mis à jour avec un doublement de leur nombre et une architecture plus puissante… mais cela ne rend pas le boulot de l’OS plus simple pour autant.

Ainsi, la panthère fait également usage de l’Intel Thread Director comme tous les SoC depuis Alder Lake, une interface permettant de faire remonter des conseils de scheduling depuis le matériel (constitués sur la base de compteurs de performances) au système d’exploitation. Puisque les profils de performances des cœurs sont différents, l’algorithme de conseil a dû être réentraîné, tout comme la télémétrie sur laquelle ce dernier se repose, mais ce n’est pas tout. Avec la continuation d’un agencement hétérogène à trois niveaux, l’algorithme évolue avec une politique "E-Core first" : dans la plupart des cas, les 4 LP E-Core sont désignés en premier, puis les 8 E-Core si le programme demande plus de threads, puis les 4 gros P-Core en cas de besoins spécifiques (calcul vectoriel, IA). Une illustration valant mille mots, voilà quelques exemples d’utilisation :

Enfin, Intel s’est attaqué au slider de mode de performance de Windows, jugé trop limité. Directement dérivé des consignes de la part des OEM quant au positionnement de la machine sur le plan performance/consommations, croisées à des tables préremplies par Intel, le bousin n’offre que des profils statiques, c’est-à-dire indépendant de l’application en cours d’exécution. Or, le mode "équilibré" n’offre selon les bleus actuellement pas assez de flexibilité en castrant trop les performances lors des cas extrêmes, sans pour autant offrir l’autonomie du mode basse consommation, même si le travail effectué n’est pas critique. Bref, une politique de gestion de la puissance statique n’est pas optimale, c’est pourquoi ce profil "équilibré" sera remplacé par un Intel Intelligent Experience Optimizer, qui viendra dynamiquement appliquer un sous-mode adapté selon l’utilisation active, penchant plus vers les "meilleures performances" au besoin, particulièrement sur batterie. De quoi rajouter près de 20 % de performances monothread supplémentaires dans des charges synthétiques. Reste à voir si le bousin n’est pas trop sensible à la détente, c’est-à-dire gourmand en batterie en pratique !

C’en est tout pour ce qui est des cœurs et de l’ordonnancement, tournez la page virtuelle pour découvrir les changements du côté GPU et gaming… qui pourraient bien recauser légèrement de scheduling !

Les évolutions architecturales sont faible mais l'augmentation du nombre d'unité cpu/gpu va dans le bon sens

Le 12 xe sera t il disponible a faible tdp ?

J'ai peur que face a un apu 12 core zen 6/6c 16 core cpu mais 12 e/lpe core ça ne va pas etre suffisant

Côté gpu intel va etre devant amd en attendant udna

Pas d'infos sur les SKU officiellement, il faut regarder les rumeurs. Néanmoins, il est très souvent possible de brider les puces avec un faible TDP (ou les faire thermal throttle dans le pire cas).

Appriorie pas de 12 xe en version u dommage