Aux dernières nouvelles, Intel Foundries était très heureux de nous causer High-NA, une technique révolutionnaire permettant de graver toujours plus fin à savoir pour le 14 A. En revanche, ce procédé est prévu pour 2026 au plus tôt : pour les générations suivantes, il va falloir taper dans du plus épais : l’Intel 4 (actuellement à l’œuvre sur le Compute Tile de Meteor Lake) et l’Intel 3 (tout juste en production sur les tout derniers Xeon Sierra Forest et Granite Rapids). Un Intel 3 qui est a désormais atteint le stade de la production de masse dans les fab d’Oregon et d’Irlande selon Walid Hafez, le vice-président du département Foundry Technology de la maison-mère. Bref, Intel rattrape peu à peu son retard, conformément à ses plans ; et, pour permettre à tous d’en profiter, la firme tenait une présentation fort édifiante lors de la présentation d’un papier de recherche sur les bienfaits de l’Intel 3, paru à l’occasion du VLSI Symposium on Technology and Circuits de l’IEEE, sauce 2024.

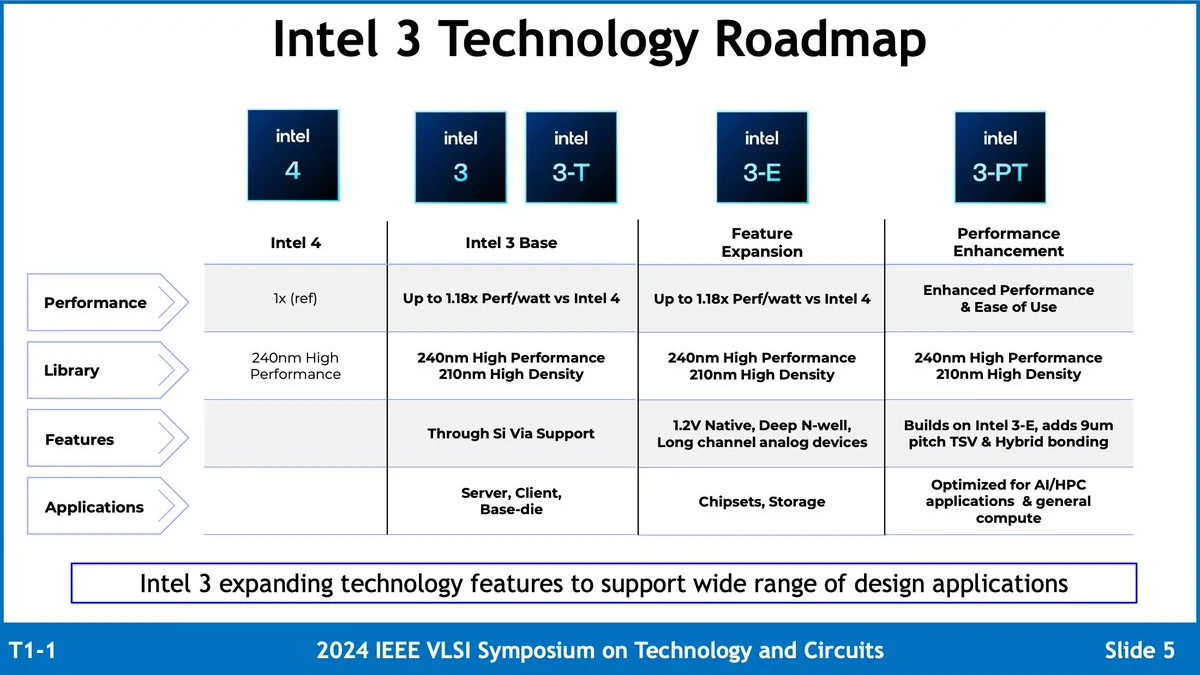

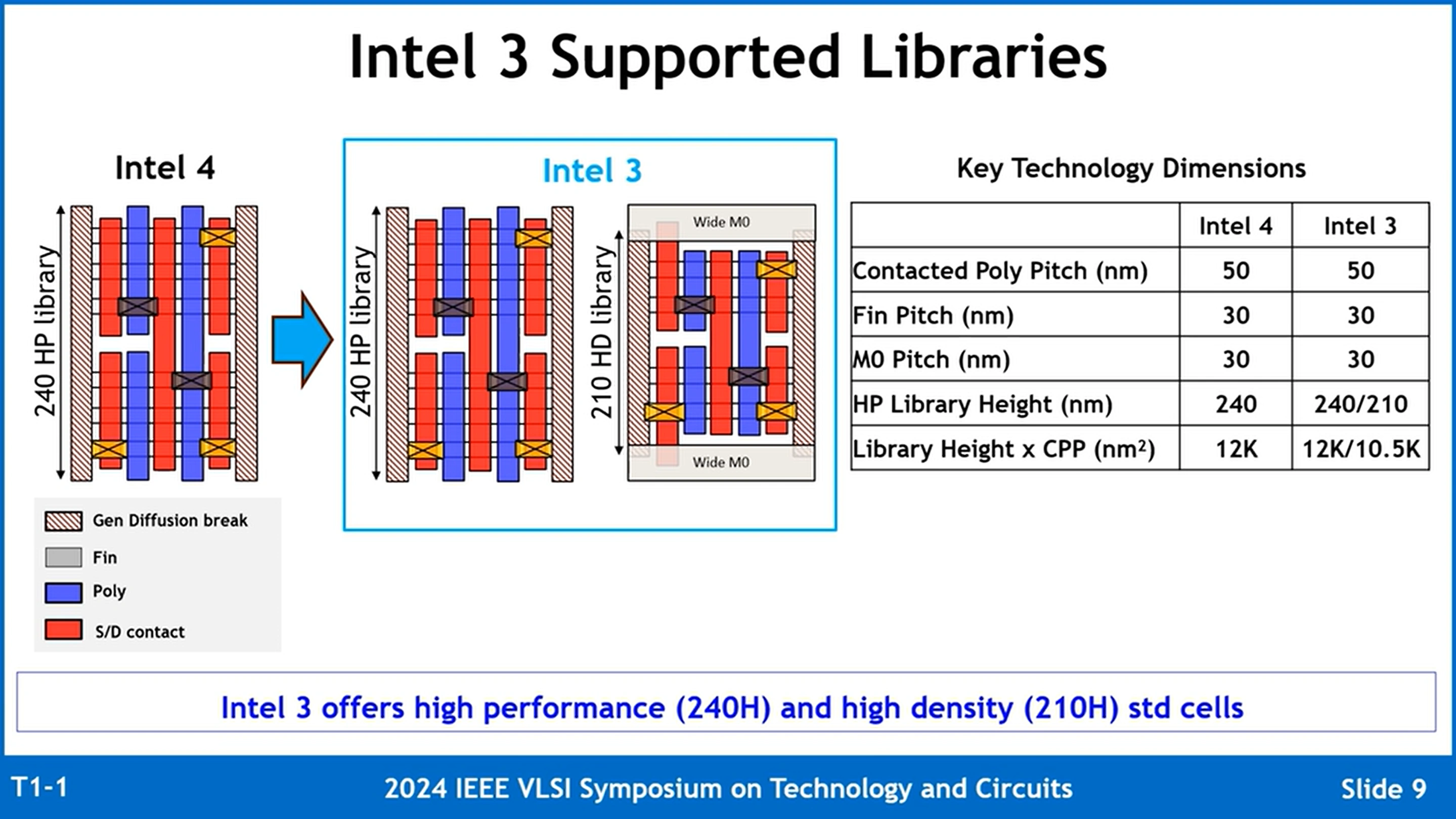

Dans cette présentation, nous apprenons que l’intel 3 peut être utilisé pour du calcul haute performance (du bon gros CPU, quoi !) tout comme du SoC via 4 variantes :

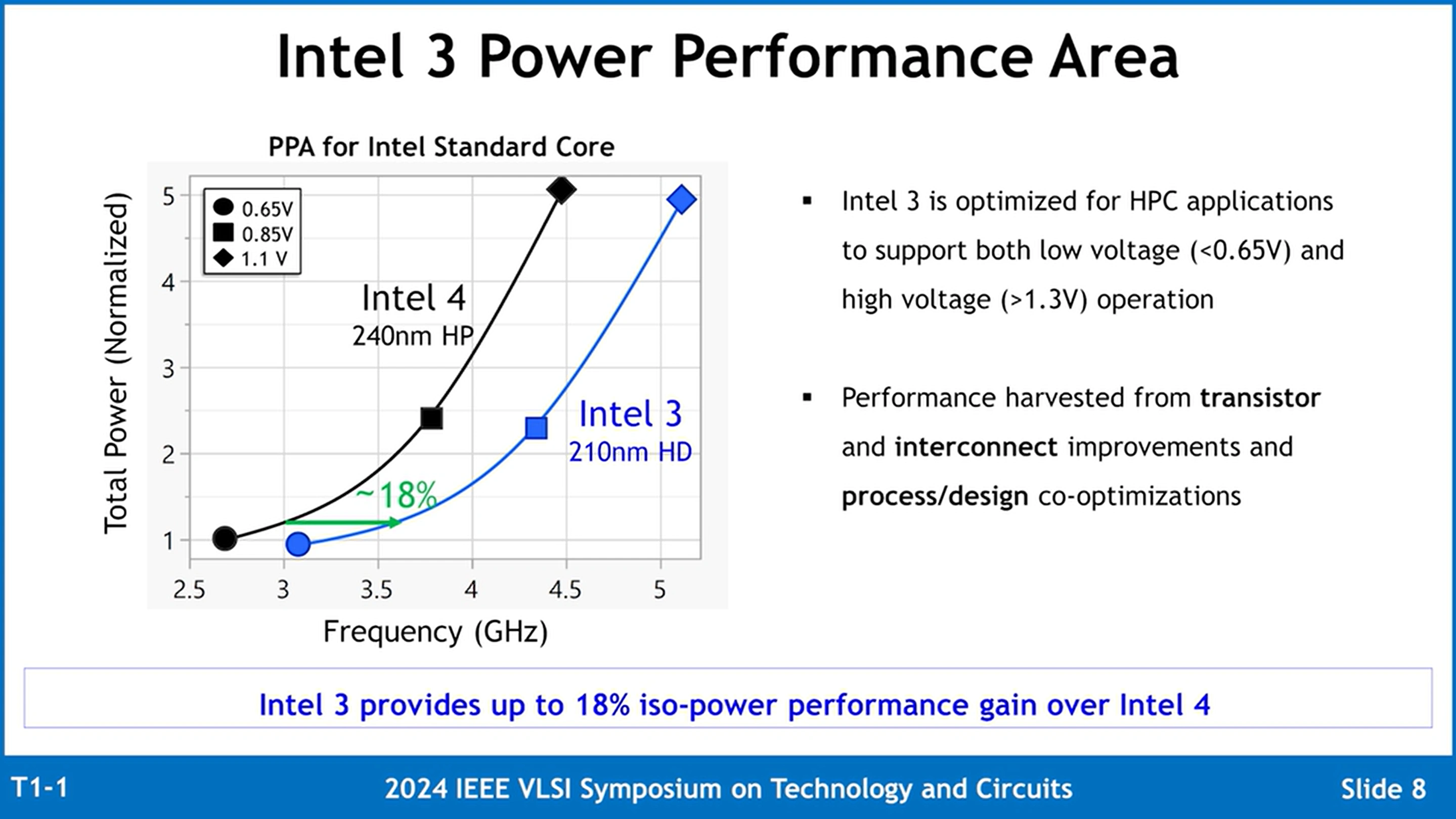

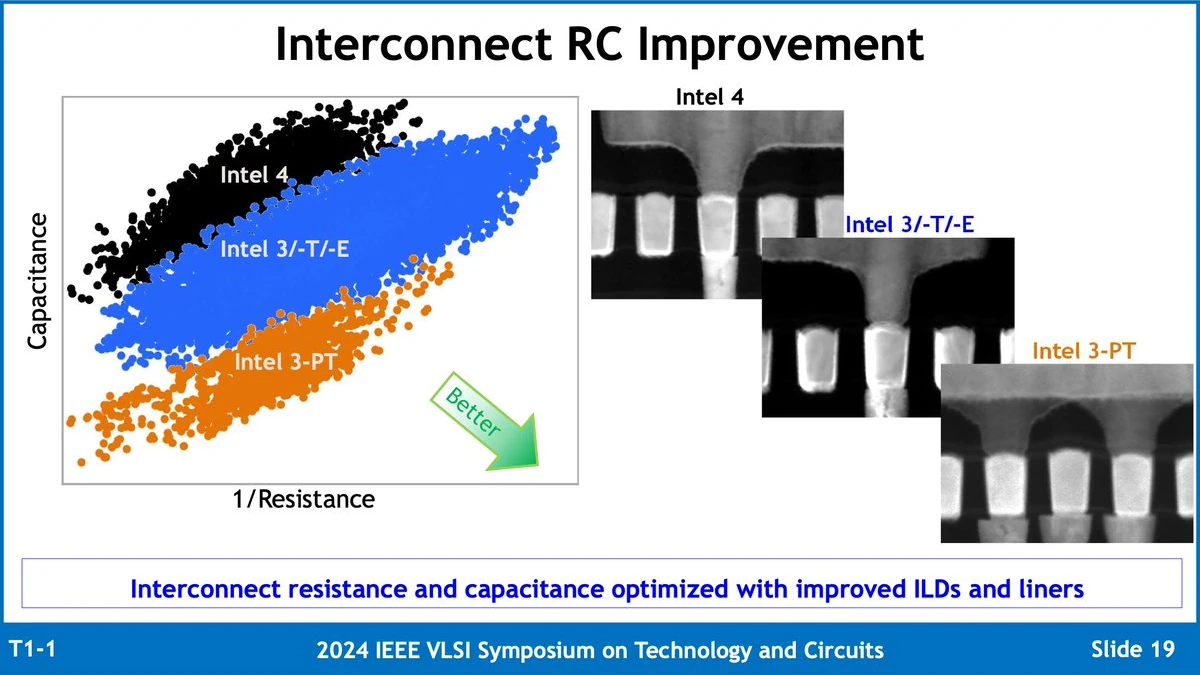

- Le Intel 3 de base, qui propose (au choix) des gains de 18 % en performance par watt par rapport à l’Intel 4, ou un gain de 10 % en densité, le tout via une optimisation complète du procédé, du transistor jusqu’aux couches métalliques chargées d’effectuer le routage. Vu la récente arrivée de l’Intel 4, la prouesse peut être saluée !

- Le Intel 3-T, qui rajoute la possibilité d’intégré des TSV (Through-Silicon Vias, des trous pour le passage du courant à travers le silicium afin d’alimenter un die stacké, typiquement en utilisant la technologie Foveros).

- Le Intel 3— E, qui permet d’utiliser des tensions un peu plus élevées (1,2 V) afin d’être utilisées pour graver des interfaces d’I/O ou gérer des signaux analogiques

- Le Intel 3-PT, qui est un genre de mix des trois précédents dans une version plus exigeante encore, avec des TSV plus fins (9 µm) et l’utilisation de l’hybrid bonding pour le stacking, permettant de créer des liaisons cuivre-cuivre en direct et ainsi gagner en densité de connexion.

Selon la firme, la version PT est là pour durer « dans les années à venir » : de quoi laisser penser à une intégration sur Arrow Lake dès Q3 2024 ? P'tet ben que oui, p'tet ben que non : il est plus logique d’y voir la version 3 tout court, avec le 3— E appliqué au chipset et le 3-PT sur… autre chose (GPU et Gaudi ?). Rajoutez que l’Intel 3 pourra intégrer, au choix, 14, 18 ou 21 couches métalliques d’interconnexion des transistors, permettant de jongler entre des versions moins coûteuses ou plus performantes.

Dans tous les cas, le fondeur de Santa Clara nous semble paré pour déballer sa stratégie PAO (procédé de gravure, architecture, optimisation) sur son Intel 3 (« la version ultime du FinFET », après cela, il faut passer au 18A et au RibbonFET) et proposer moult déclinaisons avec les gains en performance que cela induit. (Source : HardwareLuxx, Wccftech)

Une partie des amélioration de l'Intel 3 : moins gourmand, plus dense et moins propices aux effets de résistance / capacitance. Youpi !

En très grosse simplification intel à crée l intel avec des transistors haute perf qui sont ceux qu'il utilise le plus souvent avec pour objectif de faire x2 en densité ( meteor lake )

Puis une fois maîtrisé il a adapter ça à tout type de transistors

C'est une version qui va durer car c'est la dernière sans gaa qui sont un bon dans les coûts