Sierra Forest, voilà un nom qui vous est peut-être familier. En effet, Intel nous avait présenté le bousin en fin mars 2023 avec un objectif de taille : toper les 288 cœurs par socket. Pour cela, le fondeur de Santa Clara est allé chercher dans ses tiroirs la meilleure architecture en sa possession capable de répondre au besoin : Crestmont. Un choix qui convient finalement parfaitement à la demande de certains professionnels : proposer le plus de cœurs dans le moins de place possible afin d’obtenir le coût total d’opération (TCO) le moins cher possible pour des machines virtuelles à la demande. Comprenez, des serveurs privés virtuels (VPS) et autres hébergeurs web se contenant de cœurs basse consommation pour faire tourner diverses tâches légères de manière centralisée dans le cloud… Hardware & Co en est un parfait exemple, puisque le site est actuellement hébergé sur une machine virtuelle à 4 cœurs voguant au gré des vents sur un CPU EPYC bien mieux pourvu. Vu la multitude de site web et autres applications connectées nécessitant un tel service, la demande est conséquente.

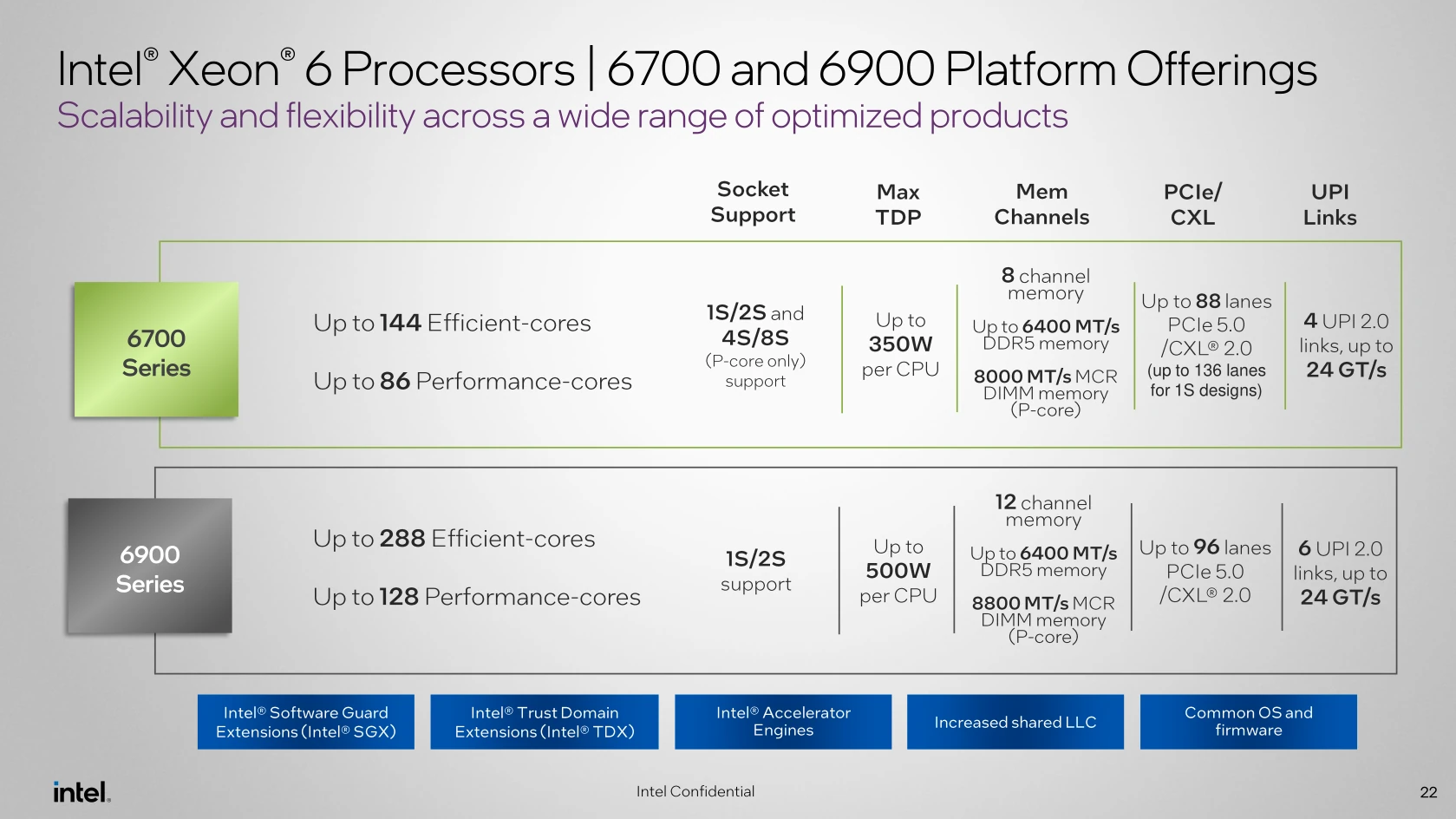

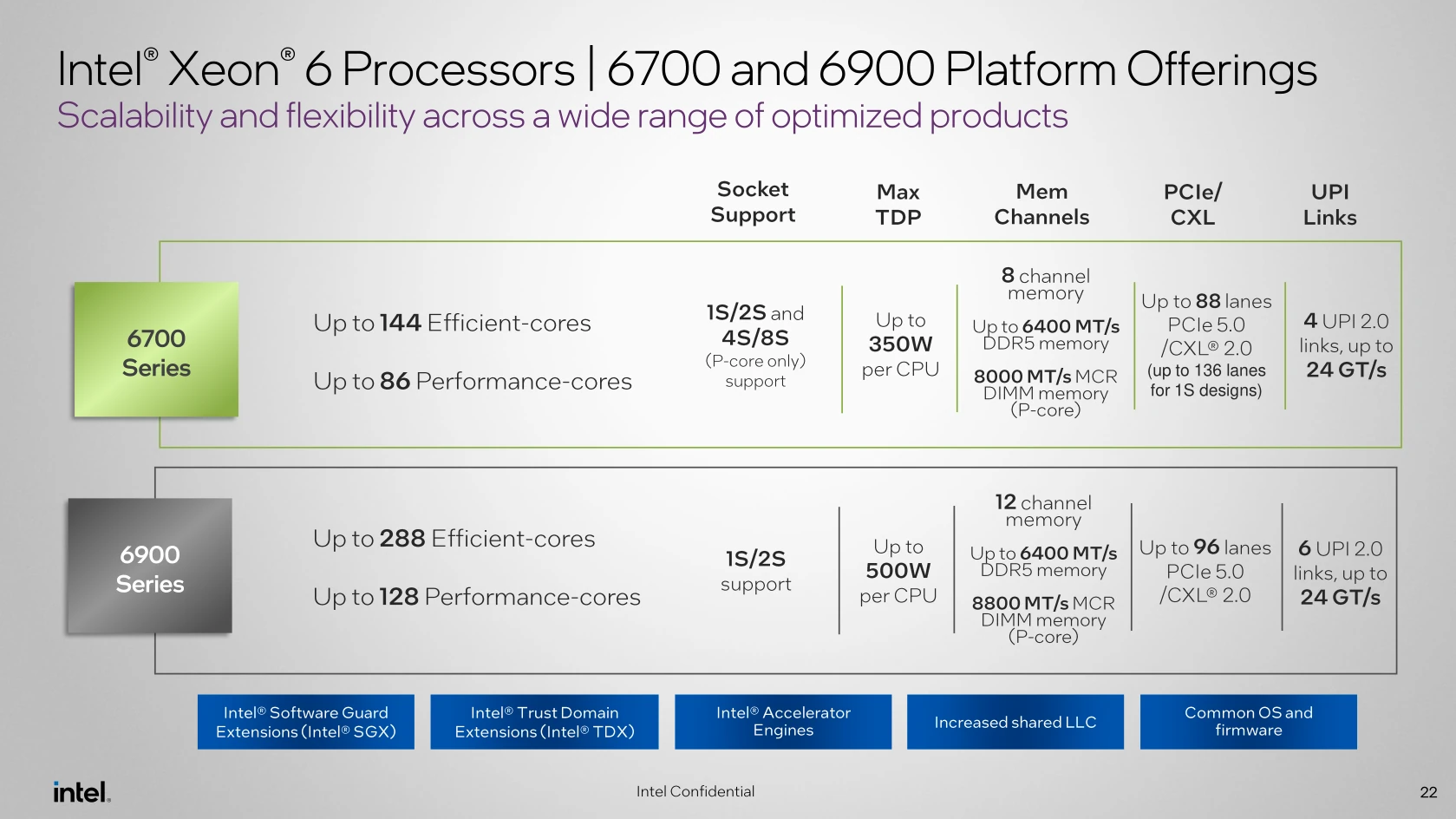

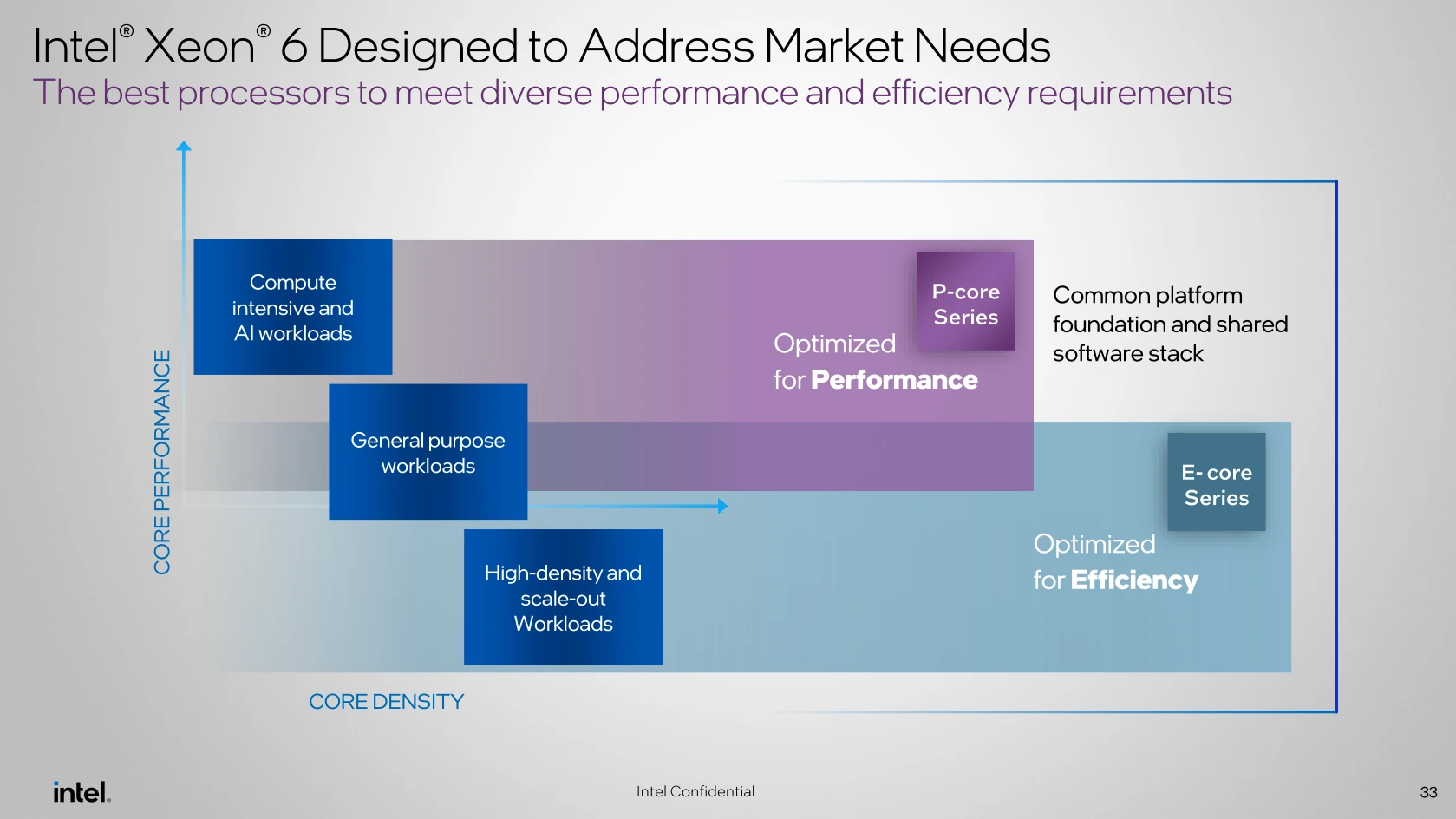

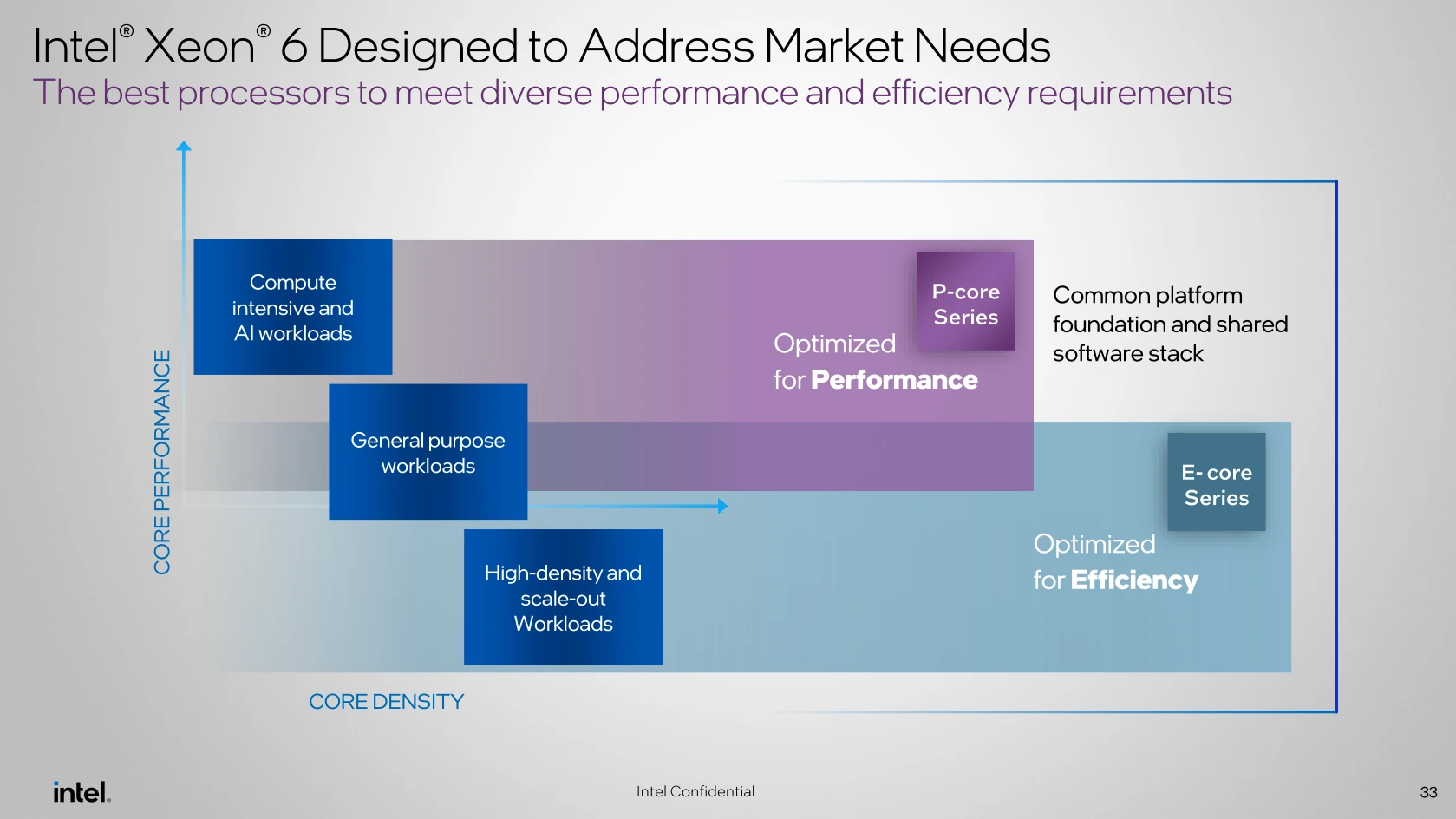

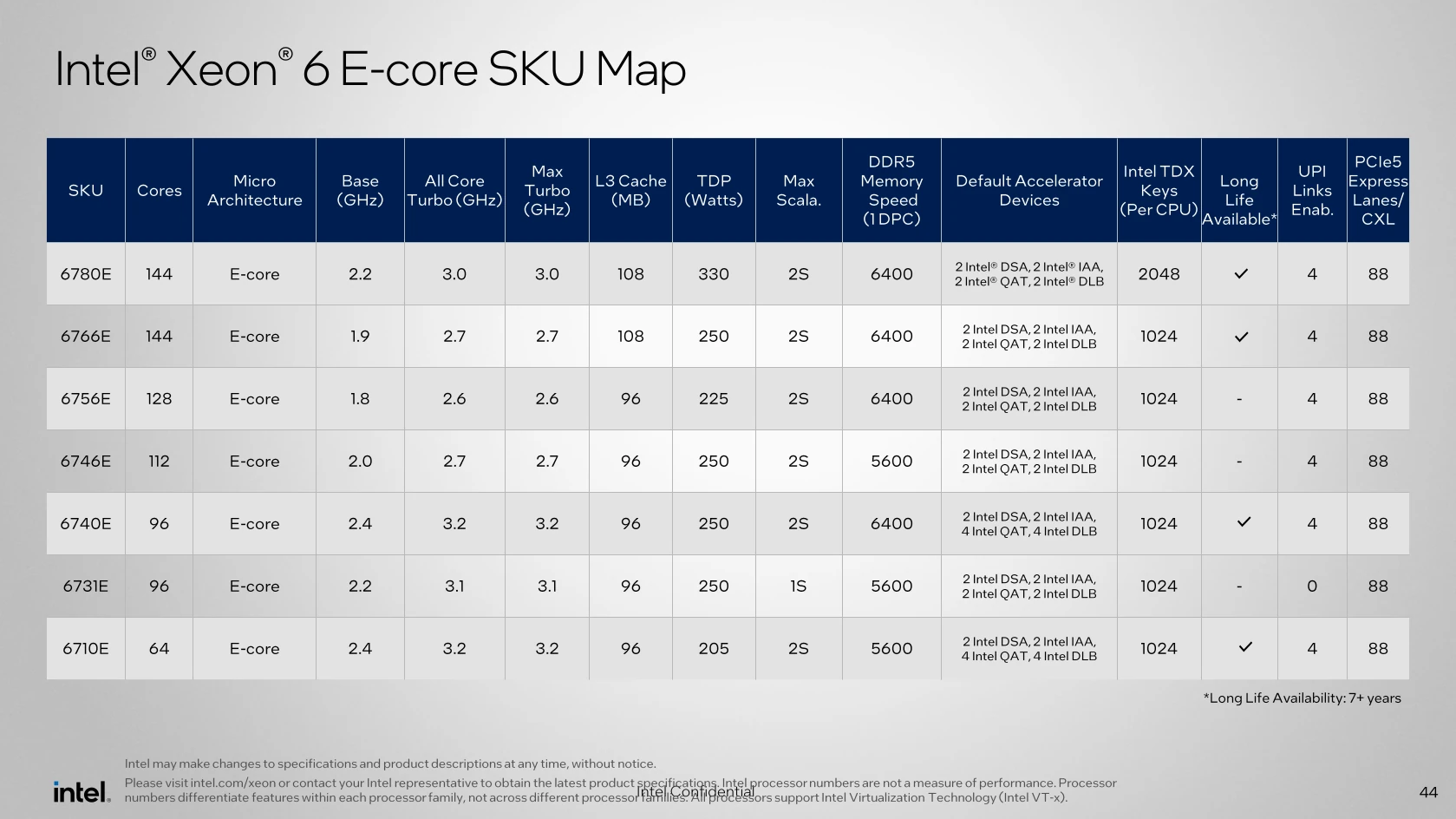

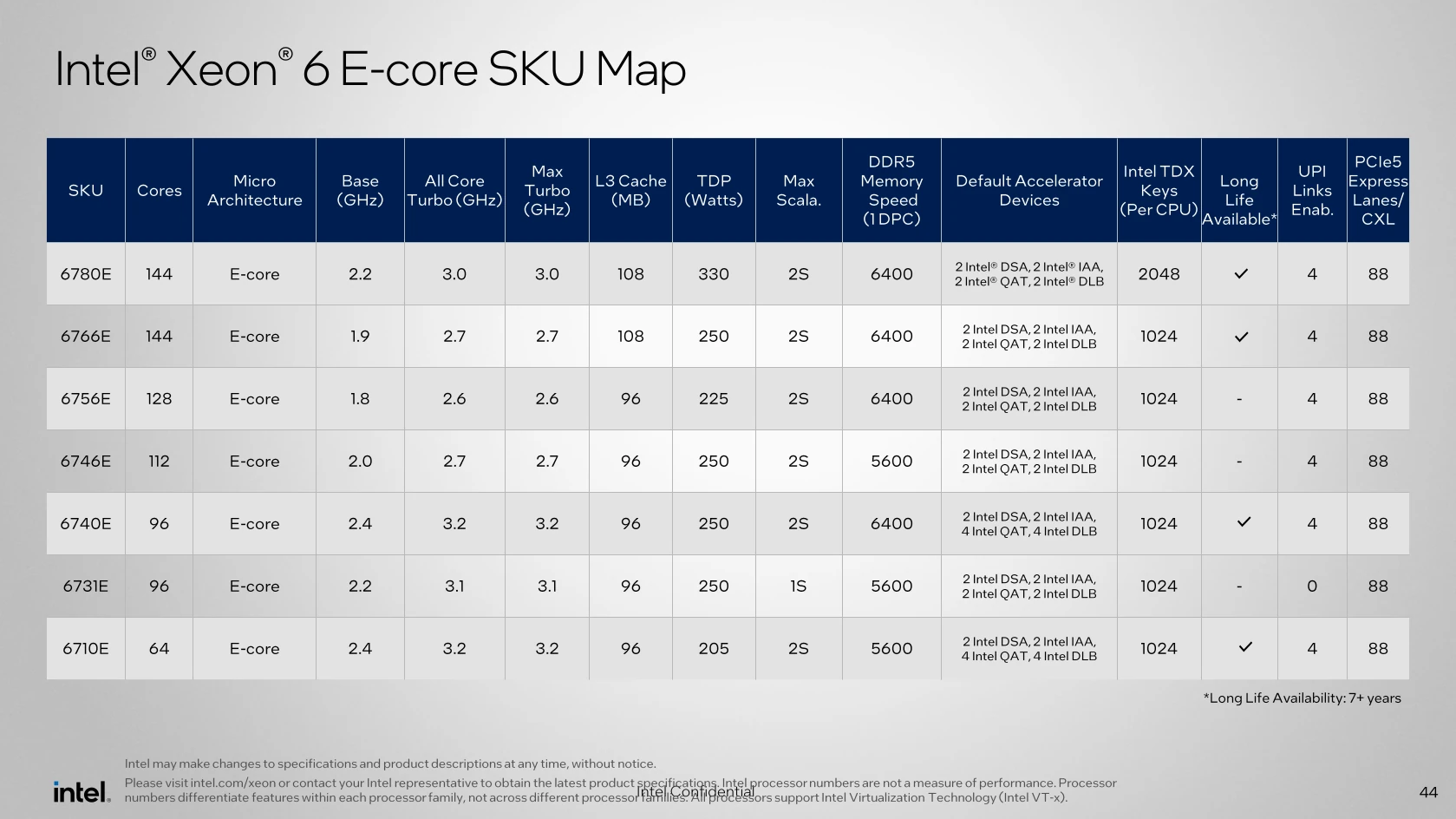

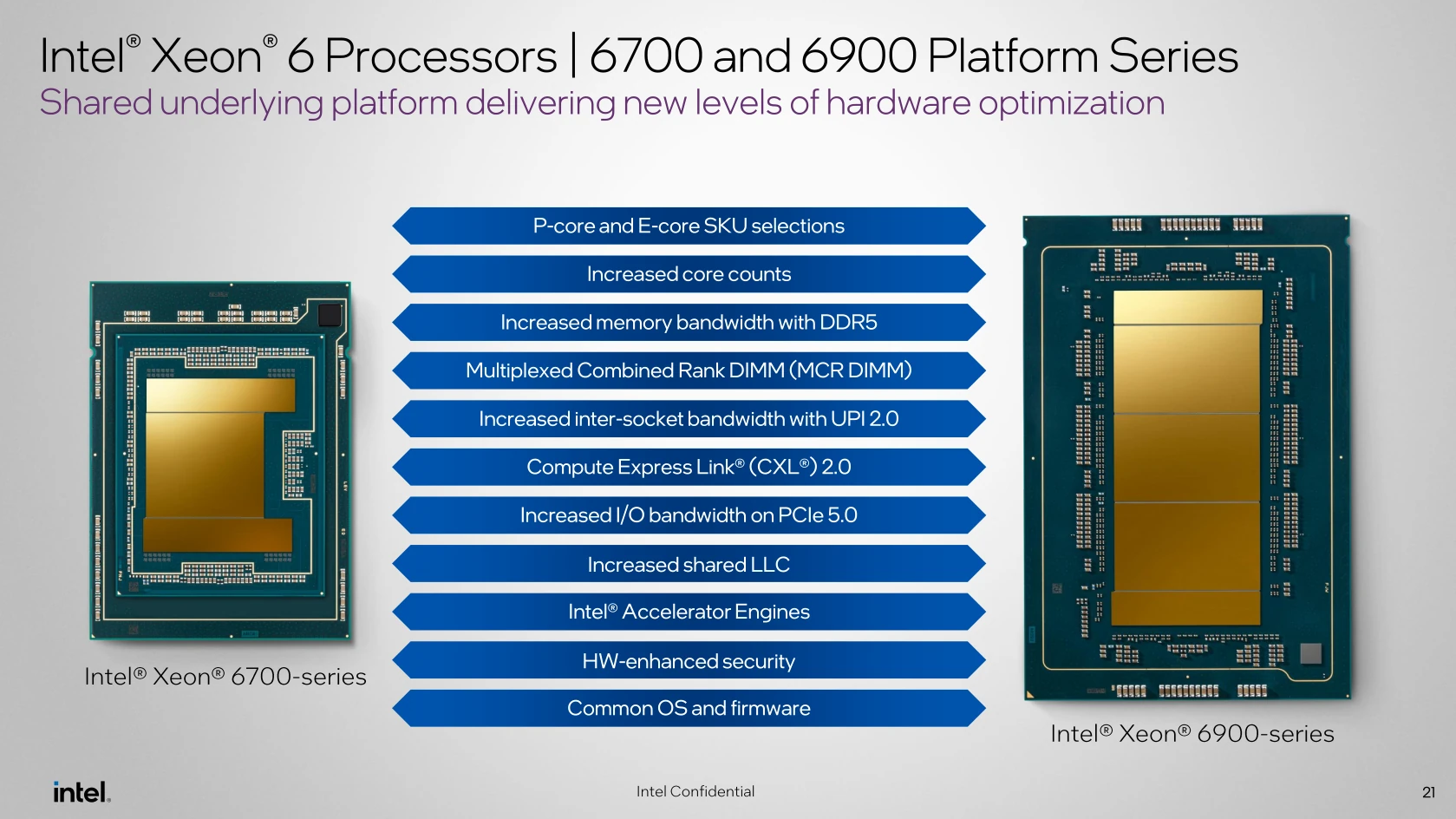

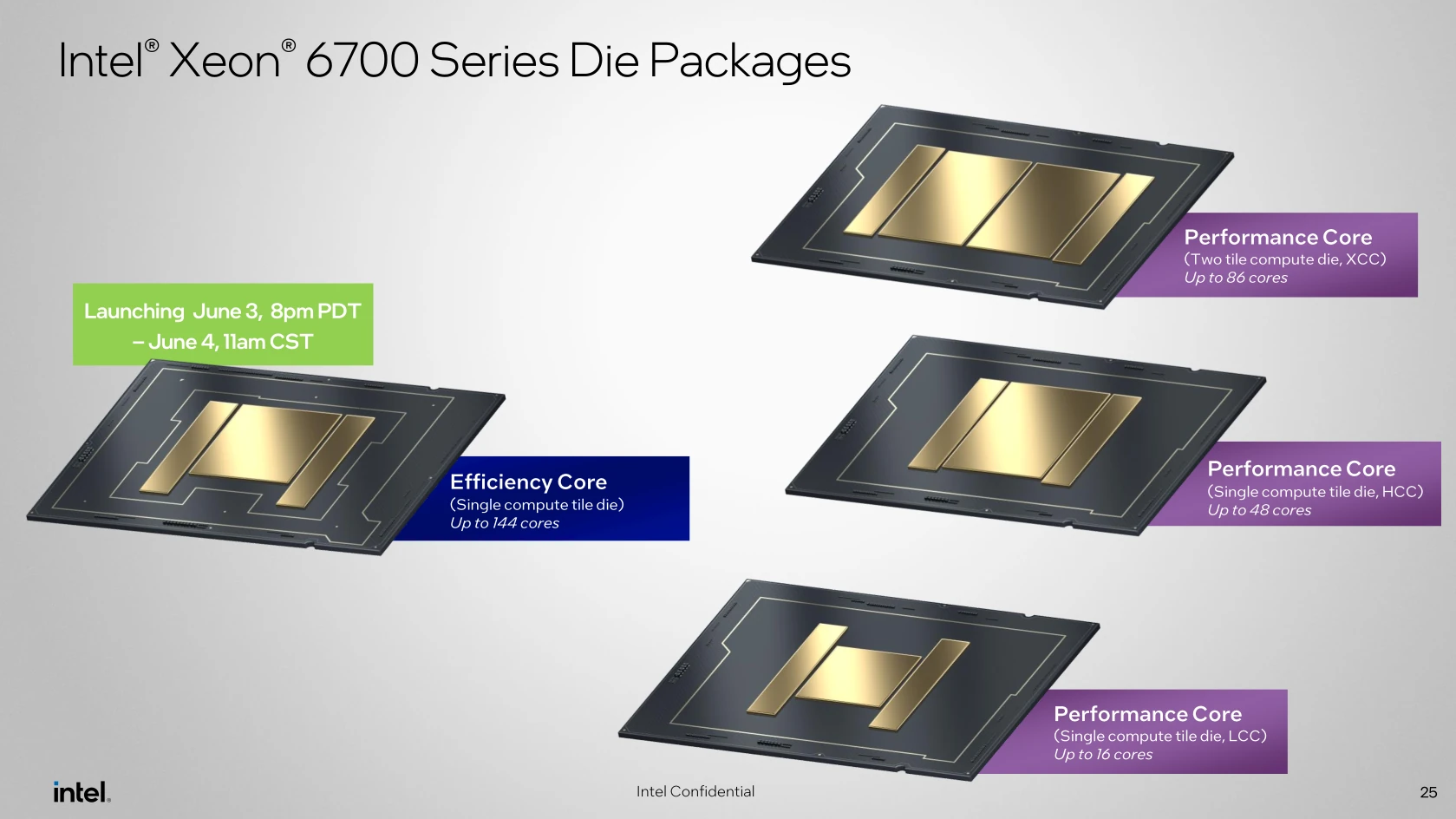

Pour cela, Intel a repris la microarchitecture des E-Core de Meteor Lake, a sorti sa baguette magique, un coup d’EMIB et pouf ! Voici les Xeon 6700E et 6900E. Notez que des versions P-Core, les 6700P et 6900P, sont également en préparation, mais pas encore détaillées officiellement. Ces CPU rassemblant sur un interconnect en mesh et 1 (série Xeon 6700) ou 2 dies de calcul (série Xeon 6900), accompagné de 2 die d’IO, le tout pour intégrer tout un tas d’E-Core sous le même capot. Leur cible ? Les serveurs, via le socket LGA-4710 (Xeon 6700E, avec un maximum de 144 E-Core, ou 86 P-Core sur la version 6700P dans un TDP de 350 W) et LGA-7529 (Xeon 6900E et 288 E-Core, ou 128 P-Core pour les 6900P, et un TDP de 500 W). Un socket qui est par ailleurs partagé avec les 6700P et 6900P, eux-mêmes équipé des cœurs performances : en cas de regret ou de besoin, les datacenter pourront être mis à jour sans avoir à racheter toutes les lames. Une fonctionnalité bienvenue, mais sur laquelle nous doutons de son utilisation en pratique étant données les habitudes sur datacenter. Rajoutez un bon tas d’interconnexion (CXL 2,0, PCIe 5.0, DDR5) et voilà le travail !

Notez que, si le géant bleu est tout content d’annoncer « son premier Xeon à base d’E-Core », il ne s’agit toutefois pas du premier processeur basé sur les architectures -mont. En effet, les années 2010 avaient vu Intel tenter d’entrer sur le marché des GPGPU avec une solution à base d’Atom culminant à un maximum de 72 cœurs. Cependant, la difficulté de programmation du bousin du fait d’une interconnexion en double ring peu efficace et les performances single-core anémiques — en dépit de la présence d’AVX-512 — en faisaient une proposition mitigée par rapport aux CPU et GPU concurrent, si bien que la plateforme s’est arrêtée en 2020 dans le silence le plus total.

Cependant, nous ne pouvons nous empêcher d’émettre quelques doutes à la vue de certains de ces choix. Ou plutôt, une occasion manquée. Expliquons-nous : pour du machine learning, les programmes se caractérisent par un code régulier, c’est-à-dire sur lequel la prédiction de branchement est particulièrement efficace de par la structure des calculs. L’idée d’un SoC type Xeon Phi — des cœurs efficients boostés à l’AVX-512 — est sur le papier une solution toute trouvée pour répondre à un besoin de mixité des tâches (assuré par le jeu d’instruction x86) et de machine learaning. Intel en a choisi autrement. Selon les concepteurs de cette gamme, le choix est assumé : greffer des unités vectorielles supplémentaires (comme l’a fait Skylake-X par rapport à Skylake) aurait nécessité de revoir une partie du sous-système mémoire pour les nourrir correctement. Pourtant, le pipeline vectoriel/flottant est un point faible de Skymont, comme nous vous l’expliquions dans notre dossier... et ces Xeons se basent sur Crestmont la génération précédente ! De plus, rajouter des unités aurait été de pair avec l’agrandissement de la taille des cœurs, et donc la réduction de leur nombre maximum. Une contrainte qui n’a visiblement pas plus au fondeur de Santa Clara, et qui a donc abouti à la gamme actuelle !

attention c'est les core e de metor lake pas ceux de lunar lake / arrow lake avec leurs grosse hausse d'ipc

a l'annonce des remplaçant de se xeon la gen clearwater forest je en comprenais pas pourquoi intel ne faisait pas évoluer le nombre de core mais au vu de l'énorme hausse d'ipc le nombre de transistor doit être en nette hausse

Bien vu, j'ai édité en ce sens :-)

bah oui mais non tu as inversé c'est pas skymont de lunar lake c'est cresmont de metor lake et clearwater forest aura les e core de panther lake qui tout les 2 seront en 18a

J'ai surtout mal enregistré ma modification, cette fois-ci, c'est la bonne ! 🙏

😅