Nous avons déjà un peu effleuré le sujet de la CUDIMM l’autre jour. Et nous allons continuer à le faire aujourd’hui, en faisant un maximum avec le peu de détails finalement disponibles à ce jour. Pourtant, le Clocked Unbuffered Dual Inline Memory Module a été standardisé par le JEDEC en décembre 2023, dans un document officiellement publié et libre d’accès depuis janvier dernier. Il en est d’ailleurs de même pour le CSODIMM, ou Clocked Small Outline Dual Inline Memory Module .

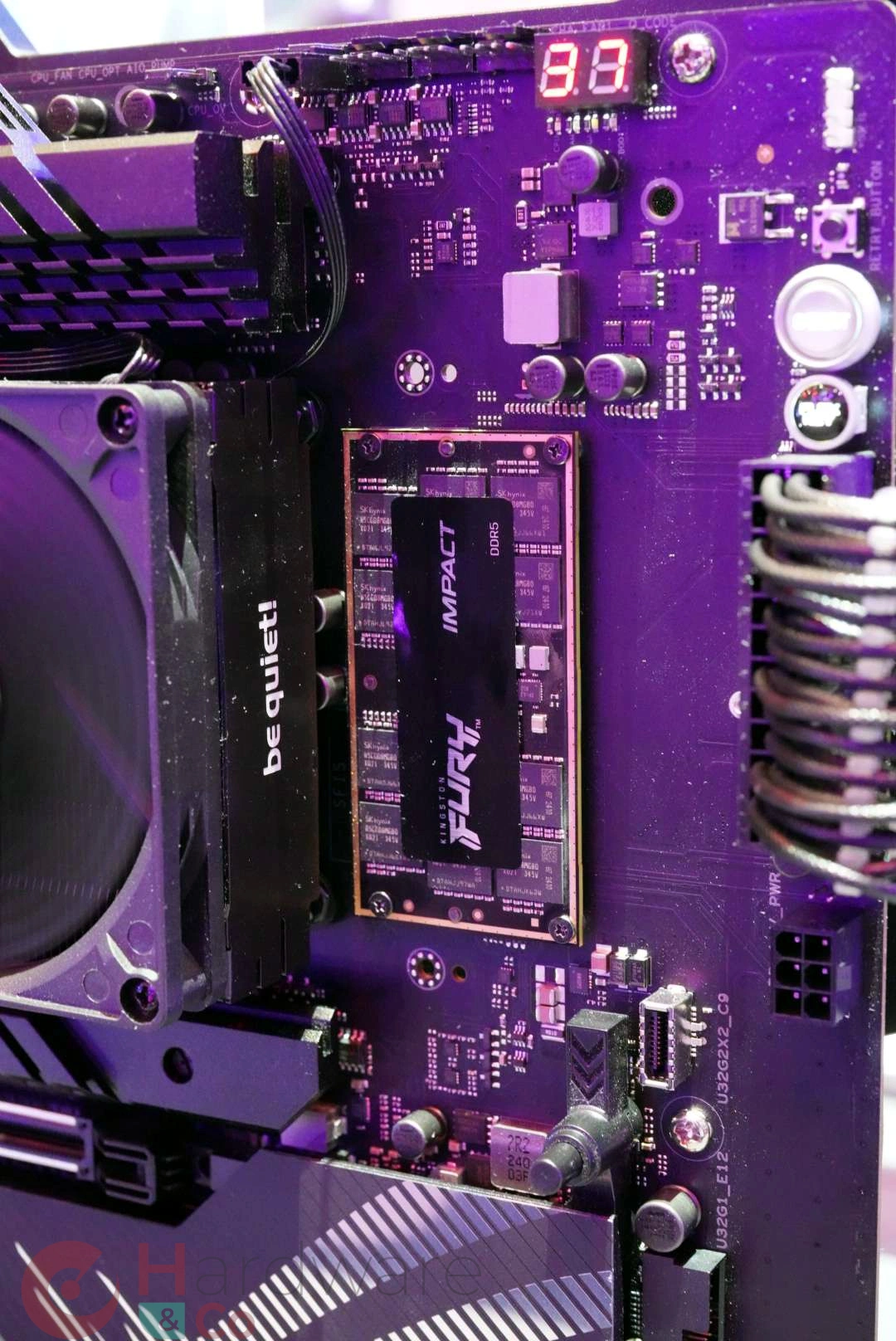

Après une plongée dans les spécifications disponibles pour l’un et pour l’autre, nous pouvons confirmer que le nombre de pins et leur attribution sont parfaitement identiques entre CUDIMM et UDIMM (la mémoire vive du grand public côté desktop), ainsi qu’entre CSODIMM et SODIMM (la même, mais pour le mobile). En fait, toutes les spécifications principales sont les mêmes dans un cas comme dans l’autre, qu’il s’agisse de la topologie, les dimensions des modules, le support des puces DDR5, la plage de capacité, la tension, le PMIC, les températures de fonctionnement, etc. Bref, le standard DDR5 est virtuellement inchangé et par conséquent, le slot côté carte mère devrait être inchangé aussi. En tout cas, à vue d’œil, c’est exactement la même chose !

vs

On a même compté le nombre de pins de part et d’autre du détrompeur ! C’est bien la même répartition.

La grande différence, c’est que ce n’est plus le contrôleur mémoire du CPU qui dictera l’horloge du signal de la mémoire, mais une nouvelle puce CKD (Client Clock Driver ou Pilote d’Horloge Client) intégrée à chaque module ! Son rôle sera de mettre le signal d’horloge en provenance du contrôleur en mémoire tampon et de le piloter directement. Ceci permettra en retour d’améliorer l’intégrité du signal et sa fiabilité. C’est en fait un fonctionnement déjà présent depuis longtemps dans le Register Clock Driver (RCD) de la mémoire RDIMM (Registered Dual Inline Memory Module) que l’on trouve toutefois surtout dans les serveurs. Mais avec la progression des débits de la DDR5 et donc l’augmentation du signal d’horloge, l’intégrité de celui-ci devient de plus en plus difficile à tenir. Ainsi, pour pouvoir continuer leur montée en vitesse l’esprit tranquille et répondre aux besoins sans cesse croissants, UDIMM et SODIMM doivent maintenant évoluer en CUDIMM et CSODIMM !

En réalité, c’est une évolution en gestation depuis au moins deux ans. En 2022 et en 2023, des constructeurs de puces et de mémoire - comme Montage Technology et TeamGroup - parlaient déjà du Pilote d’Horloge pour la DDR5 des PC. C’est donc l’aboutissement de ce travail.

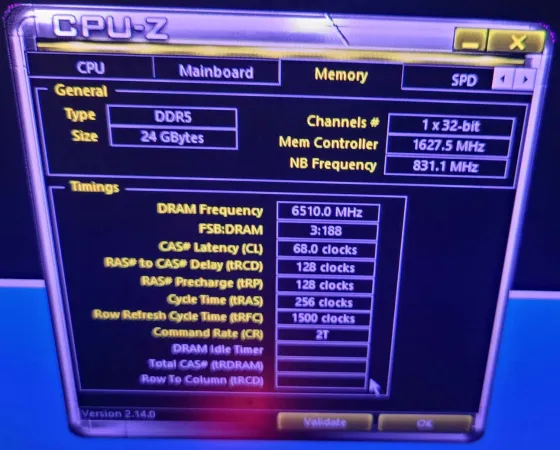

Il faudrait dans un premier temps s’attendre à des modules de capacité 16 et 32 Go, de 6400 MT/s à 8800 MT/s, de CL52 à CL64, ce qui correspond grosso modo aux spécifications ajoutées par le JEDEC en avril dernier. Bien entendu, rien ne devrait empêcher les fabricants d’aller confortablement au-delà des normes du JEDEC comme ils le font déjà. Vers les 9000 MT/s et même au-delà, puisque certains ont déjà montré des débits supérieurs à 10 000 MT/s. Se posera ensuite la question de la compatibilité. Si physiquement l’installation pourrait être possible, va-t-on pouvoir faire fonctionner de la CUDIMM sur une carte mère DDR5 actuelle le cas échéant ? Mystère. Est-ce que la compatibilité dépendra du contrôleur mémoire du CPU ? Ou ne serait-ce qu'une question de mise à jour du BIOS/UEFI ?

La CUDIMM est actuellement planifiée pour septembre 2024, ce qui colle avec la période de lancement d’Arrow Lake chez Intel. Nous pouvons en déduire que la 15ᵉ génération Core serait donc d'emblée compatible. Comme mentionné l’autre jour, l’adoption de cette DDR5 "next-gen" ne serait pas encore à l’ordre du jour chez AMD. Accessoirement, interrogation aussi quant à la carte mère Mini-CUDIMM montrée par MSI, une soi-disant exclusivité pour Intel. Mais de toute évidence, c’est un prototype ATX simplement équipé de slots CSODIMM.

Bon, et CAMM2 dans tout ça ? De l’aveu des fabricants, le format va définitivement arriver sur laptop/notebook, et est bien destiné à s’y démocratiser et envoyer la SODIMM à la retraite (donc pas de CSODIMM sur ce segment ?). En revanche, CAMM2 pour desktop relèverait pour l’instant plus de l’expérimentation. Oui, plusieurs fabricants ont montré des cartes mères (essentiellement Intel) équipées d’un module DDR5 CAMM2, c’est le cas d’ASUS (ci-dessus), d’ASRock et de MSI. Mais, GIGABYTE par exemple, n’en a pas présenté. Les modèles dévoilés sont a priori pour certains au moins prévus pour être commercialisés également en septembre - le début de la phase bêta en somme.

Apparemment, l’idée générale serait de tremper un doigt pour prendre la température auprès des clients (nous, entre autres). Si l’affaire ne devrait pas être trop compliquée pour CUDIMM, l’avenir de CAMM2 sur desktop dépendrait dans l’immédiat surtout des réactions du public et du niveau d’adoption. On devine qu’il y aura donc bientôt match entre CAMM2 et CUDIMM, en sachant que CAMM2 n’a pas de CKD (pour l’instant) parmi ses atouts !

En conclusion, la fin de l’été promet d’être très intéressante !

Il serait temps que les constructeurs arrêtent leur bêtises et passer à la ReRAM qu'ils ont dans les cartons depuis bien longtemps, au lieu de faire du des formats technologiquement dépassés...

On a la fusion nucléaire dans les cartons depuis un moment et on utilise toujours des technologies dépassée, il y a un monde entre une expérience et de la production commerciale.

Et la ReRAM, étant de la mémoire non volatile, ce n'est pas plus pour du stockage et les SSD à la base ?

Il y avait une ambition que cela remplace aussi la RAM, en étant plus perf que cette dernière aussi. Peut-être que cette ambition a été revue à la baisse suite aux évolutions de la RAM depuis les essais prototypiques et effets d'annonce du début des années 2010.

https://semiengineering.com/what-happened-to-reram/

Si je comprends bien, c'est quand même une affaire assez complexe.

Certainement, à développer et ensuite trouver un moyen d'en faire une production à grande échelle hors labo. Mais je pense qu'au départ, ils ont réellement cru tenir leur graal avec un machin qui pourrait tout faire en mieux au vu des annonces initiales.

Intégrer l'horloge au niveau des barrettes, ils n'y auraient pas pu y penser avant, au début de la définition de la DDR5, en même temps qu'il y ont déporté le module d'alimentation? Plutôt que de foutre le bordel en plein milieu de l'ère DDR5? Maintenant il serait plus judicieux que ça reste de l'expérimentation et attendre la DDR6 pour éventuellement démocratiser cela.

Pourquoi augmenter les coûts de production en y ajoutant un truc pas encore nécessaire ?

Le régulateur, à l'origine de pénurie au tout début des premières barrettes DDR5, c'était vraiment nécessaire ou bien un caprice d'ingénieur?

Je ne suis pas ingénieur, mais a priori oui : meilleure alimentation, plus précise et au plus proche des composants à alimenter, plus besoin de concevoir la carte mère avec les composants d'alimentation requis pour gérer 4 modules...

https://semiengineering.com/ddr5-pmics-enable-smarter-power-efficient-memory-modules/

Je crois qu'on peut réutiliser à peu près les mêmes arguments pour l'horloge... Meilleur ne veut pas dire indispensable.