Après un bon étalage technologie sur le DLVR, voilà qu’Intel nous comble de nouvelles informations avec une piqûre de rappel sur la MRDIMM. Késako ? Une mémoire haute performance compatible avec les Xeon afin de rassasier ses cœurs en manque de bande passante, le tout sans passer par une multiplication du nombre de canal (et donc une complexification du SoC), que le JEDEC a officialisé en juillet dernier. Comment tout cela fonctionne-t-il ? Hardware & Co vous explique tout !

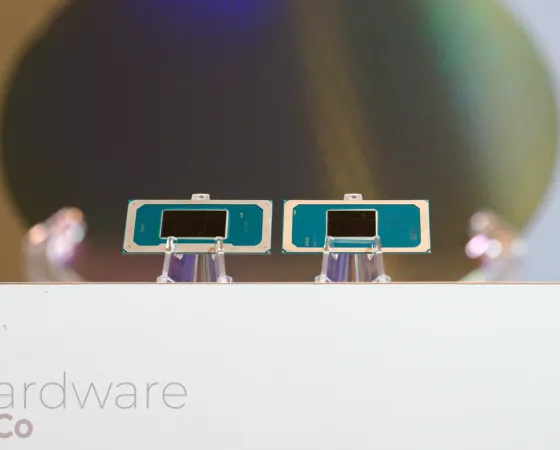

Et non, ce n’est pas un Photoshop à deux balles, promis !

Une barrette de RAM — de la DDR5 par exemple — se compose de plusieurs puces de mémoire, chacune apportant une capacité fixe à la barrette. Par exemple, sur ce kit de RIPJAWS S5 de chez G.Skill testé par Guillaume, 16 puces de 2 Gio sont intégrées sur chaque module (8 sur chaque face), pour un total de 32 Gio. Mais tout n’est pas si simple, car ces puces peuvent également être organisées en rank : des groupes — usuellement un ou deux, mais pouvant monter jusqu’à 4 sur serveurs — capables de fonctionner indépendamment les uns des autres. Typiquement, l’un est en train de charger une valeur, quand l’autre effectue un rafraîchissement. Si la fonctionnalité était particulièrement utile sur de la DDR4 pour optimiser les performances, la DDR5 est moins friande de la technologie du fait de la découpe des canaux de 64-bit en sous-canaux de 32-bits, permettant des gains similaires mème en single-rank.

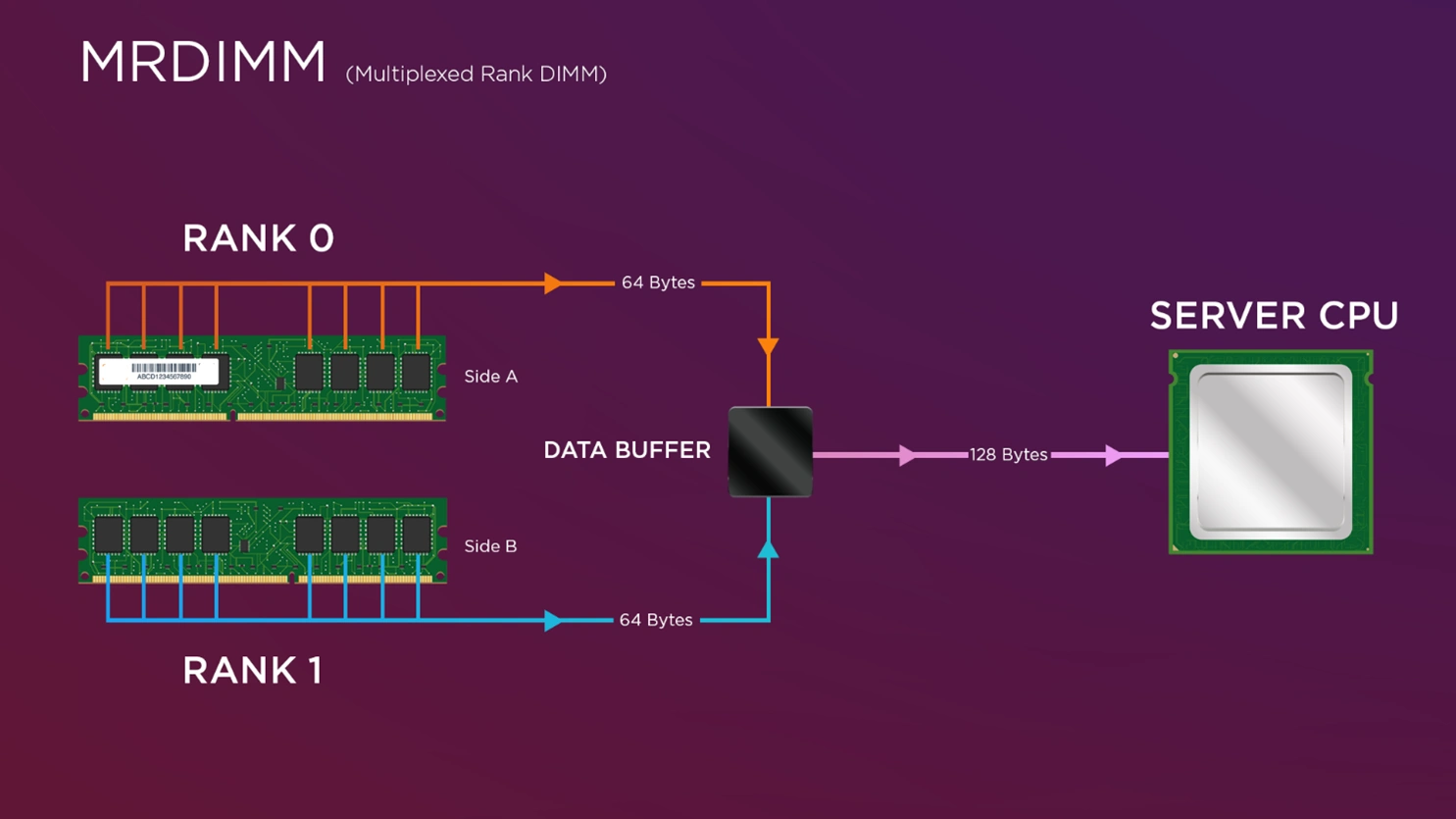

Il y avait là matière à optimiser : pourquoi donc ne pas directement utiliser plusieurs ranks en parallèle, et ainsi doubler le débit (en théorie, tout du moins) ? Voilà la naissance de la MRDIMM, pour Multiplexed Rank DIMM. Comme son nom l’indique, ce type de DDR5 fait appel à un composant supplémentaire pour paralléliser les accès : un data buffer ; ce qui a pour inconvénient d’augmenter le coût du bousin… ainsi que sa consommation par rapport à une barrette normale (donc de capacité moindre, attention !). En revanche, Intel communique sur des gains allant jusqu’à 33 % sur les applications utilisant la mémoire de manière intensive. Un chiffre qui n’est guère surprenant, puisque le nombre de cœurs et leurs performances (et donc la puissance de calcul des CPU) ont évolué plus rapidement que la bande passante mémoire.

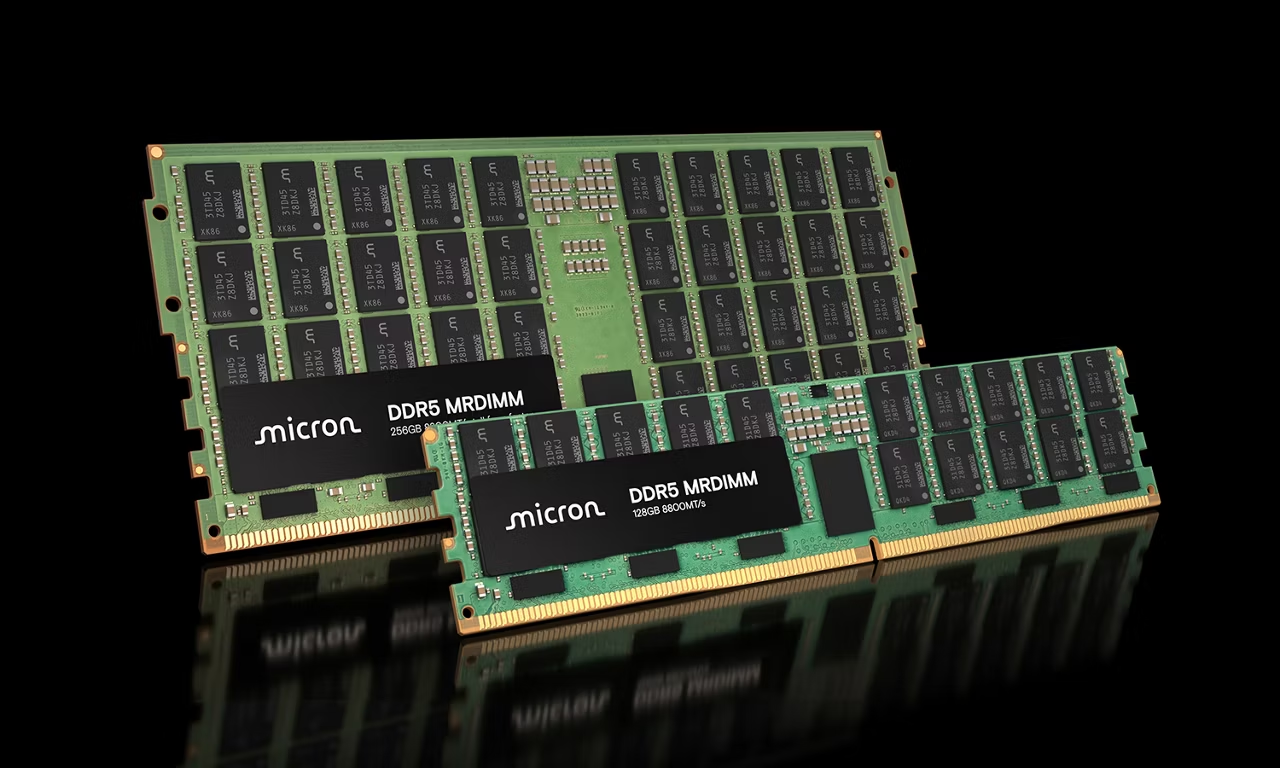

Évidemment, ces modules ne sont pour le moment compatibles qu’avec les processeurs Xeon 6 version P-Core d’Intel, mais il se pourrait bien que la concurrence d’AMD s’aligne dans le futur, d’autant plus qu’un projet similaire côté rouge avait fait parler de lui en 2023. En attendant, les vitesses restent sages avec "seulement" 8800 MT/s (2200 MHz, multipliés par deux transferts par cycle, multiplié par deux ranks maximum), pour une capacité montant jusqu’à 256 Gio par barrette. Décoiffant ! Dans le futur (comprendre, vers 2030), la MRDIMM est planifiée pour monter jusqu’à 17 600 MT/s : une promesse ô combien prometteuse !

c'est possible de cumuler mrdimm et cudimm ?

comme ça 10 voir 10.6 gbps sans oc

Dansa théorie je ne vois pas pourquoi ce serair impossible, mais je suis suis pas électronicien. Il faut aussi voir le coût de R&D, d'integration face auel gain procuré... Pas sur que CEMA arrive de sitôt, surtout vu que la MRDIMM se limite aux serveurs (pour le moment en tout cas).