Sur Arrow Lake, Intel a introduit une nouvelle technologie de gestion de l’alimentation : le DLVR (Digital Linear Voltage Regulator), et la possibilité de l’outrepasser (bypass) pour favoriser la montée en cadence via une option nommée power gating mode. Dans les grandes lignes (détaillé en 2021 dans un brevet), le DLVR permet d’activer si besoin une alimentation auxiliaire au CPU afin de stabiliser sa tension, et était censé arriver sur Raptor Lake avant d’être abandonné à la dernière minute. Comment passe-t-on de cela à une réduction (ou une augmentation) de la consommation globale ? Sortez les neurones, H&Co vous explique tout ça !

Tout d’abord, commençons par quelques notions d’électroniques. Un CPU, comme tout composant, consomme du courant, qui lui est fourni par l’alimentation ; plus précisément, par les VRM (modules de régulation de tension) de la carte mère. Ces VRM sont pilotées par les phases d’alimentation des mobales, leur nombre étant un des indicateurs de la robustesse de la carte côté alimentation. Cependant, ces VRM sont imparfaits : comme tout système d’alimentation de courant, elles possèdent une impédance, c’est-à-dire que la tension de sortie décroît avec le courant fourni (ici la charge imposée par le processeur). Comprenez que plus le CPU consomme, moins les VRM lui donnent de tension. Pour contrer cela, les processeurs intègrent un module FIVR (Fully Integrated Voltage Regulator), un composant présent dans le silicium pour réguler la tension en aval de la carte mère, permettant de spécifier plus finement les tensions données aux CPU depuis le BIOS.

Mais l’histoire se répète : ces FIVR ne sont pas parfaits non plus, si bien que pour une tension consigne VID, un cœur verra une tension réelle réduite de VOFFSET. Pire, en charge, la tension diminue encore d’un montant nommé VDROOP. Et — encore pire — lors des changements brutaux de consommation (par exemple, passer du bureau à une petite partie d’Europa Universalis ou à un encodage vidéo), le courant demandé évolue de faible à maximal en une poignée de microsecondes, ce qui génère des oscillations de la tension pendant un régime transitoire (des vagues sur notre schéma ci-dessous). Encore une fois, cela est causé par notre couple VRM/FIVR imparfait ; un phénomène qui est même accentué par leur spécialisation. Comprenez qu’une alimentation optimisée pour avoir un bon rendement (donc moins consommer) à pleine charge va entraîner un régime transitoire long et instable, là où une alimentation calibrée pour des régimes transitoires stables se retrouve moins efficiente sur des utilisations prolongées.

Avec un graphique, c’est (un peu) plus clair

Jusqu’alors, la solution était simple : optimiser les VRM pour peu chauffer sous forte charge, et compenser les oscillations (fortes) lors des changements de ladite charge en appliquant une tension de compensation supplémentaire (survolter, quoi !). Cela assure que la tension des cœurs du CPU ne tombe jamais en dessous de son seuil critique, appelée tension requise sur notre illustration. Le souci dans tout ça ? Cette compensation est présente quelle que soit la charge. Ainsi, au repos, le CPU est goinfré par bien plus de volts que ce qu’il requiert, entraînant une chauffe et une consommation inutile. C’est là que notre DLVR entre en jeu : mis en parallèle du couple VRM/FIVR, le nouveau venu (alimenté par le rail VccIA, pour les curieux) optimise l'alimentation lors des changements de charge en limitant les oscillations.

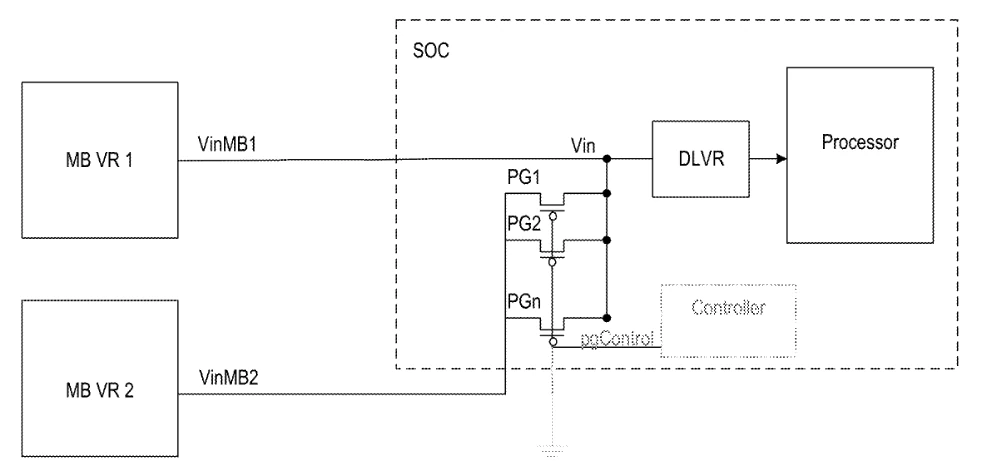

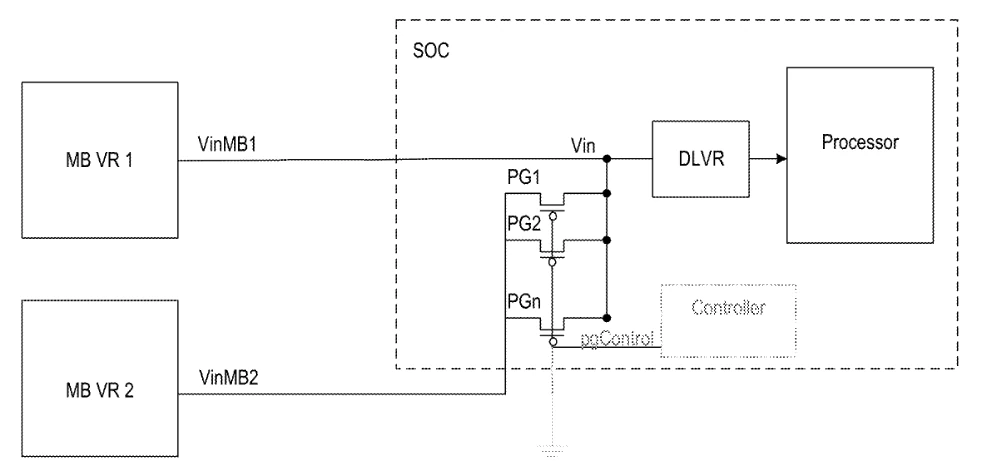

Notre DLVR en place, qui alimente une partie du processeur (ici à partir de deux sources de tension)

Pour les plus férus de détails techniques, chaque cœur est muni d’un régulateur de tension linéaire à commande numérique. Selon le brevet de la firme, ce dernier peut être utilisé comme une alimentation auxiliaire et déconnecté lors des faibles charges, mais rien ne nous permet d'affirmer qu'un tel mécanisme soit utilisé sur Arrow Lake. Grâce à ce composant, la tension de compensation est réduite (puisque l’amplitude des oscillations l’est), ce qui réduit mécaniquement la consommation... au repos tout du moins. En charge, par contre, tout dépend de l’intensité de courants : étant optimisé pour les régimes transitoires, le DLVR se retrouve moins performant dans sa capacité à fournir du jus d’électron. Dans le cas de très gros OC, le rendement du DLVR peut devenir moins bon que le gain apporté par la diminution de la tension de compensation : il est alors bénéfique de le désactiver — voilà notre Power Gating Mode ! Notez que le DLVR est un composant gérant l’alimentation à la granularité du cœur (ou du cluster dans le cas des E-Cores), rejoignant AMD à ce niveau qui intégrait cette technologie sur les Zen 3 avec le Precision Boost Override 2 (PBO2).

Tout cela est bien beau, mais quel est le rapport avec l’actualité, vous diriez-nous ? Avec le microcode 0x112, Intel a retiré cette désactivation du DLVR, officiellement pour éviter une mauvaise utilisation du bouzin par des utilisateurs non-initiés. En revanche, l’option restera accessible pour les overclockers extrêmes — comprendre « sous température négative » (c’est-à-dire à l’aide d’azote liquide), nous imaginons à l’aide d’un BIOS dédié où une option désactivant la quasi-intégralité des sécurités du CPU. De quoi sérieusement rebuter les clockers amateurs soucieux de conserver un processeur en bon état ! Vu la marge d’overclocking disponible sur les générations actuelles, l’option ne manquera probablement pas à grand-monde, mais il est intrigant de voir le géant bleu forcer autant la main de ses utilisateurs. Un moyen de s’assurer les meilleures performances dans la majorité des cas d’usage (et donc des futurs tests) d’Arrow Lake ? (Source : HardwareLuXX)

👌👍