Comme tous les ans, la conférence internationale phare concernant la recherche en technologie de gravure et autres machines à transmettre des électrons rapidement, plus communément appelée IEDM se tient à San Francisco. Intel, en sa qualité de fondeur — et malgré ses difficultés actuelles en la matière — est bien là une année supplémentaire pour montrer les possibles futurs du transistor. Car pendant que certains sont occupés à chercher un nouveau décisionnaire, d’autres doivent bien s’occuper des progrès côté manufacture, qui, à ce niveau-là de technicités, sont loin d’être évident à saisir. Pas de panique, Hardware & Co est là pour vous déchiffrer tout cela !

Des nouveautés sur le packaging

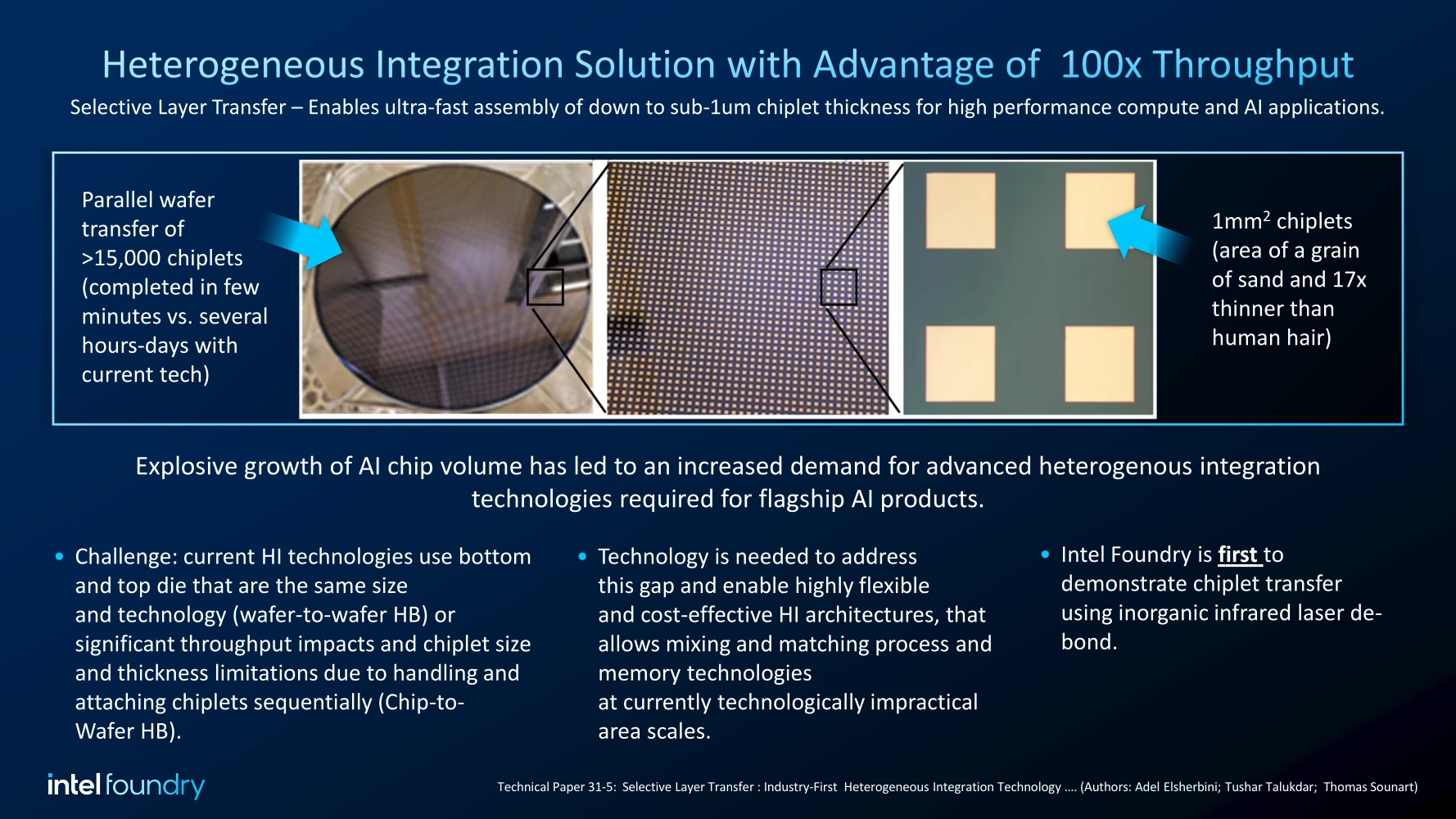

Une des dernières étapes de la réalisation des CPU Lunar Lake et Arrow Lake encore fait maison chez Intel est celle de packaging, c’est-à-dire l’art consistant à relier ensemble plusieurs dies de silicium avec le PCB (nommé substrat dans ce cas-là). Avec Foveros, les bleus ont toutes les cartes pour empiler des transistors dans tous les sens… à condition de bien gérer la dissipation thermique. Dans le premier papier du jour, Intel propose une méthode capable de faciliter l’intégration de cette technologie dans des produits finis en utilisant un procédé nommé Selective Layer Transfer. À l’heure actuelle, il est possible soit de coller deux wafers l’un sur l’autre — à condition, du coup, que les deux dies à assembler soient de même dimension — de manière relativement efficace (wafer-to-wafer hybrid bonding), ou de coller un à un des dies déjà découpés à un wafer (chip-to-wafer hybrid bonding), imposants des contraintes fortes en ce qui concerne l’épaisseur des puces tout en étant affreusement lent (plusieurs jours dans le pire cas).

Désormais, il est possible d’utiliser une méthode se basant sur des lasers infrarouges afin d’attacher ensemble deux wafers, mais pouvoir choisir de manière sélective quel die attacher ou non, combinant le meilleur des deux mondes. Notez que cette technologie a également l’avantage d’être fonctionnelle sur des toutes petites puces (1 mm² de surface pour moins d’1 µm d’épaisseur), ce qui la rend particulièrement adaptée pour des accélérateurs basse consommation embarqués — qui a parlé d’IA et d’IoT ? Selon les dires de la firme, cette idée pourrait très rapidement trouver écho dans l’industrie, à la manière des PowerVia du futur 18A (une affirmation qui reste déjà à démontrer !).

Des transistors toujours plus fins

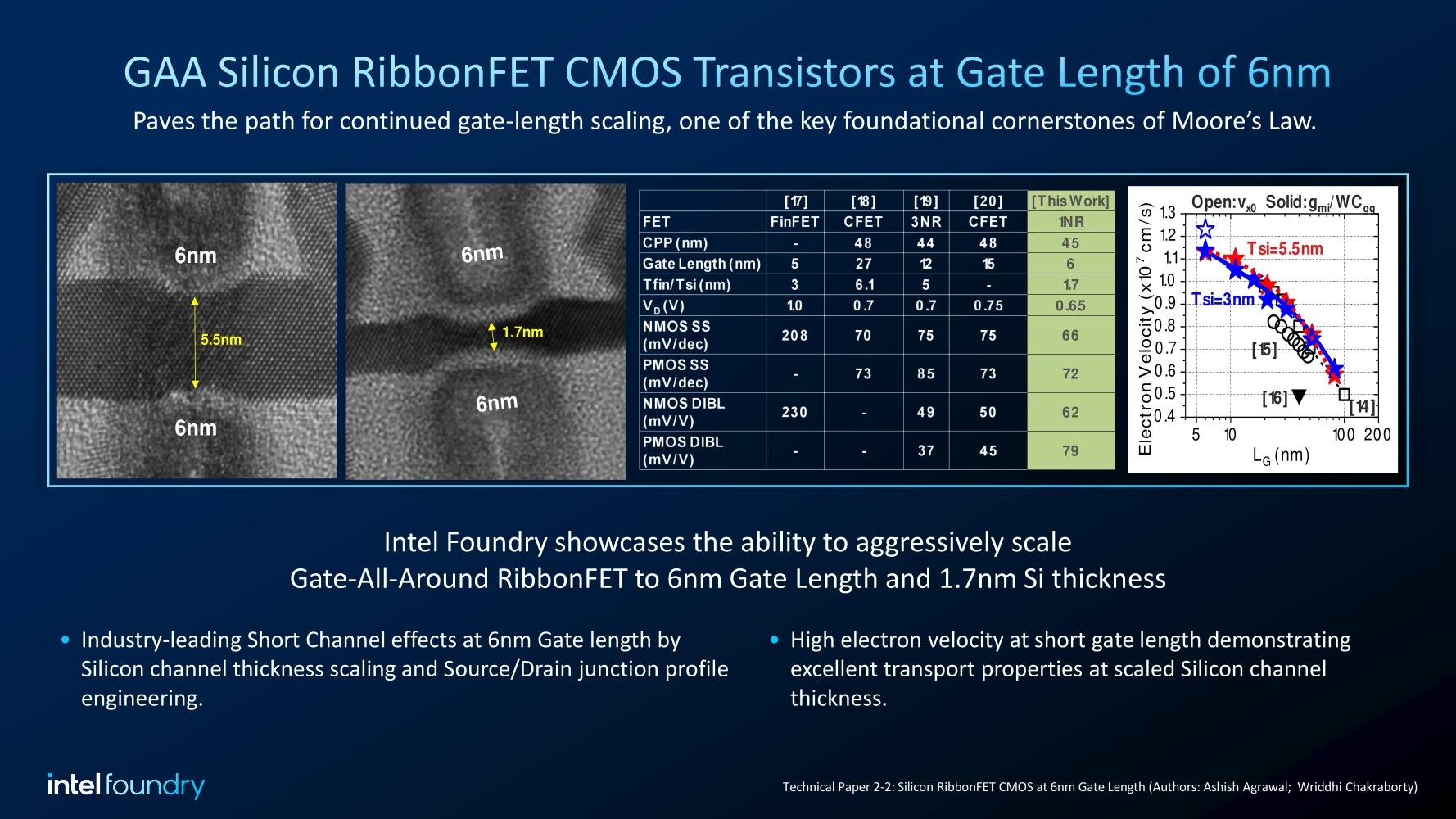

Le packaging est certes excitant, mais rien ne remplace un bon vieux transistor ! Ainsi, Intel continue d’innover pour chercher davantage de densité dans ses procédés. Avec le 18A, Intel introduit la technologie GAAFET (ou RibbonFET) consistant à empiler plusieurs fines couches de silicium. Dans les labos, les recherches se sont multipliées pour perfectionner la chose, et Intel est très heureux de présenter ses meilleurs résultats : une réduction de la taille de la gate à 6 nm (comprendre, de l’empilement), et de l’épaisseur des nanofeuilles de silicium de 1,7 nm ; le tout dans un état stable et fonctionnel. De quoi offrir les habituelles diminutions de la consommation et augmentation de la densité : bref, un procédé de gravure kikil est mieux que le précédent ! Si jamais vous cherchez un lien entre ces dimensions et les appellations de 5 nm, 3 nm ou encore 1,8 nm (conversion depuis les 18 Å), ne cherchez pas plus loin : les noms des procédés ne correspondent plus à des dimensions réelles depuis le 22 nm au plus tard, mais sont censés refléter les progrès obtenus (au moyen de structures alambiquées qui forment les transistors actuels) une fois rapportés à la métrique dimensionnelle des anciennes méthodes de gravure planaires… si vous croyez les fondeurs sur parole.

![]()

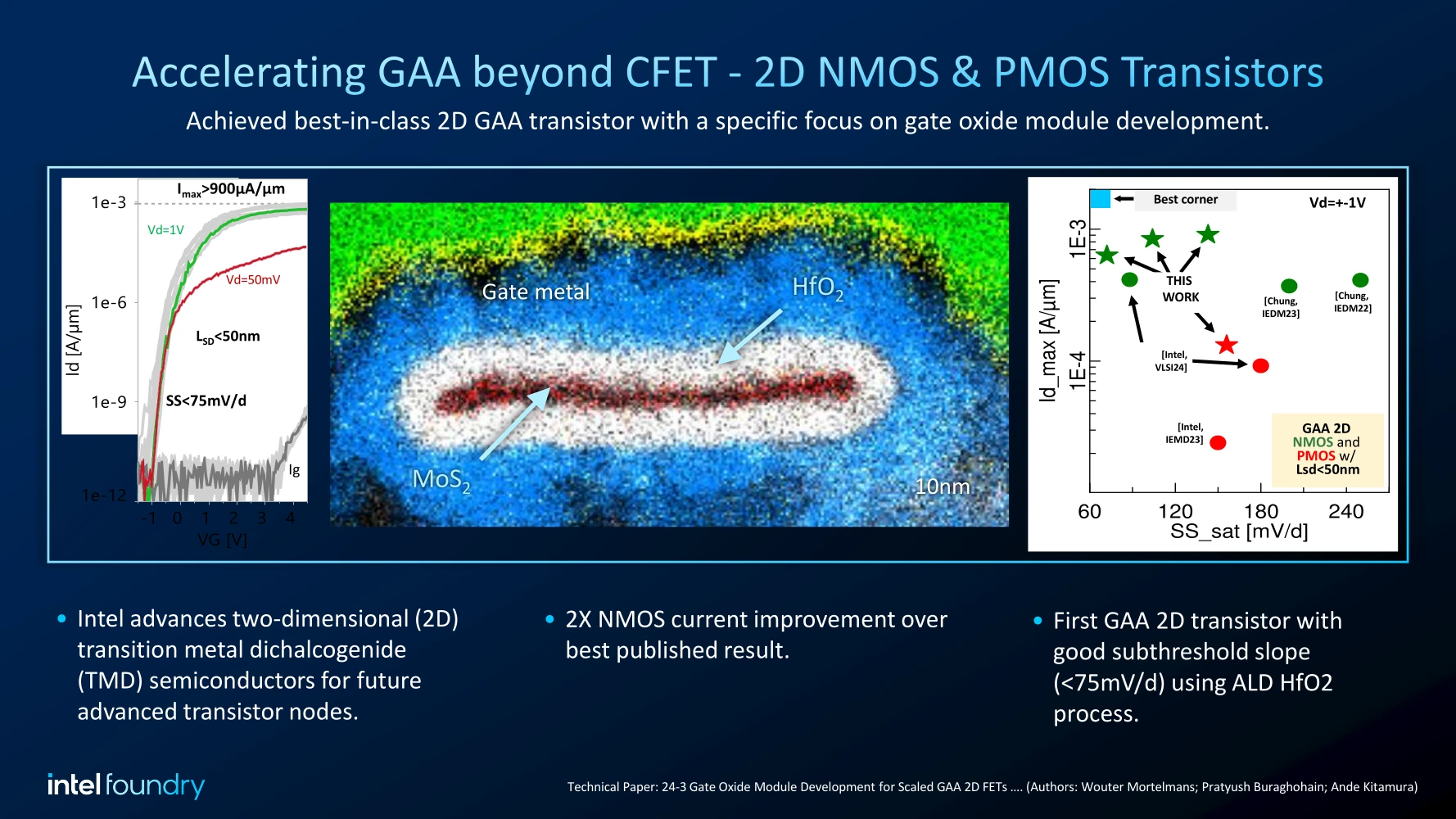

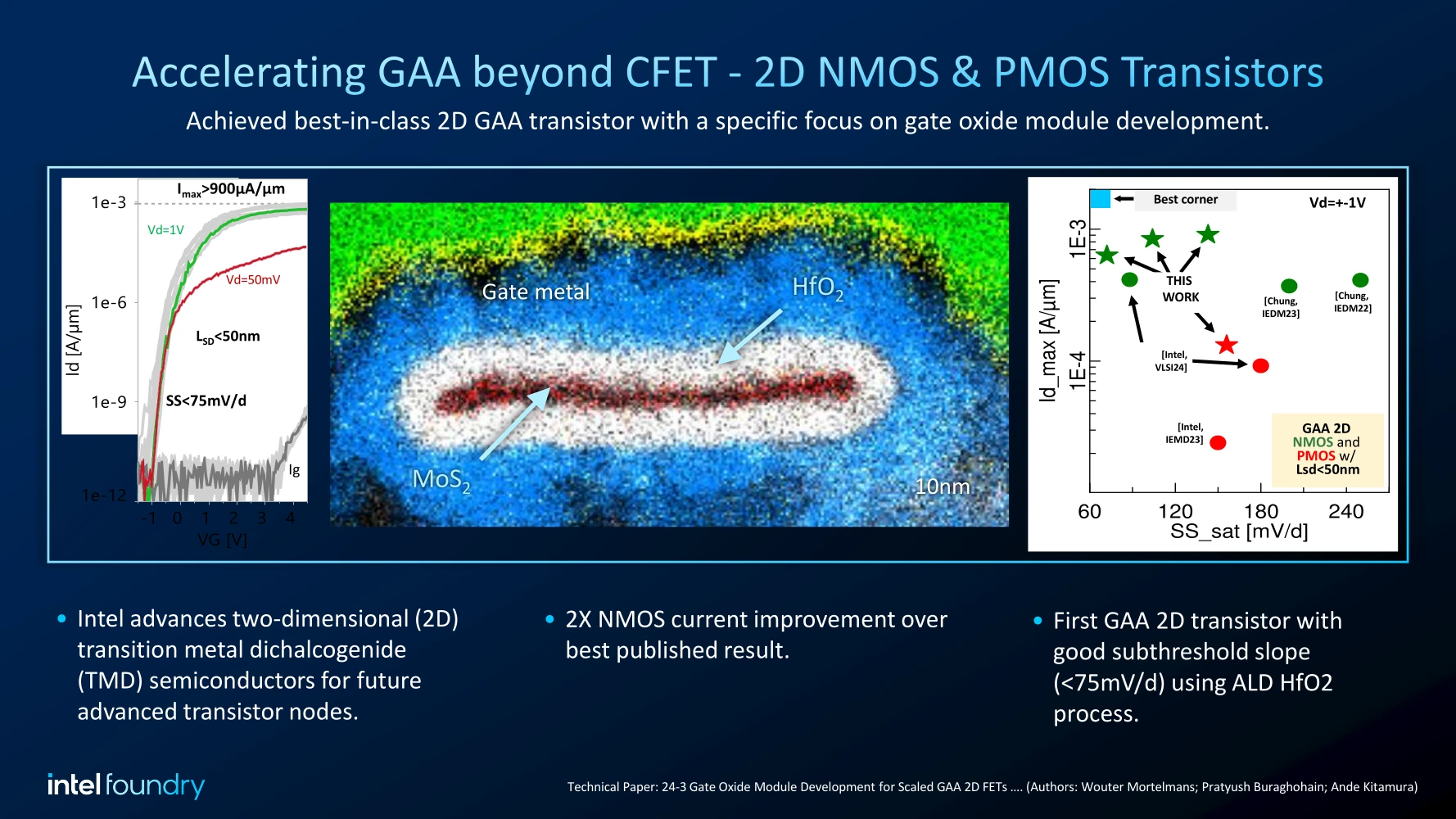

Toujours dans la série des transistors, Intel a également bossé sur le futur du GAAFET en remplaçant le silicium des channels (ces fameuses nanofeuilles formant le transistor gate-all-around) par une structure bidimensionnelle des matériaux : du disulfure de molybdène (MoSi2 pour les chimistes) entouré par de l’oxyde d’hafnium (HfO2), lui-même autour du métal « normal » de la gate. Encore une fois, la bataille ici est de fournir la courbe de réponse de réponse en intensité à la tension mise en entrée du transistor la plus propre, et le nouveau venu est l’un des meilleurs de sa catégorie. Rendez-vous dans une dizaine d’années pour savoir s’il aura fait son chemin jusqu’à la production de masse !

Un interconnect encore plus dense

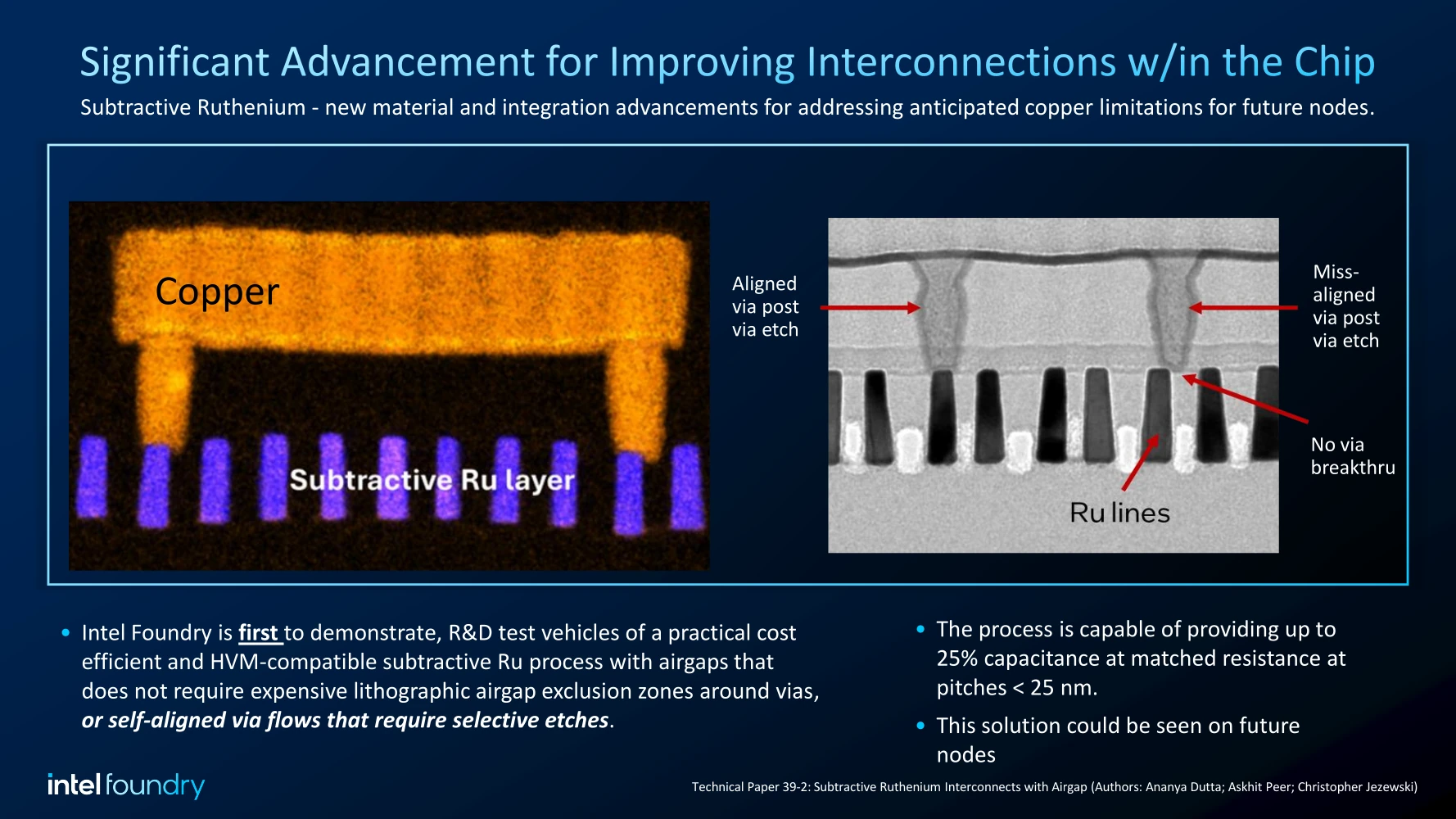

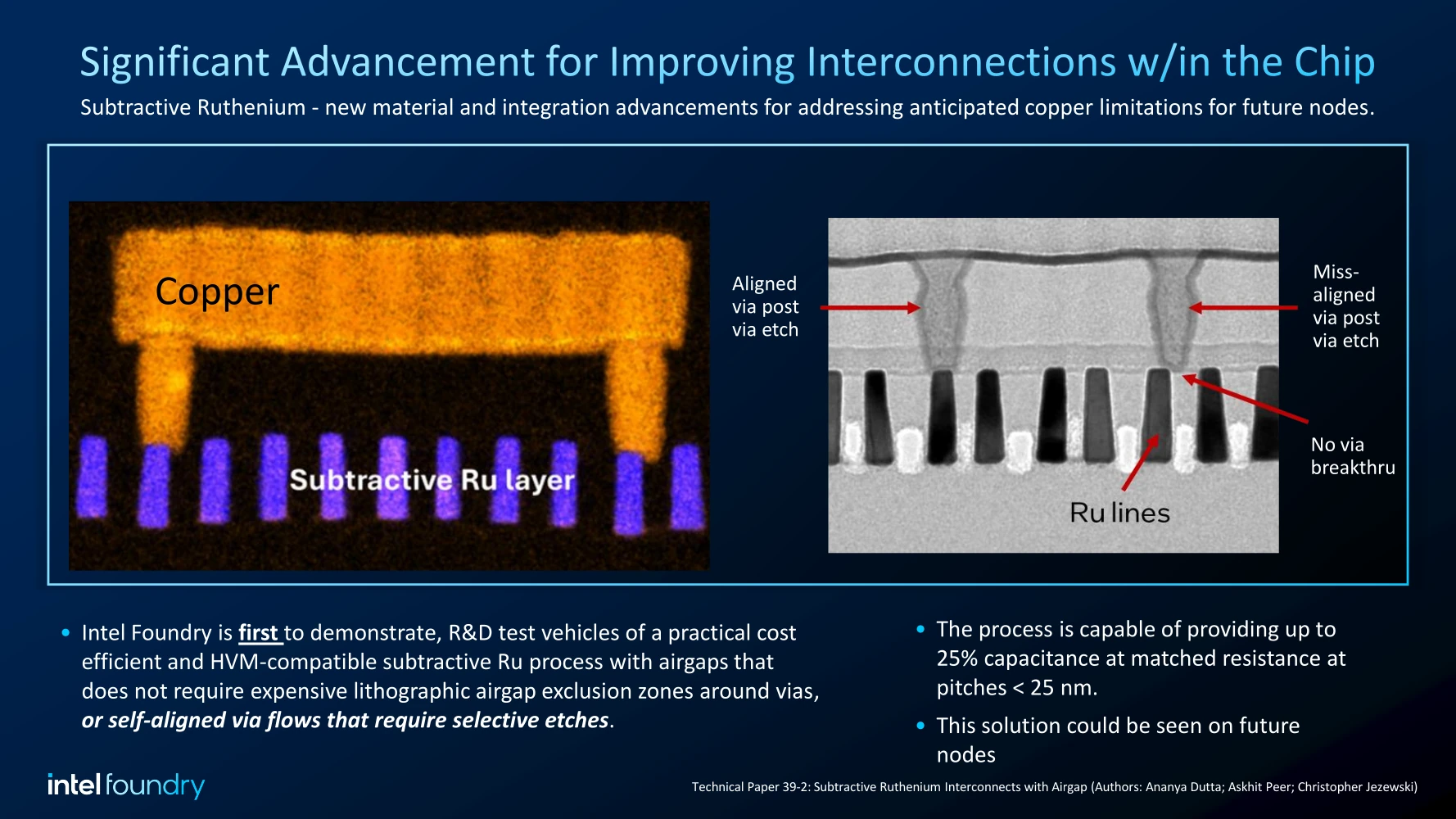

Enfin, à mi-chemin entre le packaging et les transistors se trouve les metal layers, ces couches de métal chargées de transporter des informations ou du courant entre les différents transistors. Pour le moment, le cuivre déposé par damascene demeure le matériau de prédilection pour cela, mais ce dernier montre ses limites lorsque les contraintes de tailles deviennent trop prononcées, notamment du fait d’une perte des propriétés de conductivité du courant devenant dominante sur des connexions trop fines et de la nécessité d'entourer le cuivre d'un autre métal barrière stoppant sa diffusion dans le silicium pour des questions de tenue dans le temps du die. À cela, il faut encore rajouter un métal intermédiaire nommé liner pour améliorer l'adhérence du cuivre au composé : un vrai casse-tête ! Dans ce travail, les ingénieurs bleus ont remplacé ce composé par du ruthénium, qui se trouve être aligné sans requérir de machinerie spécifique (comprendre « par rapport aux équipements existants » !) ou de technologies d’alignement coûteuses en laissant la possibilité de créer des airgaps (des trous dans le design, de manière à offrir une isolant de qualité). Au niveau des résultats, les chercheurs communiquent sur une capacitance réduite à 25 % à isorésistance pour un interconnect de 25 nm de pitch (une métrique mesurant l’écart entre fils, qui est à 30 nm sur la plus fine couche de l’Intel 4 !). Ici aussi, la solution serait transférable prochainement sur les couches métalliques les plus denses en complément du cuivre des nodes de gravure destinés à la production de masse : nous avons hâte !

Si toutes ces nouveautés et bien plus encore (au total, Intel a soumis 7 papiers à l’IEDM !) semblent alléchantes, il faut bien garder en tête qu’elles proviennent du groupe Technology Research (anciennement Components Research), au sein d’Intel Foundry. Et, dans l’appellation, l’emphase doit être mise sur la partie « Recherche » : le but est d’avoir des idées de nouveaux procédés, mais rien n’est encore prouvé quant à leur applicabilité à grande échelle — bien que certains papiers semblent avoir plus de prétentions que d’autres. Découvrir une technologie de pointe fait rêver, mais la bonifier pour pouvoir l’utiliser dans des produits à destination du grand public (qui plus est sur des puces typées haute performance), ça n’est pas une mince affaire. Rendez-vous dans quelques années pour découvrir lesquelles de ces inventions ont survécu à la sélection naturelle des semiconducteurs ?

Si seulement (pour eux) Intel était encore capable d'utiliser ces inombrables fonderie pour faire autre chose que cramer des milliards d'aides et des tonnes de silicium.

Car ils ont quand même abandonné le 20A il y'a pratiquement 1 an pour pouvoir se concentrer sur le 18A, et leurs rendement ne dépasse pas les (risible tellement ça en devient pathétique) 10%, tout le e reste c'est poubelle...

Ils peuvent innover tant qu'ils veulent, tant qu'ils passeront la plupart de leurs temps à raconter des cracks je vois mal des entreprises (vraiment sérieuse) prendre (encore) le risque de leurs faire confiance pour quoi que ce soit !

Pat Gelsinger est leurs PDG le plus durable depuis pas mal d'années, mais malheureusement celui qui leurs créait également le plus de tord avec ses mensonges et promesses bidon plus régulière que la pluie ne tombe dans ma région dans le seul but d'influencer le cour de leurs actions, car certains investisseurs sont malheureusement pour Intel encore à essayer de lui faire confiance.

Tant qu'ils ne seront pas ramasser et que la situation ne soit pas réellement critique, j'ai bien peur qu'ils vont continuer à accumuler les casseroles chez les Bleus

Et nous avons pourtant terriblement besoin d'une vraie concurrence (saine) pour le marché du CPU.

Car un AMD seul, n'est au final guère plus intéressant (é matière de Gap sur les performances et de tarifs que lorsque Intel faisait encore cavalier seul il y'a de ça dès années)

Tu ne sais pas de quoi tu parles

Beaucoup a commencé à partir de travers avec l'arrivée de Paul Otellini, essentiellement un homme d'affaires, aux commandes. Brian et Bob étaient de la même trempe. Il ne faut pas non plus négliger le rôle crucial du comité d'administration d'Intel dans tout ça, constitué en grande partie de membres sans expérience particulière dans le domaine du semiconducteur. En gros, difficile pour ces gens-là de prendre des décisions éclairées et informées en la matière, et qui s'arrêtent probablement aux chiffres et au cours de l'action. Un PDG comme Pat aurait sûrement dû prendre les commandes il y a bien longtemps et procéder à un recadrage en règle. Maintenant, changer la course du mastodonte est bien plus difficile, les mauvais choix du passé se payent encore et les règles du jeu ont beaucoup changé.