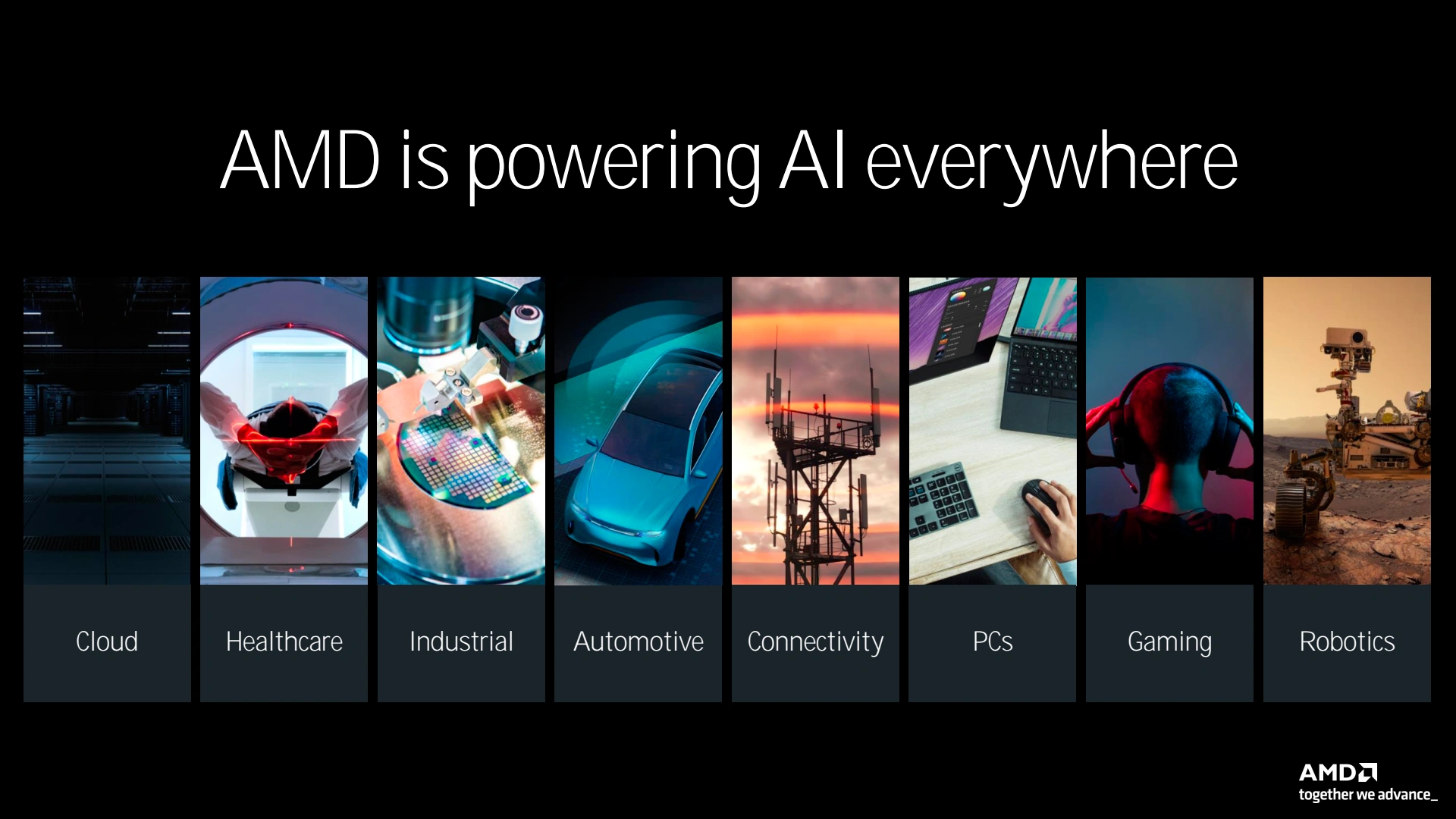

C'est au coeur de la cité des anges, écrasée par le soleil de juillet du sud de la Californie, qu'AMD a convié une partie (dont nous fîmes partie des heureux élus) de la presse mondiale pour son Tech Day 2024. Cet événement était clairement orienté autour de l'IA, et on sent bien qu'après avoir raté le coche face à NVIDIA pour son accélération via GPU, INTEL comme AMD veulent combler leur retard et profiter de l'intégration des NPU au sein de leurs CPU, pour capter aussi un part substantielle du gâteau. N'attendez pas pour autant de grosses annonces ici, puisque tout ou presque avait déjà été dévoilé il y a un gros mois lors du Computex, dont Nicolas avait assuré la couverture pour le compte de H&Co. Vous pouvez donc consulter par exemple cette news à ce sujet ou si vous désirez en apprendre davantage sur ce que l'on appelle l'IA, prendre le temps de lire le dossier qu'il lui a consacré.

De gauche à droite : Joe Macri, Mike Clark, Will Harris & Mahesh Subramony, parmi les maîtres architectes d'AMD

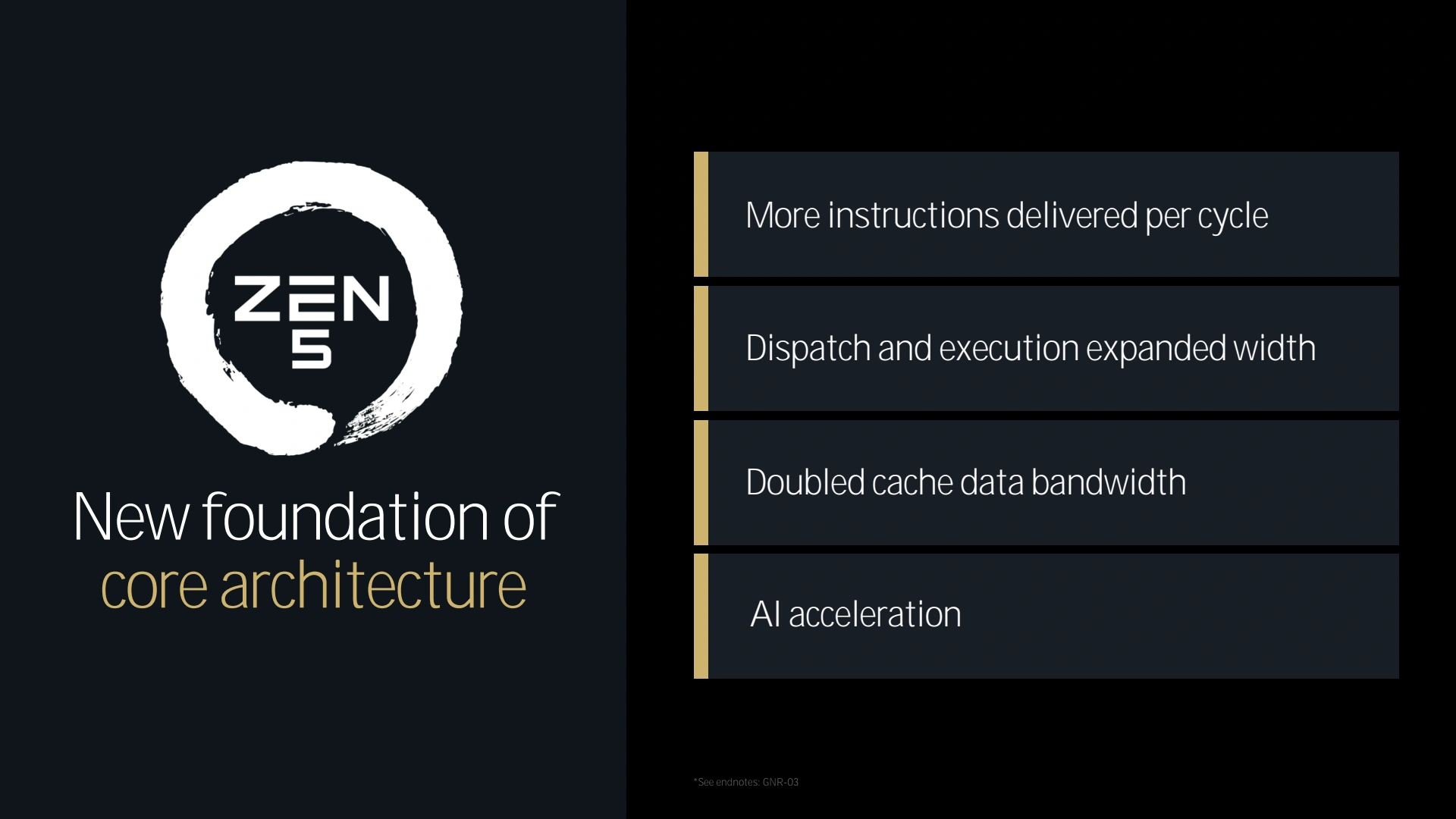

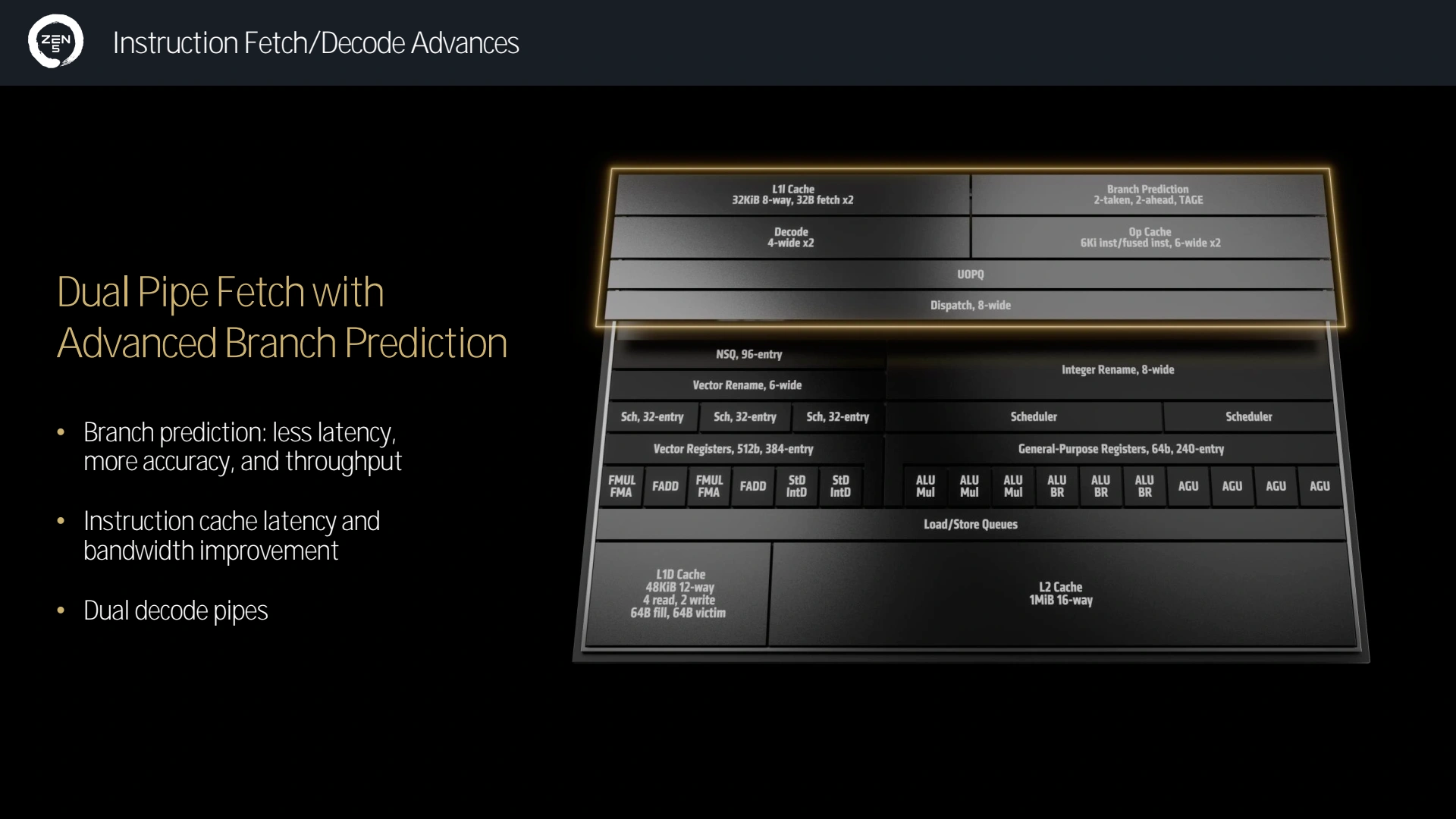

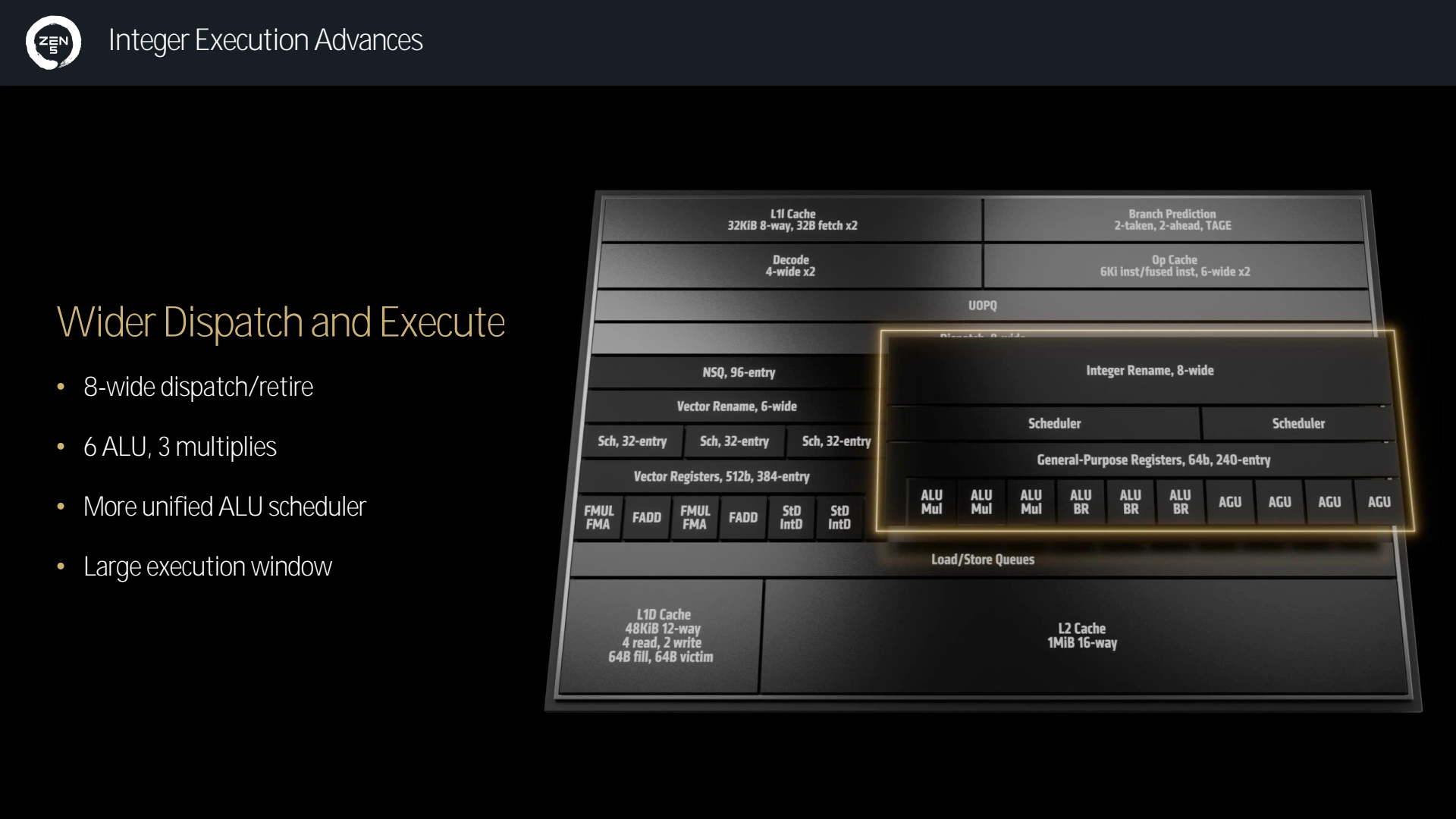

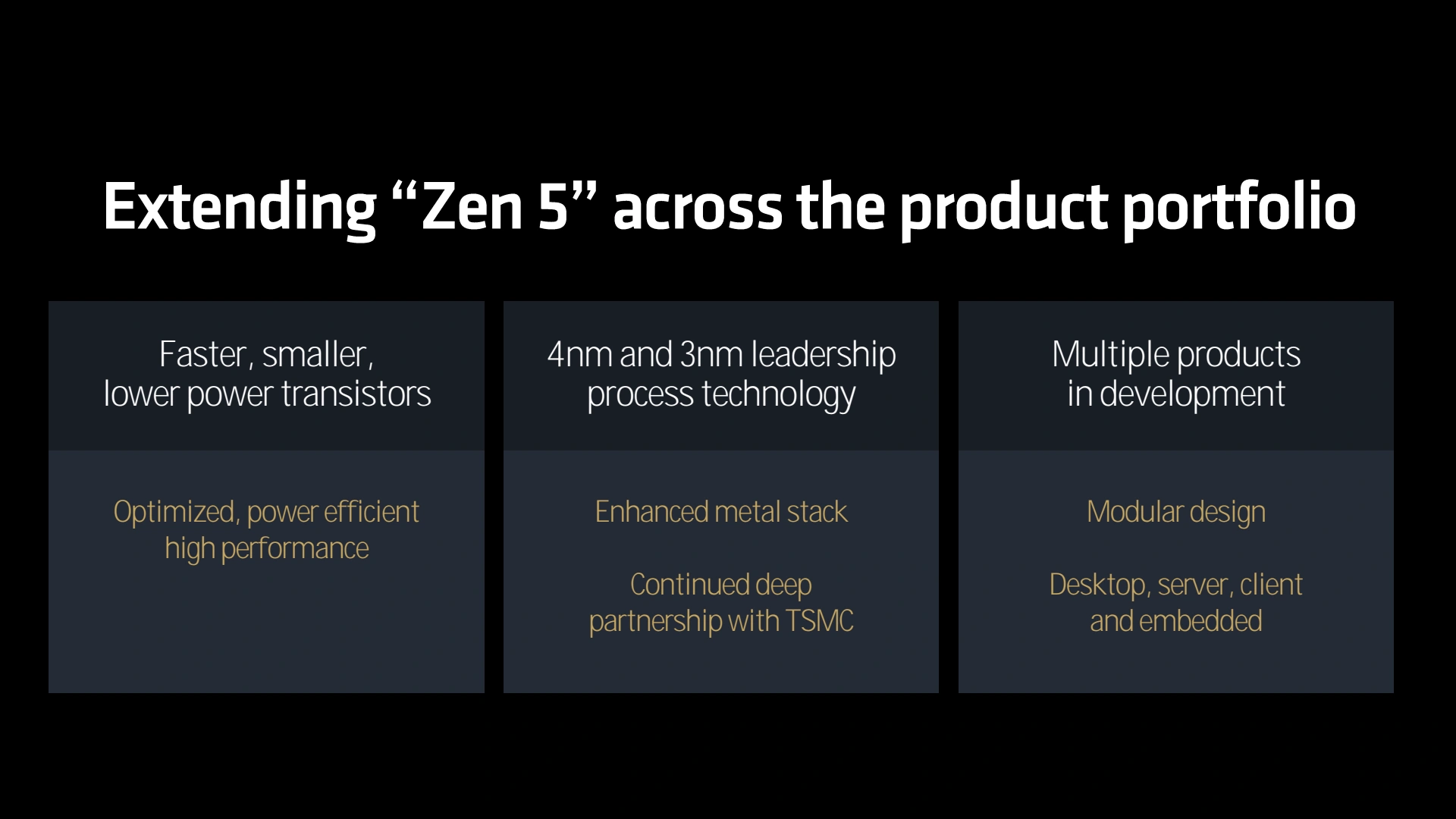

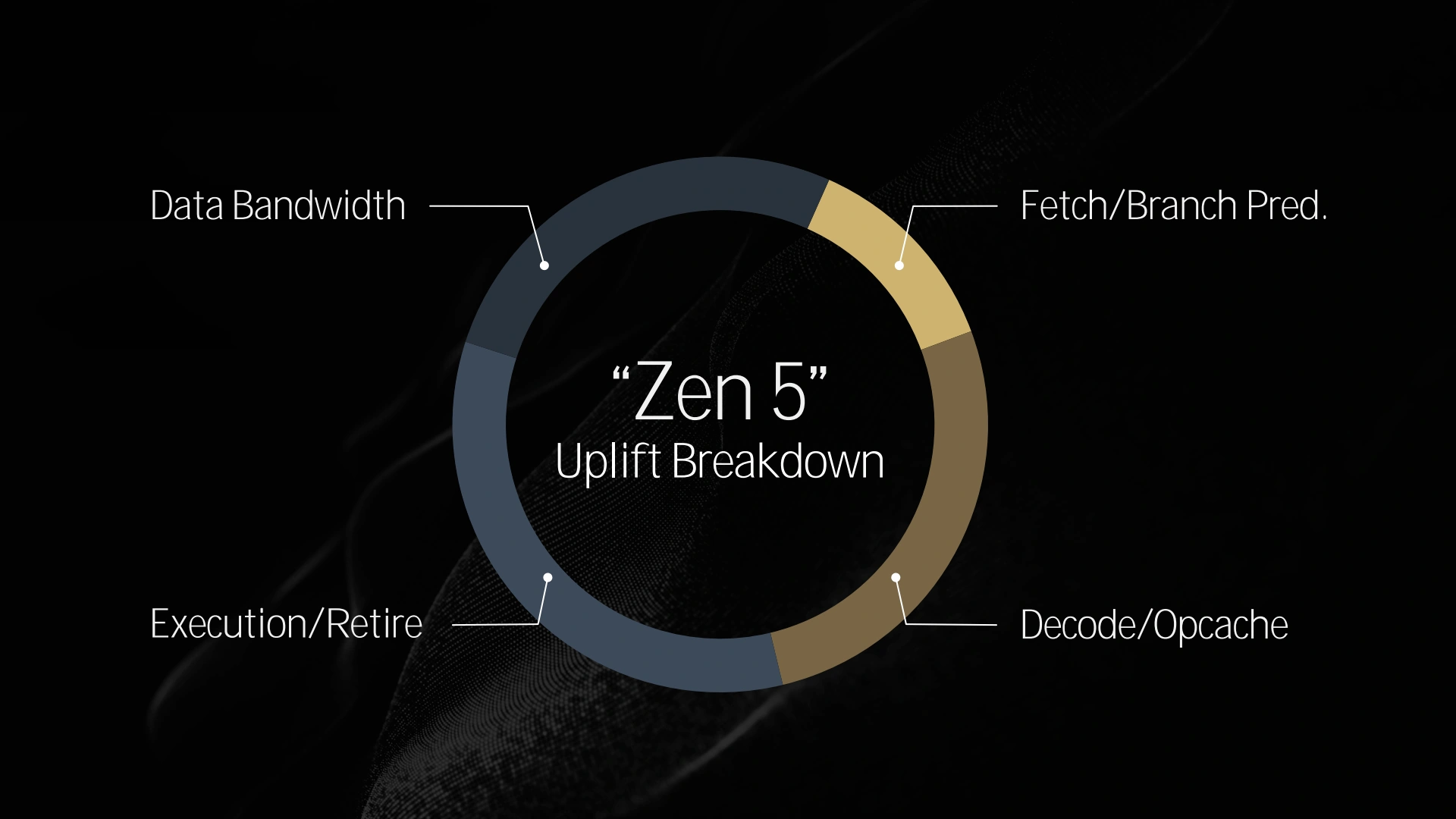

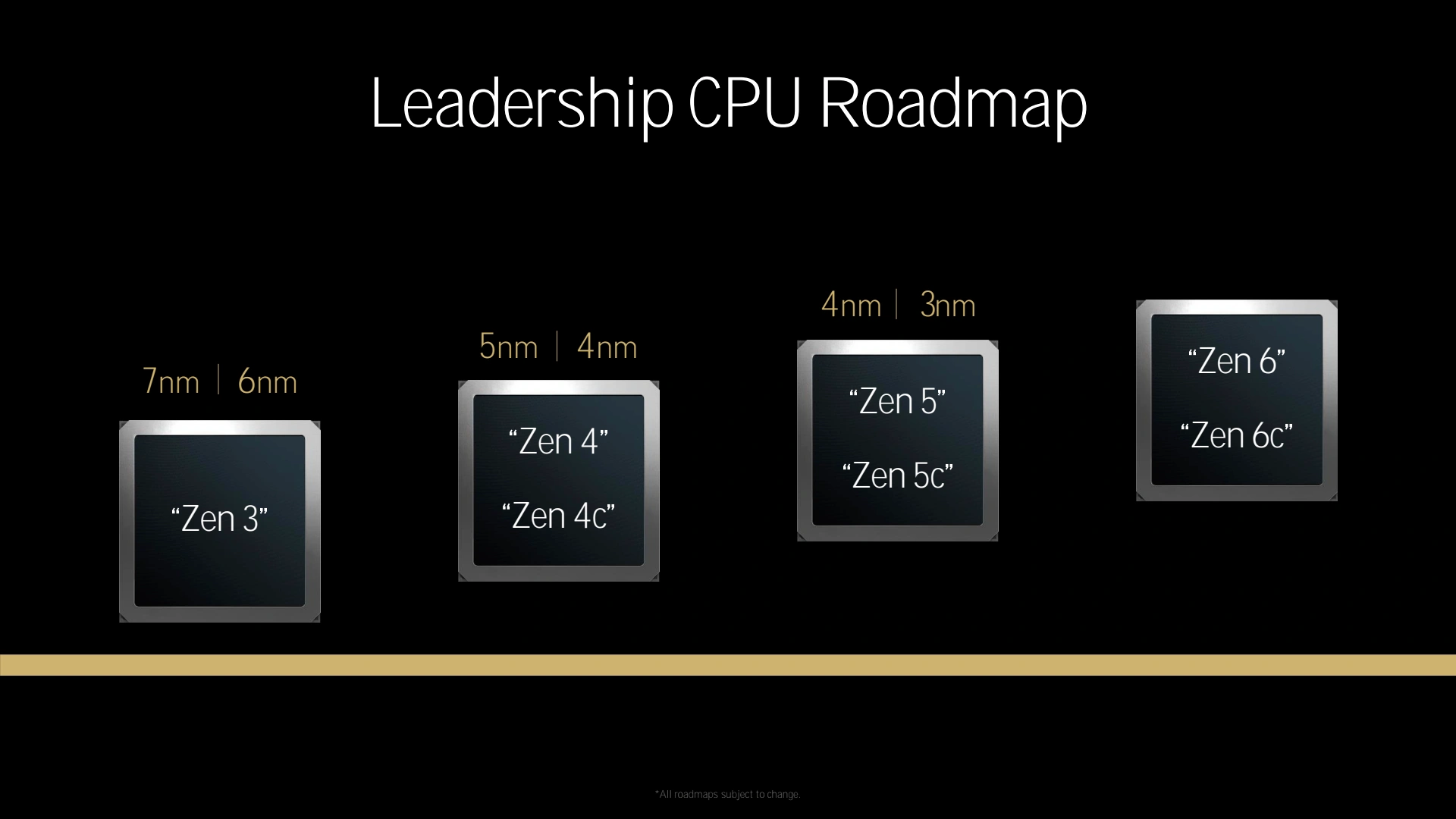

Mais revenons à nos moutons et l'événement d'AMD à proprement parler. La star n'y était pas la traditionnelle gamme desktop, qui finalement n'aura guère été au centre des attentions, à contrario de celle mobile, probablement du fait de l'absence de NPU au sein de la première citée. Avant de détailler les deux gammes, commençons toutefois par rappeler les principaux apports de Zen 5. L'architecte en chef décrit cette dernière comme une nouvelle fondation permettant d'envisager aisément les évolutions pour Zen 6/7 en s'appuyant sur ces nouvelles bases. En pratique, il ne s'agit toutefois pas d'une remise à plat complète de la microarchitecture comme avait pu l'être Zen en son temps, mais bien d'une évolution significative de la précédente itération. Ainsi au niveau du Front End, la prédiction de branchement progresse en termes de latence, précision et débit. La bande passante des instructions se retrouve doublée, ce qui permet d’augmenter la taille de la fenêtre des instructions (c’est-à-dire du nombre d’instructions auxquelles le processeur a accès).

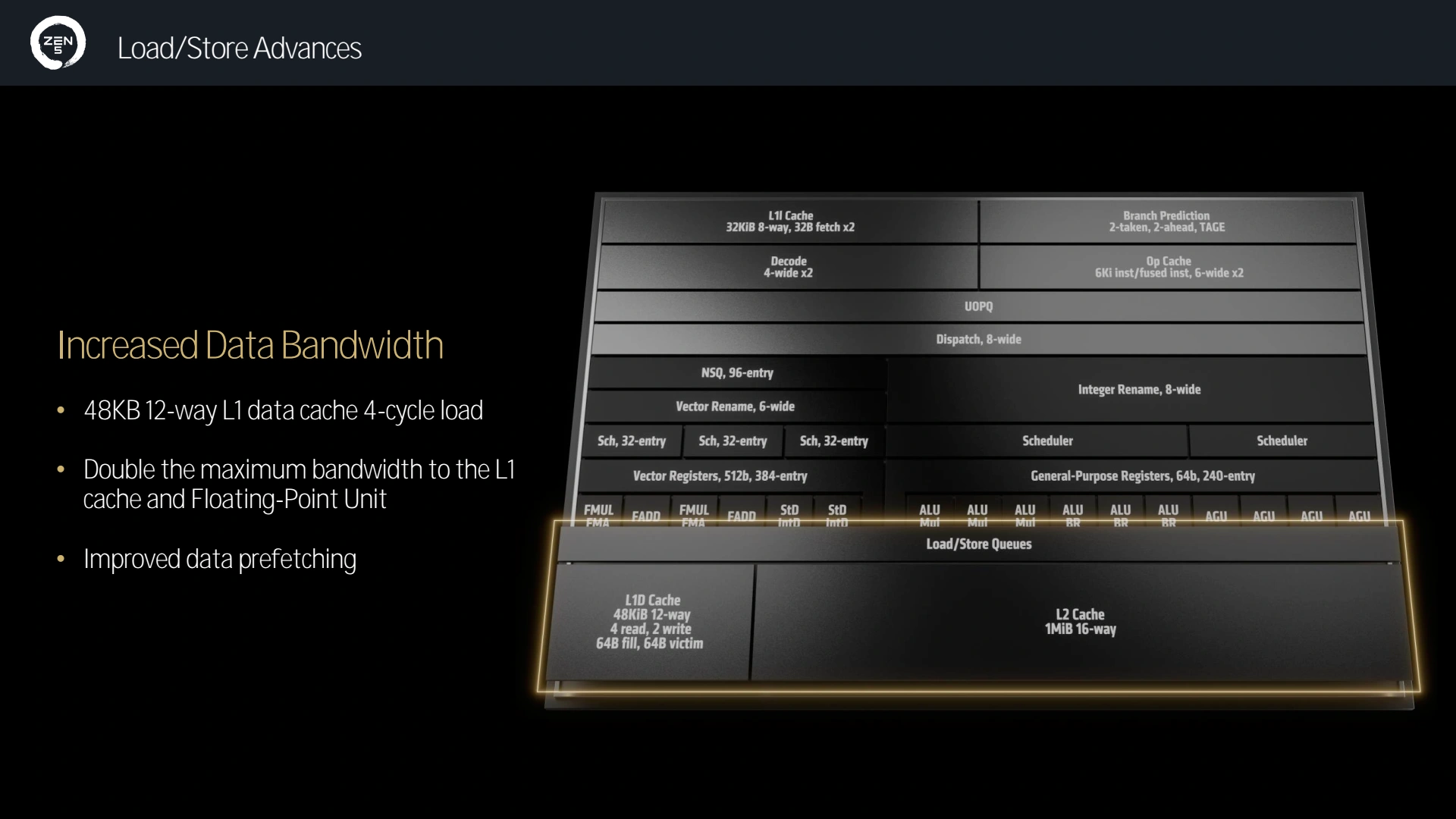

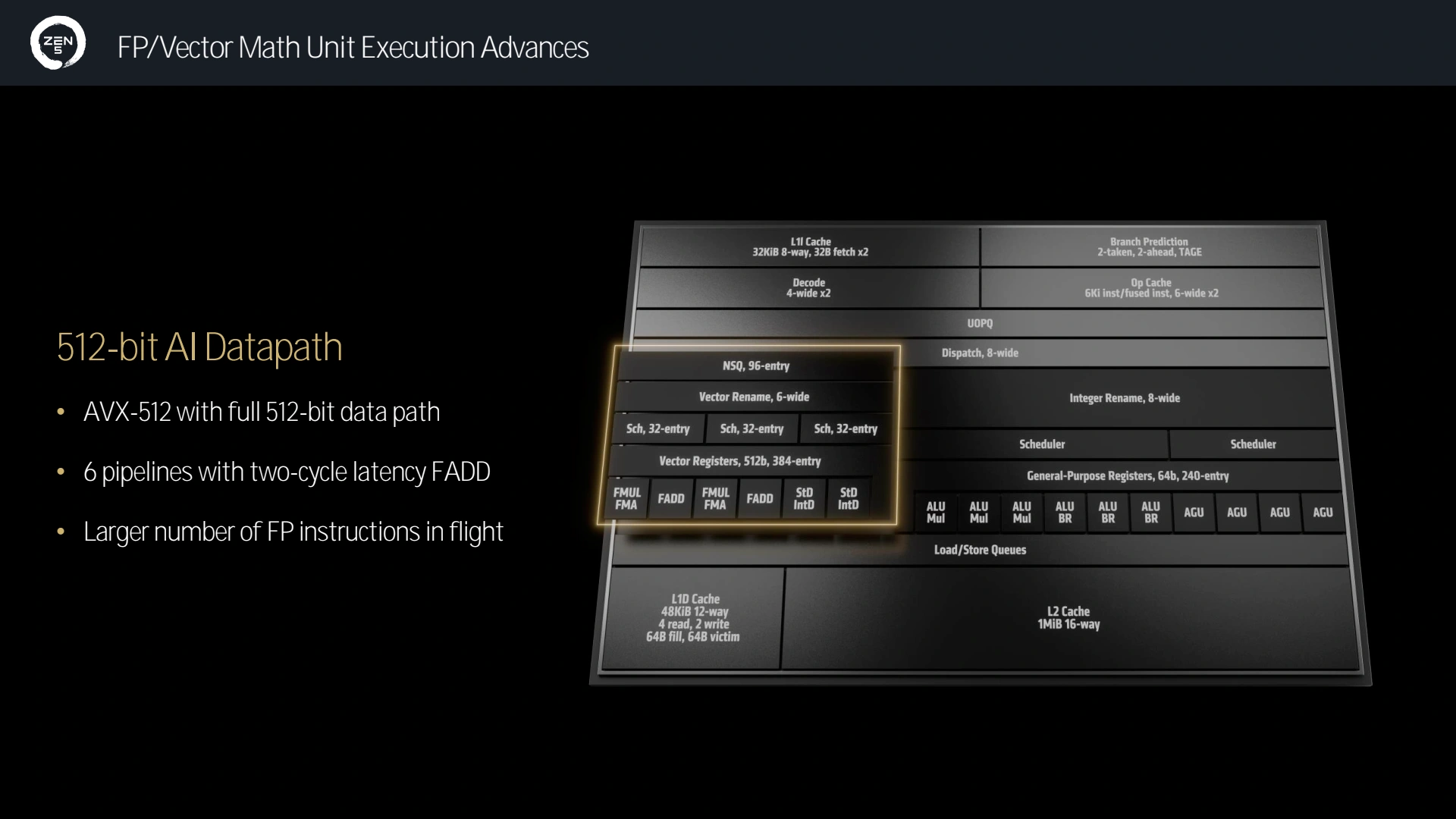

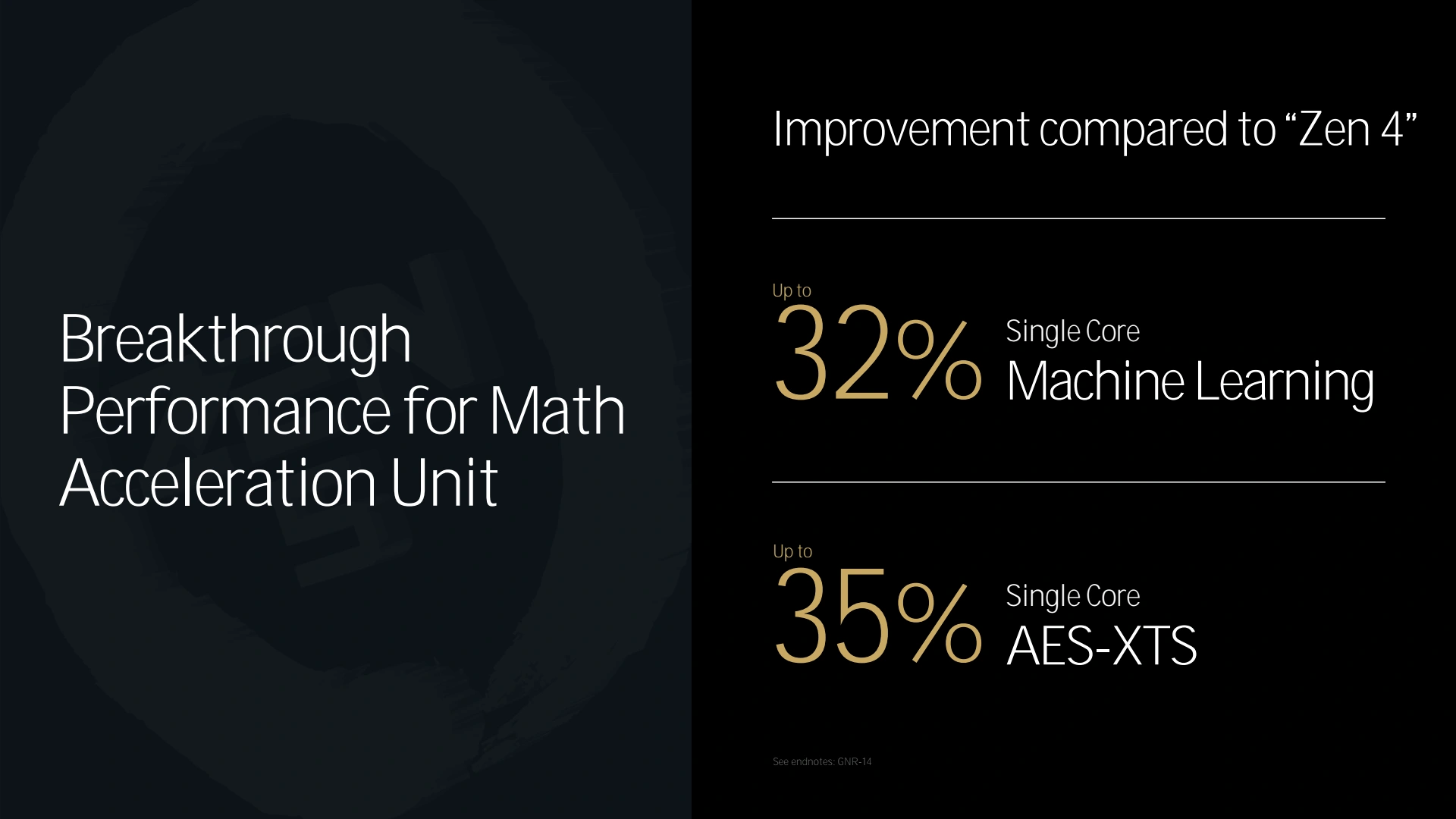

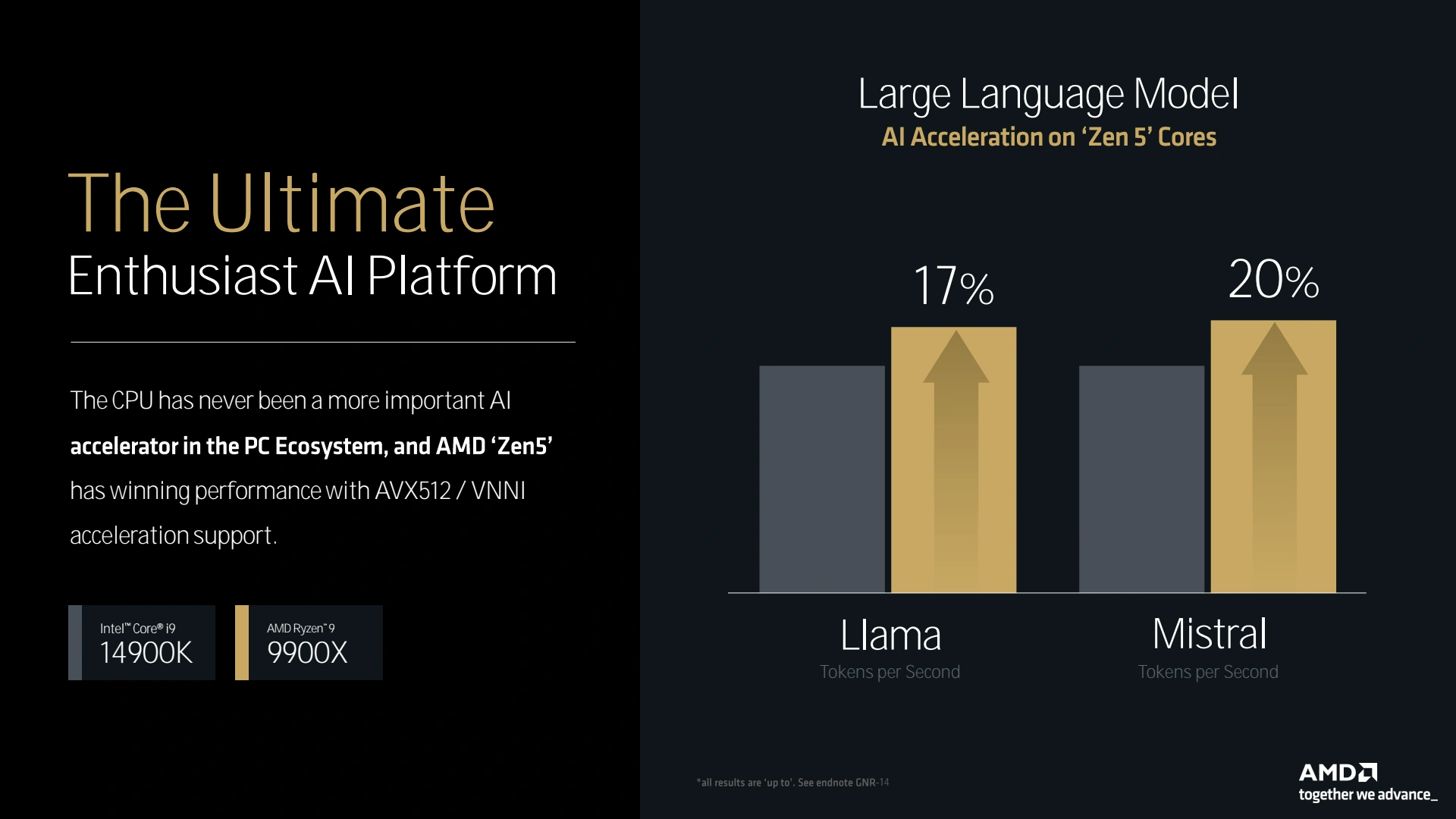

Après le décodage des instructions, vient le tour de leur exécution. Car plus de parallélisme dans le décodage, c’est bien, mais il faut également que la puissance de calcul suive : c’est ainsi que les rouges ont revu les capacités de calcul et en particulier des unités vectorielles en améliorant l’AVX-512 via des unités dual pump. Enfin, décoder et calculer ne sert à rien si le CPU passe son temps à attendre des données, c’est pourquoi les bandes passantes des caches ont été doublées (L2 vers L1 et L1 vers le pipeline vectoriel) afin d’être raccord avec le doublement de la puissance de calcul. De quoi expliquer les gains sur GeekBench, qui sont attribuables aux applications tirant parti des capacités vectorielles !

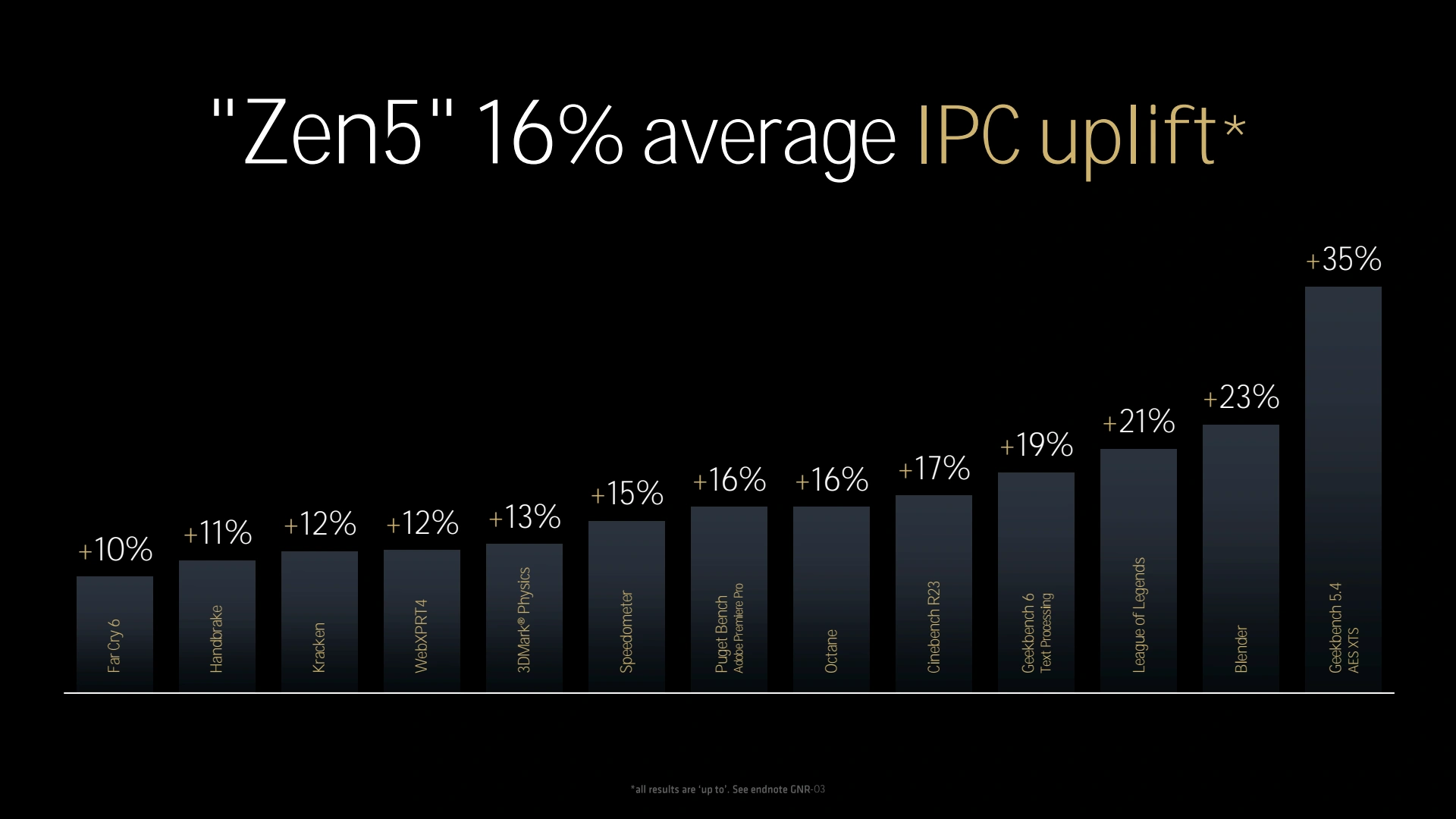

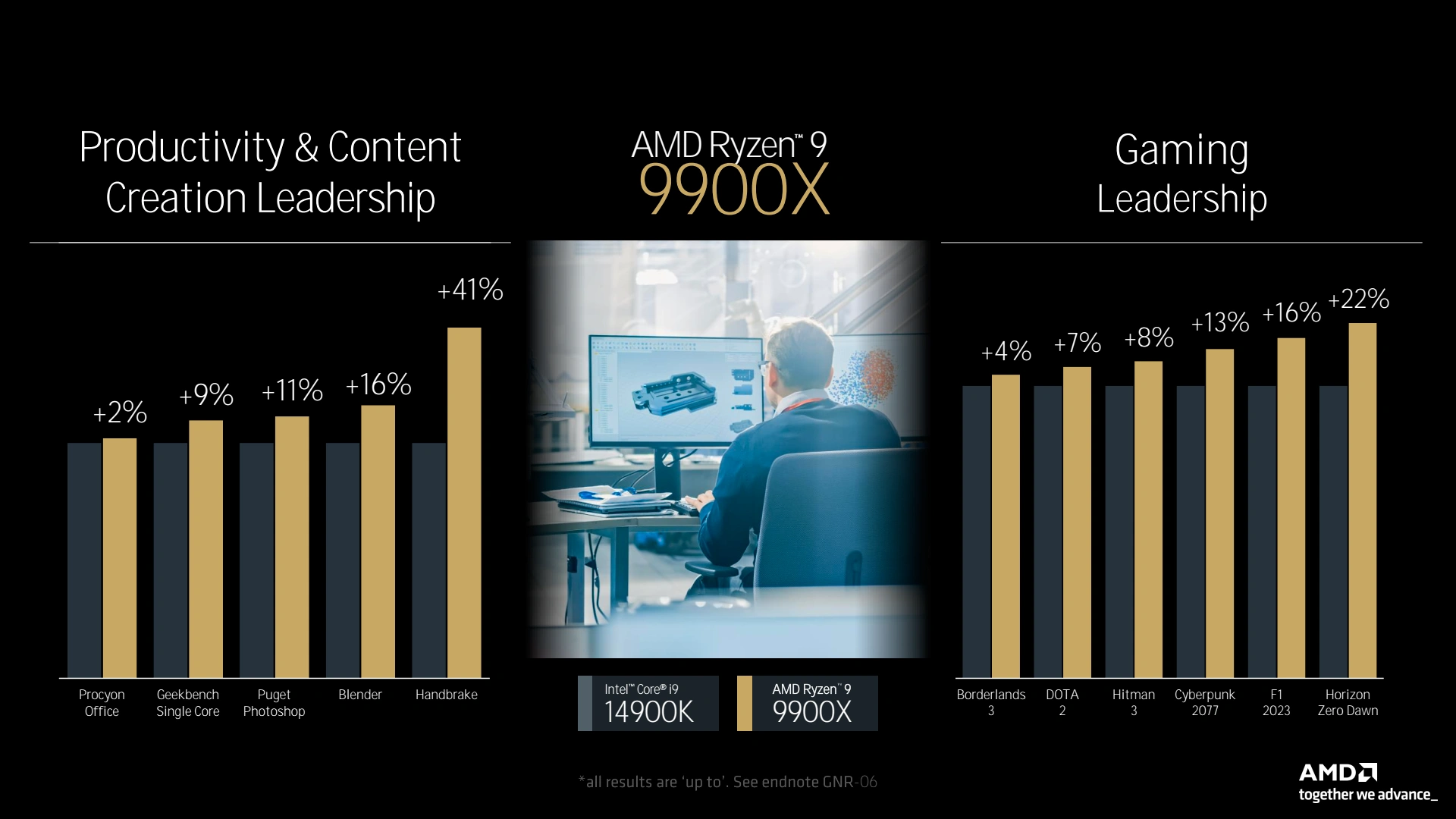

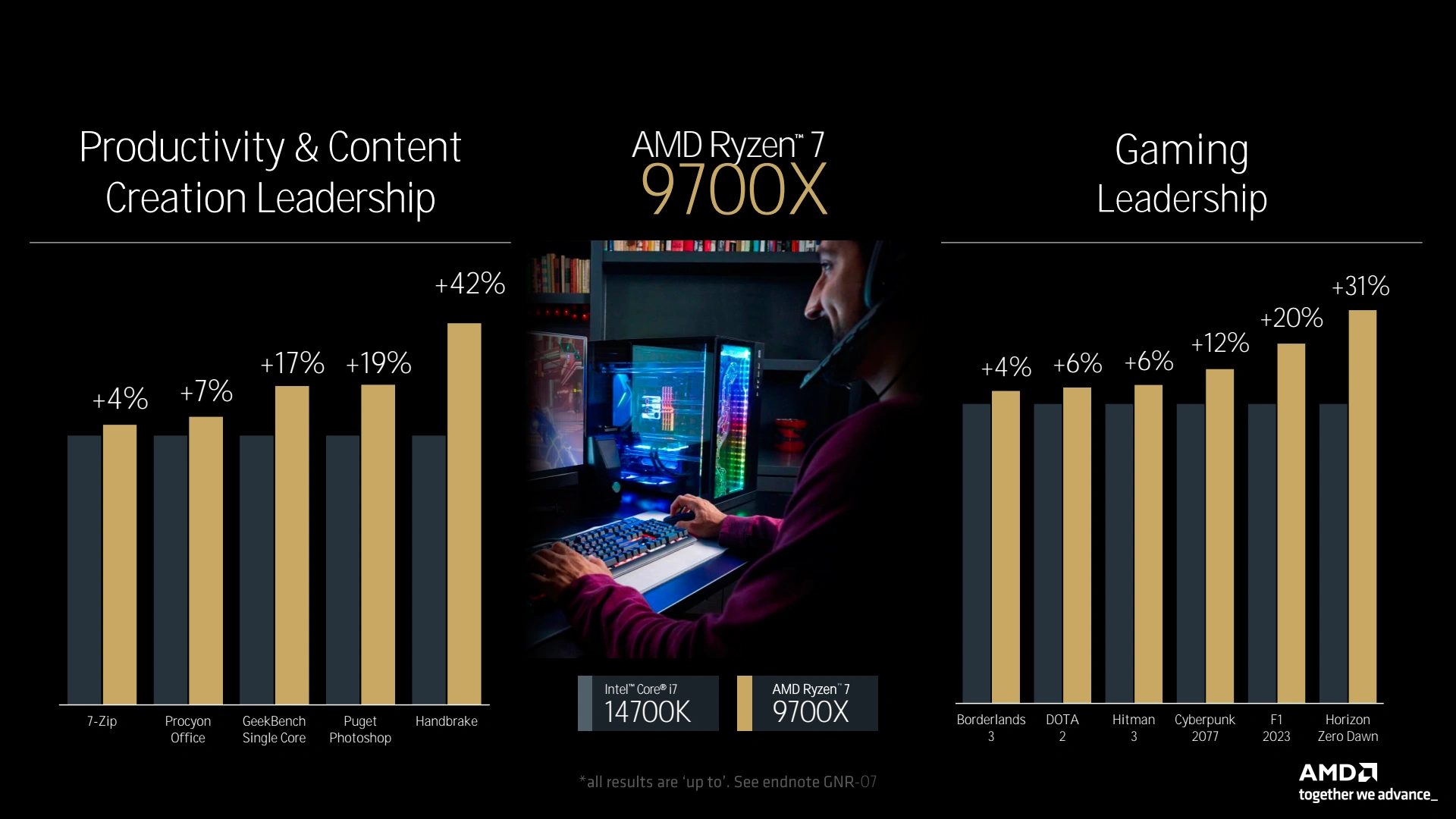

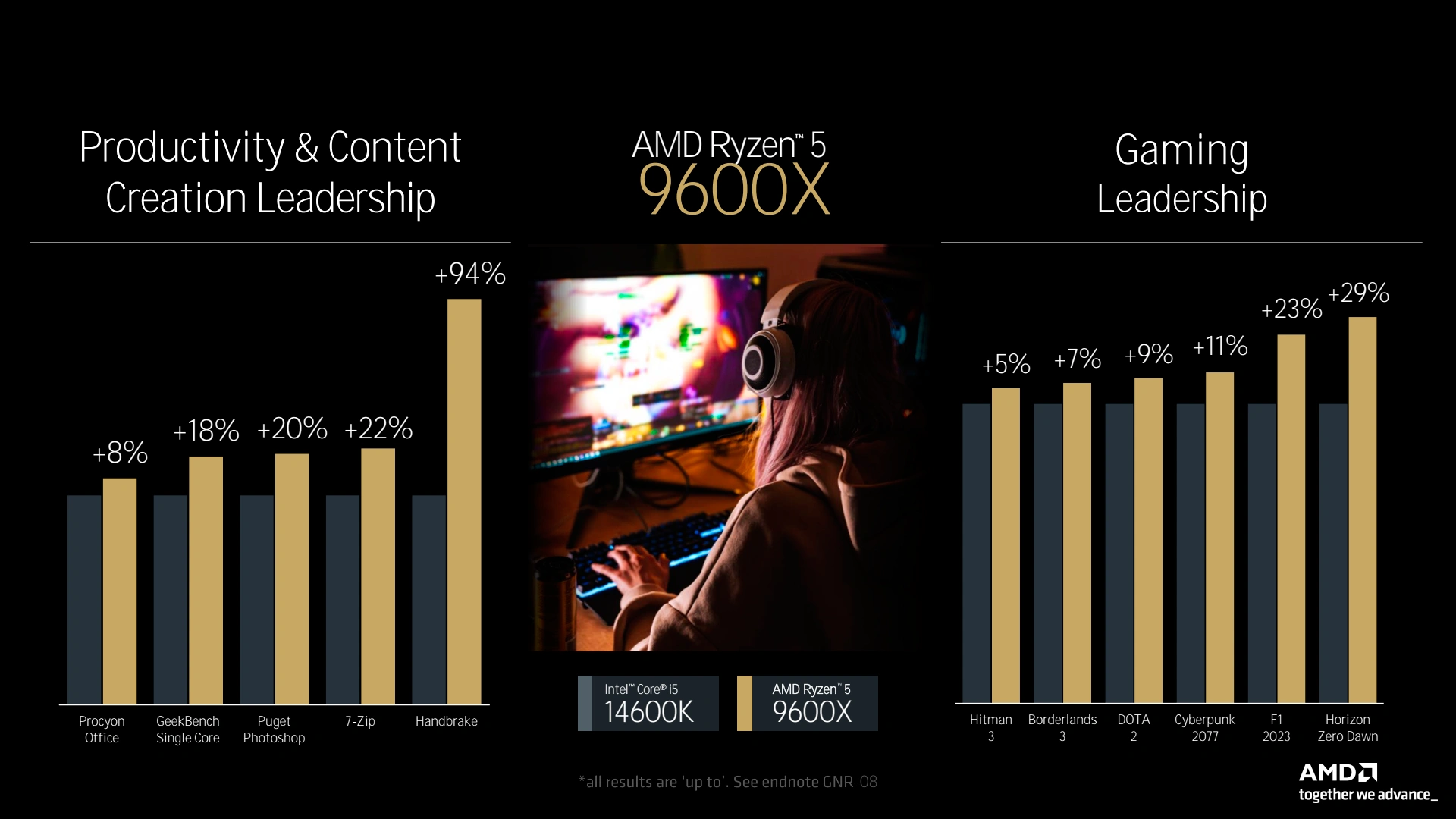

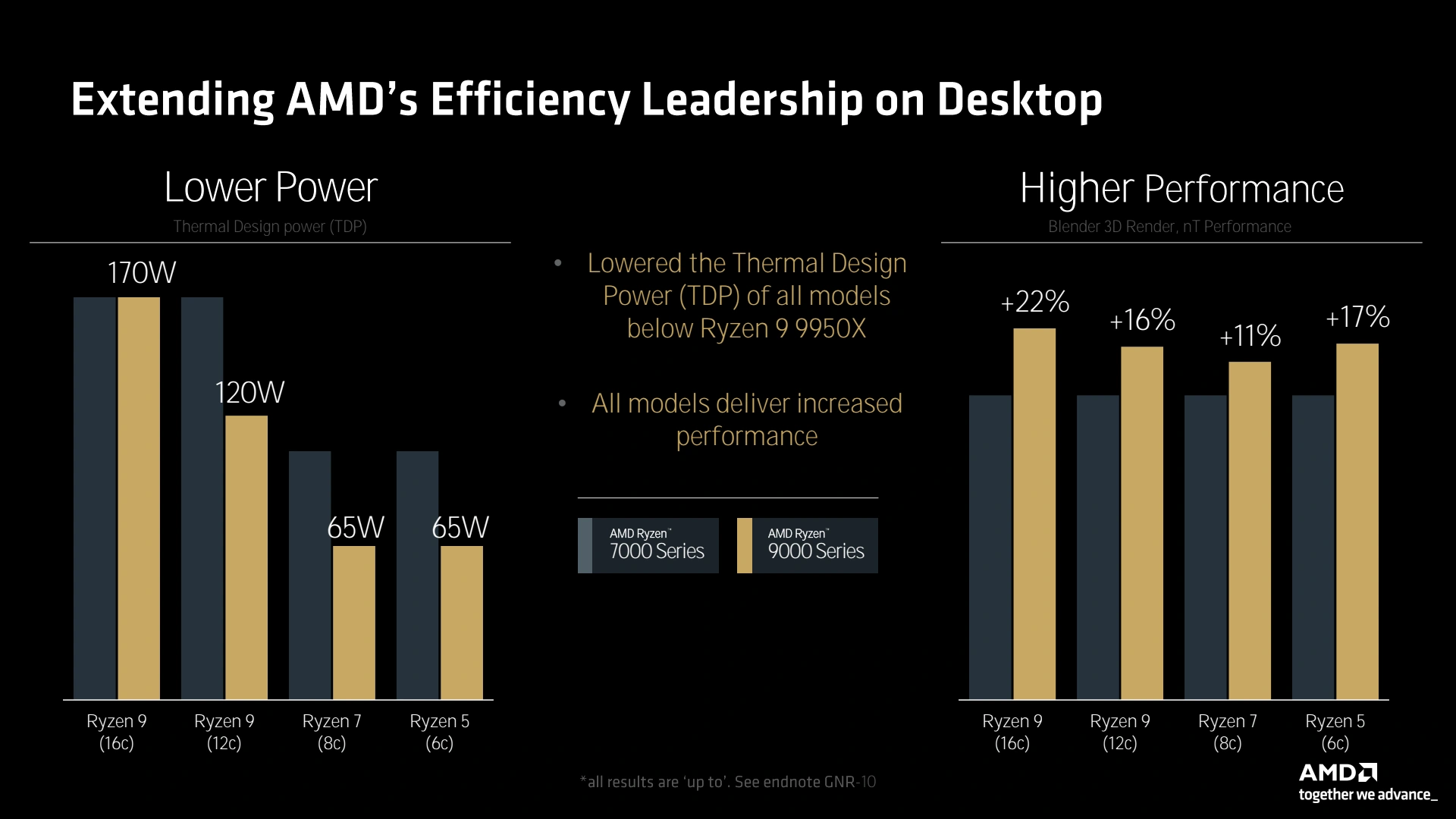

Toute cela conduit à un gain moyen d'IPC de 16 % en comparaison de Zen 4, même si cela varie fortement selon les applications. AMD indique que les gains se répartissent entre les 4 composantes indiquées précédemment avec une légère prédominance pour la partie exécution. Nous tâcherons de détailler tout cela lors du dossier consacré aux futurs processeurs pour PC Desktop dont nous allons parler à présent. Sans surprise la gamme de lancement se calque sur celle des générations précédentes (à partir de Zen 2), soit de 6 à 16 coeurs. Une différence toutefois, à l'exception du flagship, les 3 autres disposent d'un TDP moindre que celui de leurs prédécesseurs, une bonne chose. AMD indique une supériorité face à la concurrence de la Gen 14 d'Intel à tous niveaux de la gamme, nous vérifierons bien entendu ces assertions avec nos propres tests.

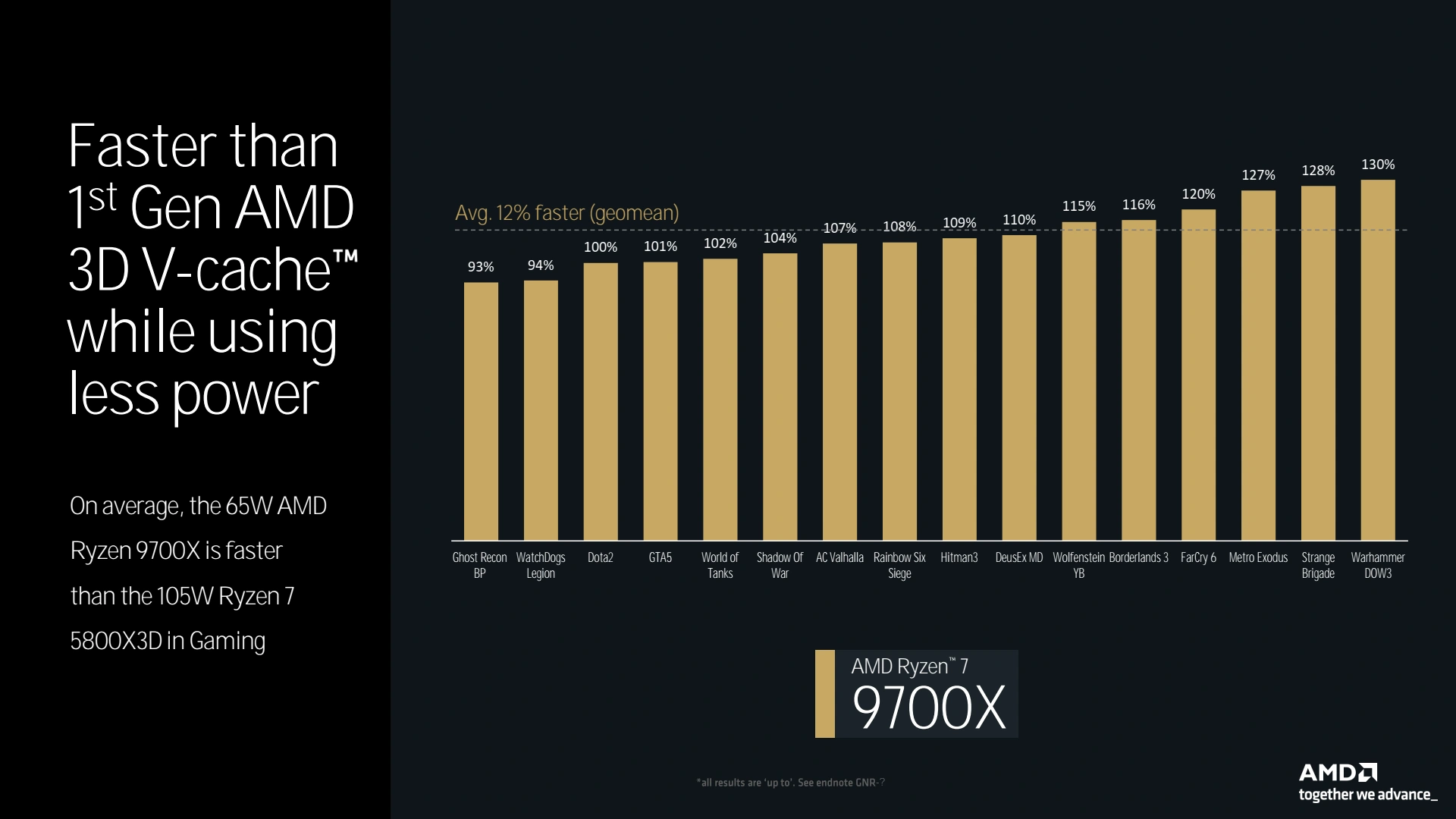

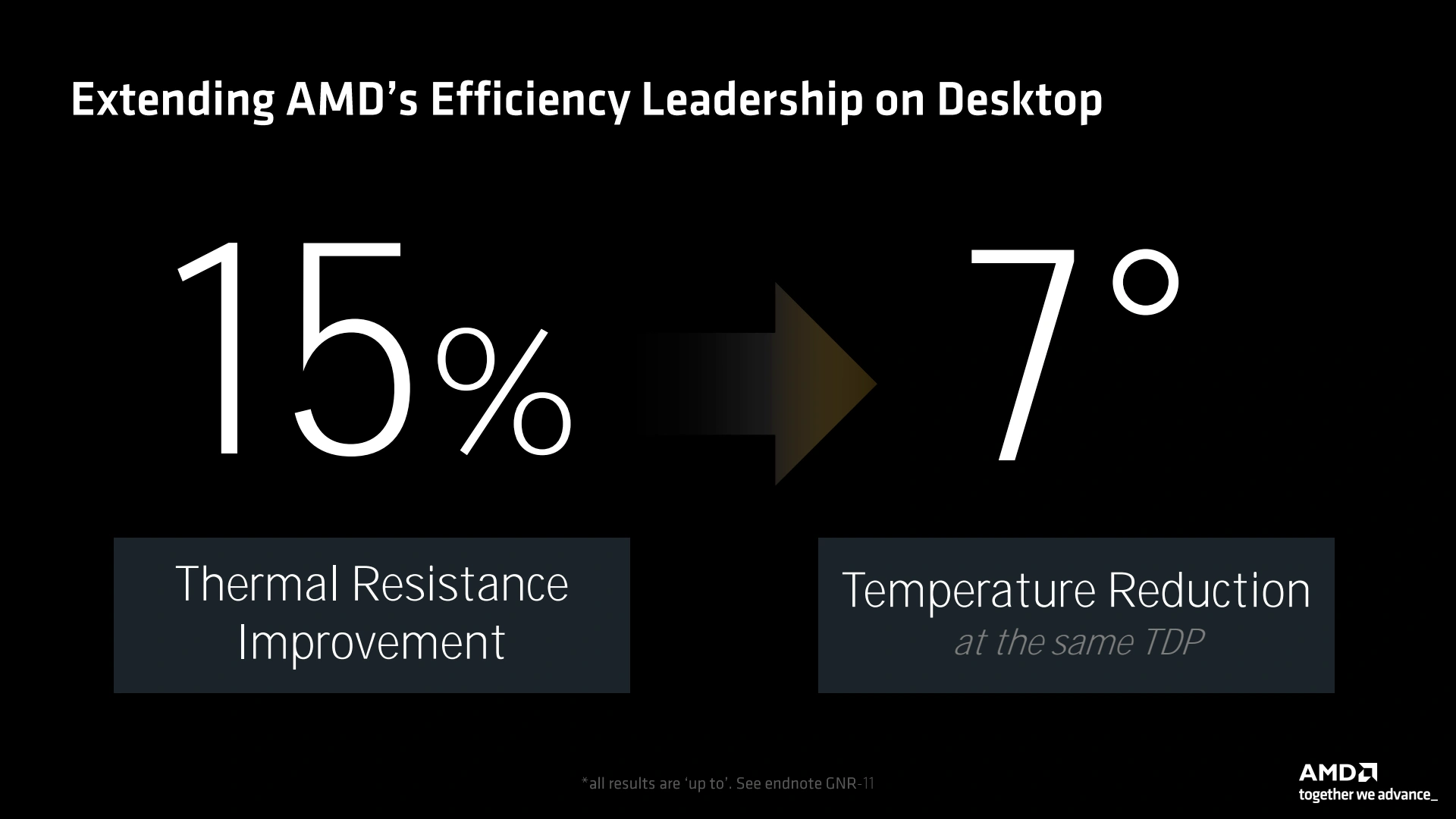

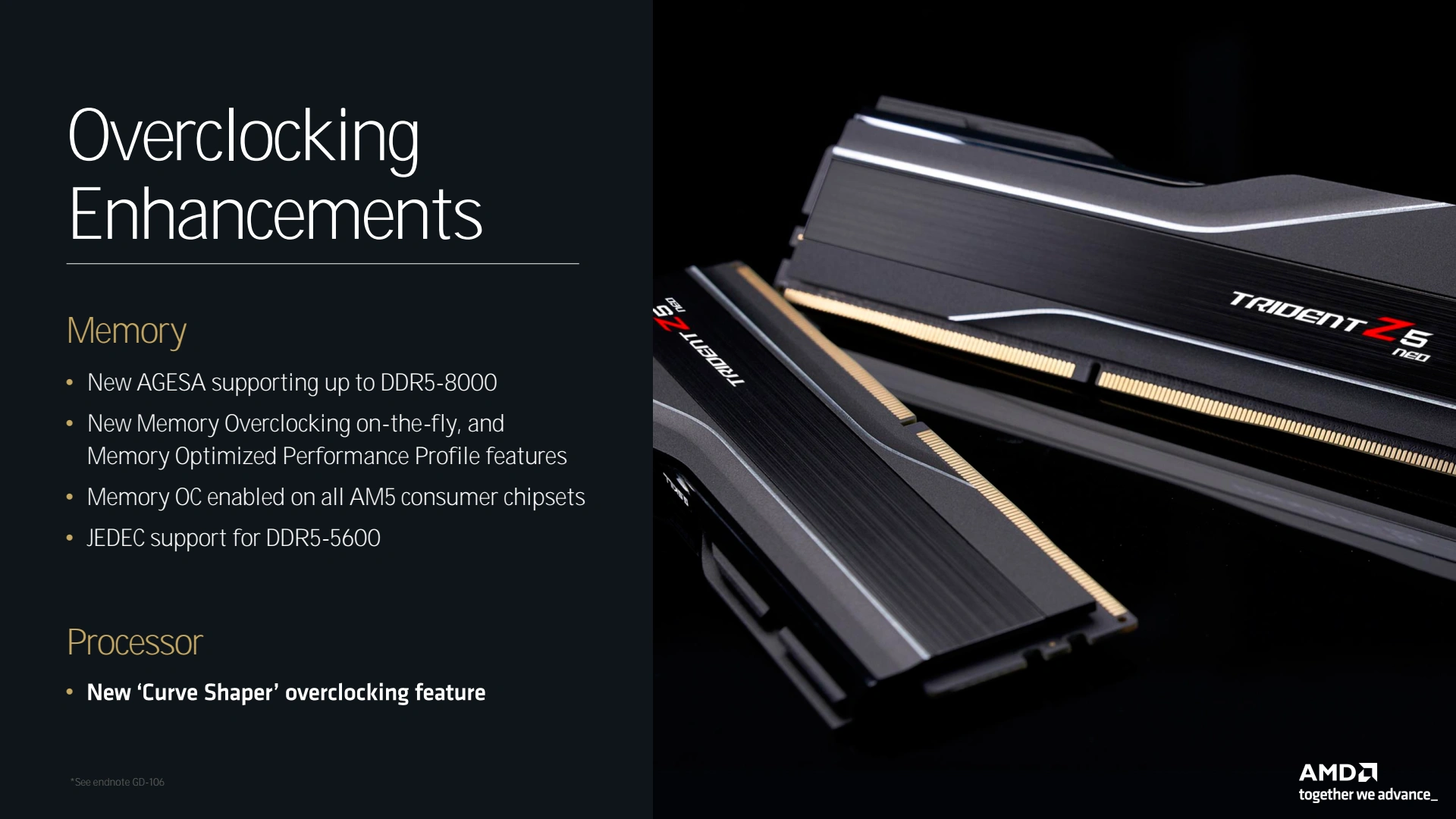

Le 9700X parviendrait également à devancer un 5800X3D en jeu, mais comme toujours l'échantillon retenu peut influencer largement ce rapport de force et sur nos propres tests, le 7700X n'en était déjà pas si éloigné. L'efficacité énergétique serait toutefois en hause notable et la température moindre (au même TDP) par le biais d'une amélioration de la résistance thermique. Enfin, une option de tweaking intéressante consiste en la possibilité d'appliquer des offsets non plus uniformes mais spécifiques à certains points de la courbe fréquence/tension. Cela permettrait par exemple d'appliquer un undervolting important sans pour autant que le CPU crash en IDLE du fait d'un offset généralisé qui conduirait à une tension de fonctionnement trop faible dans ce mode par exemple.

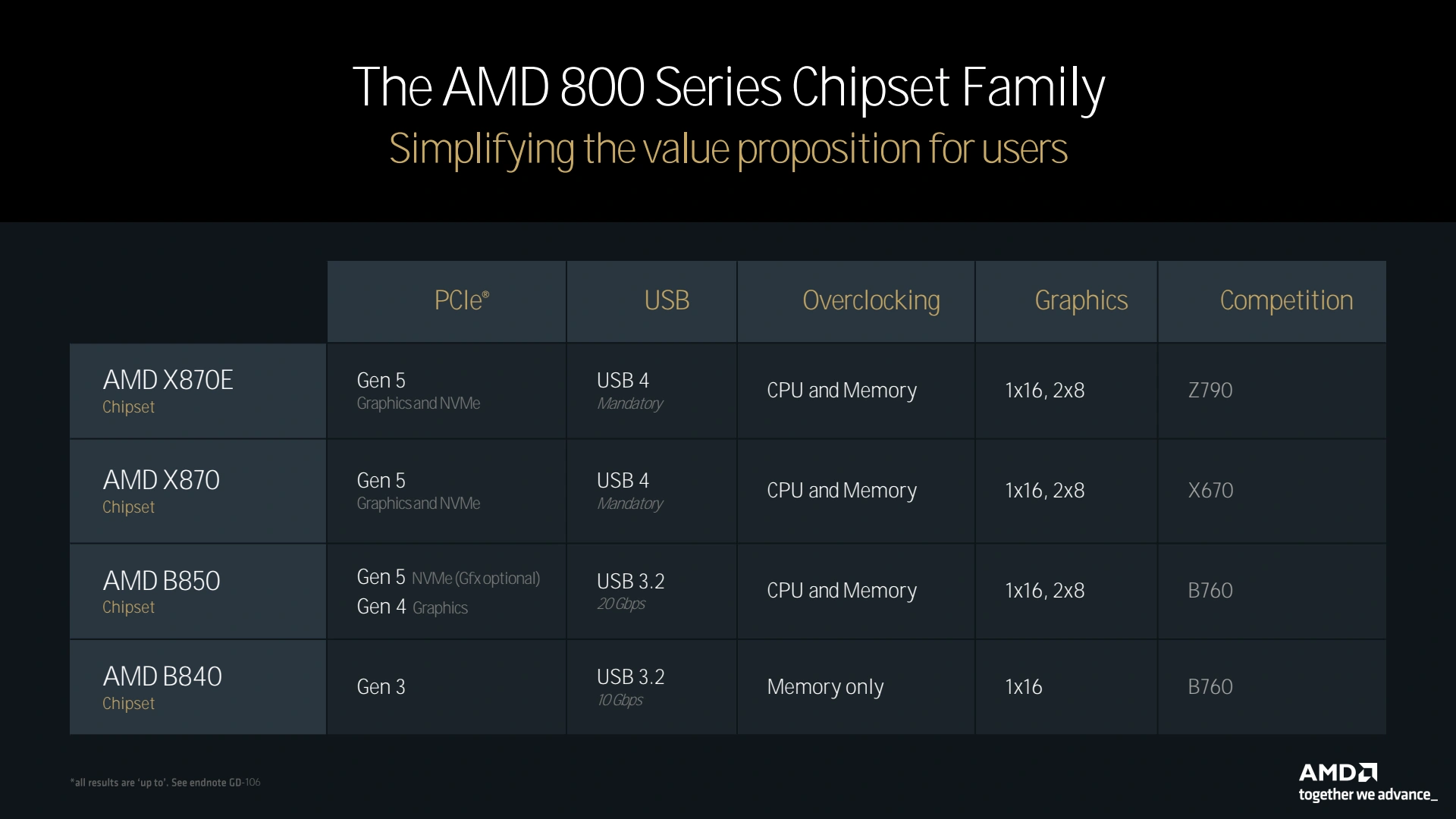

Côté plateforme, toutes les cartes mères AM5 sont censées supporter les nouveaux Ryzen 9000, même s'il sera probablement nécessaire de mettre à jour le bios au préalable. AMD a bien prévu une nouvelle génération de chipset, mais les cartes mères ne sont pas encore prêtes. Il faudra donc attendre quelques mois pour voir ces dernières à l'œuvre, en attendant, les caractéristiques ne semblent pas plus emballantes que cela en comparaison de la série 600, puisque hormis l'USB 4, il n'y a vraisemblablement pas grand chose à se mettre sous la dent, sans compter que la conservation de l'I/O die au sein des processeurs, conduira à une bande passante toujours limitée entre CPU et chipset...

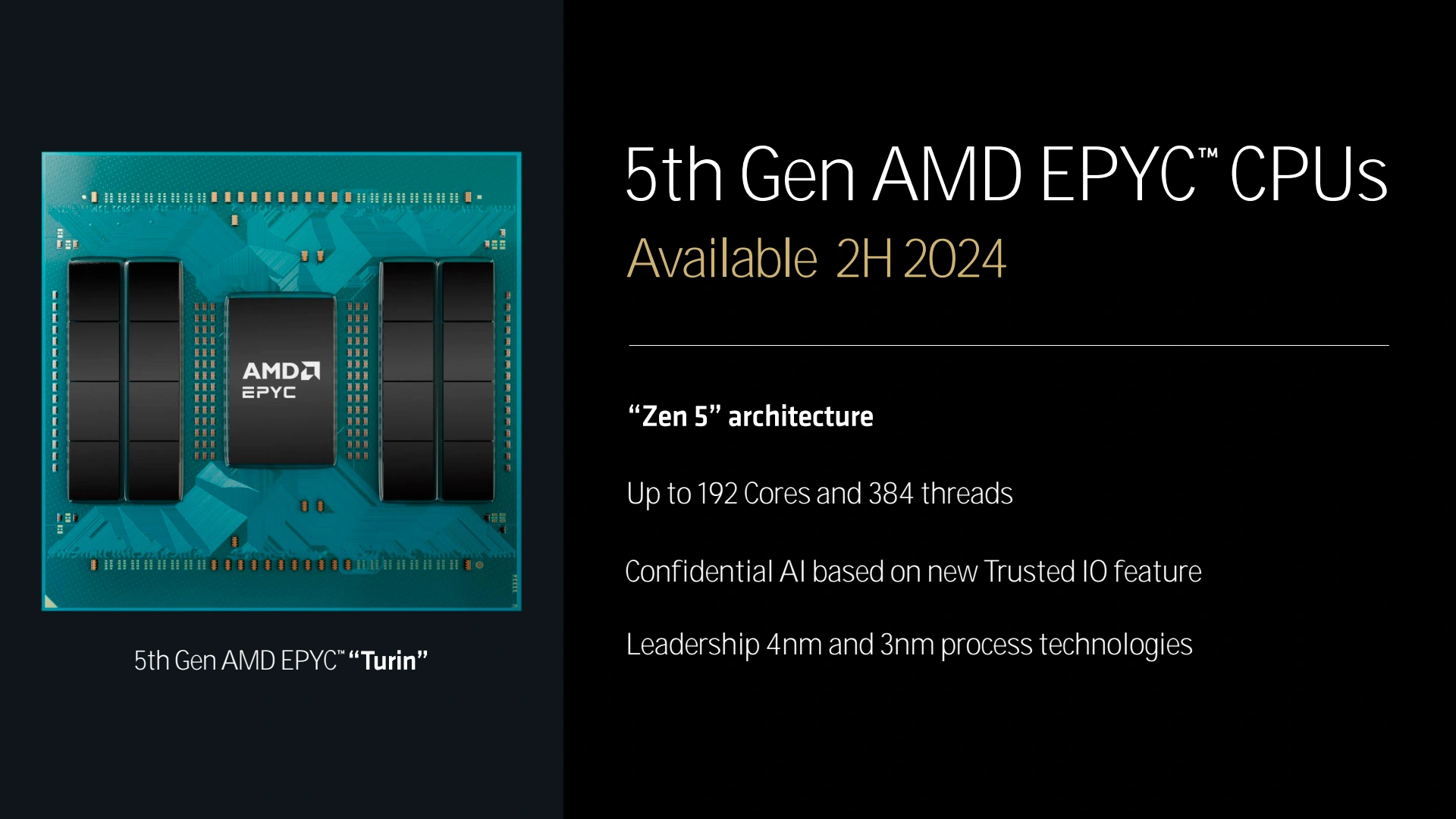

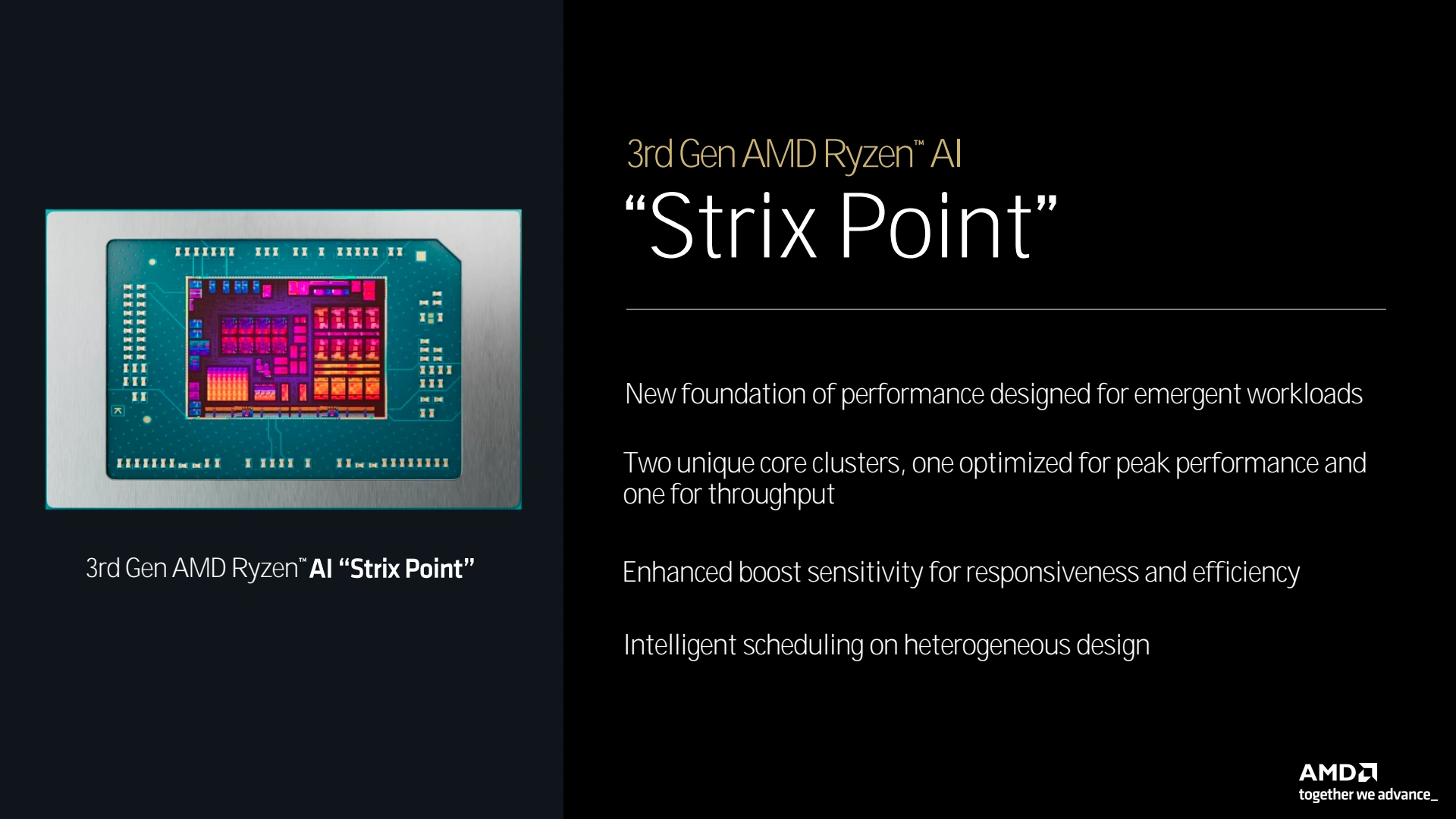

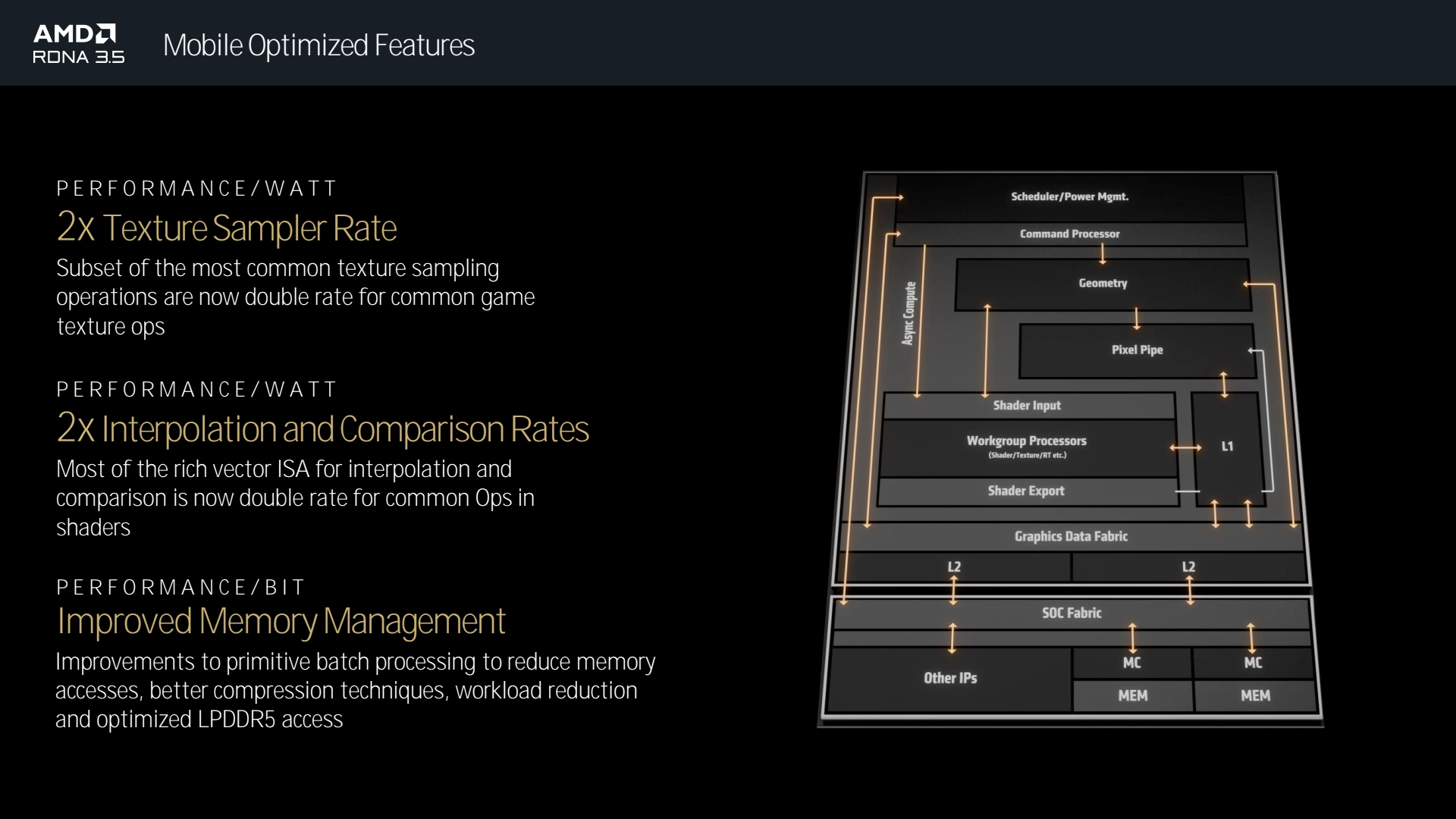

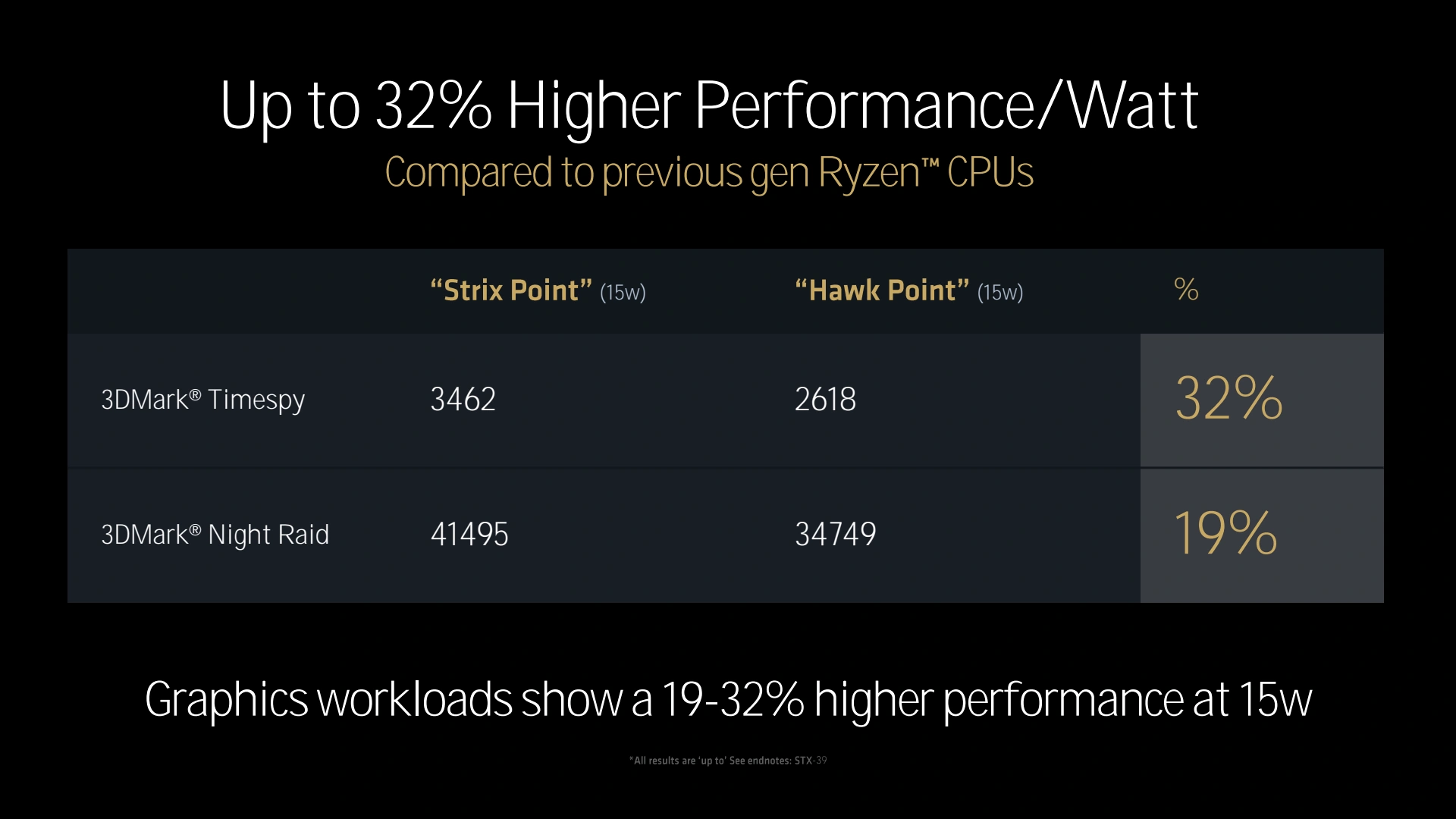

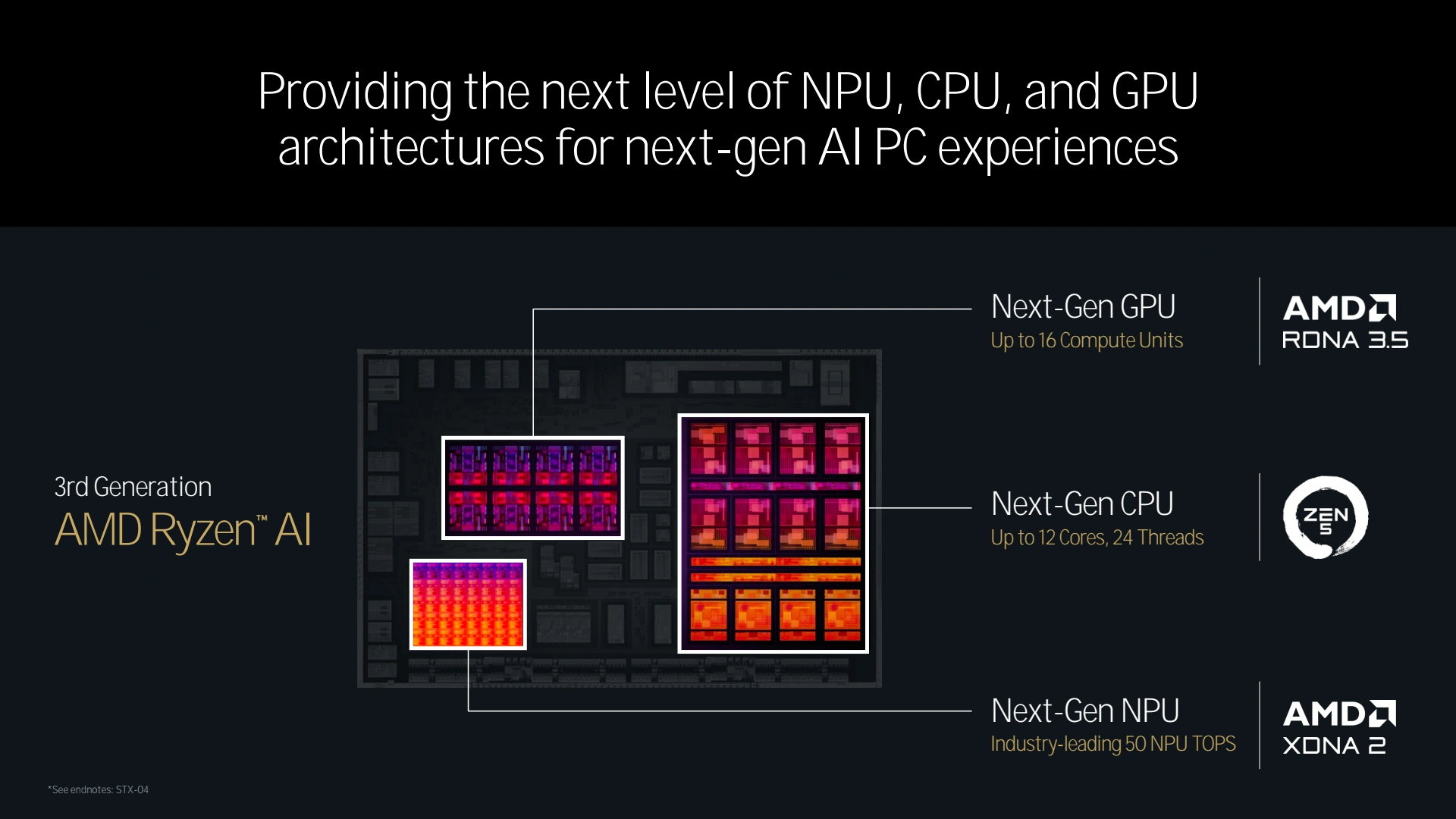

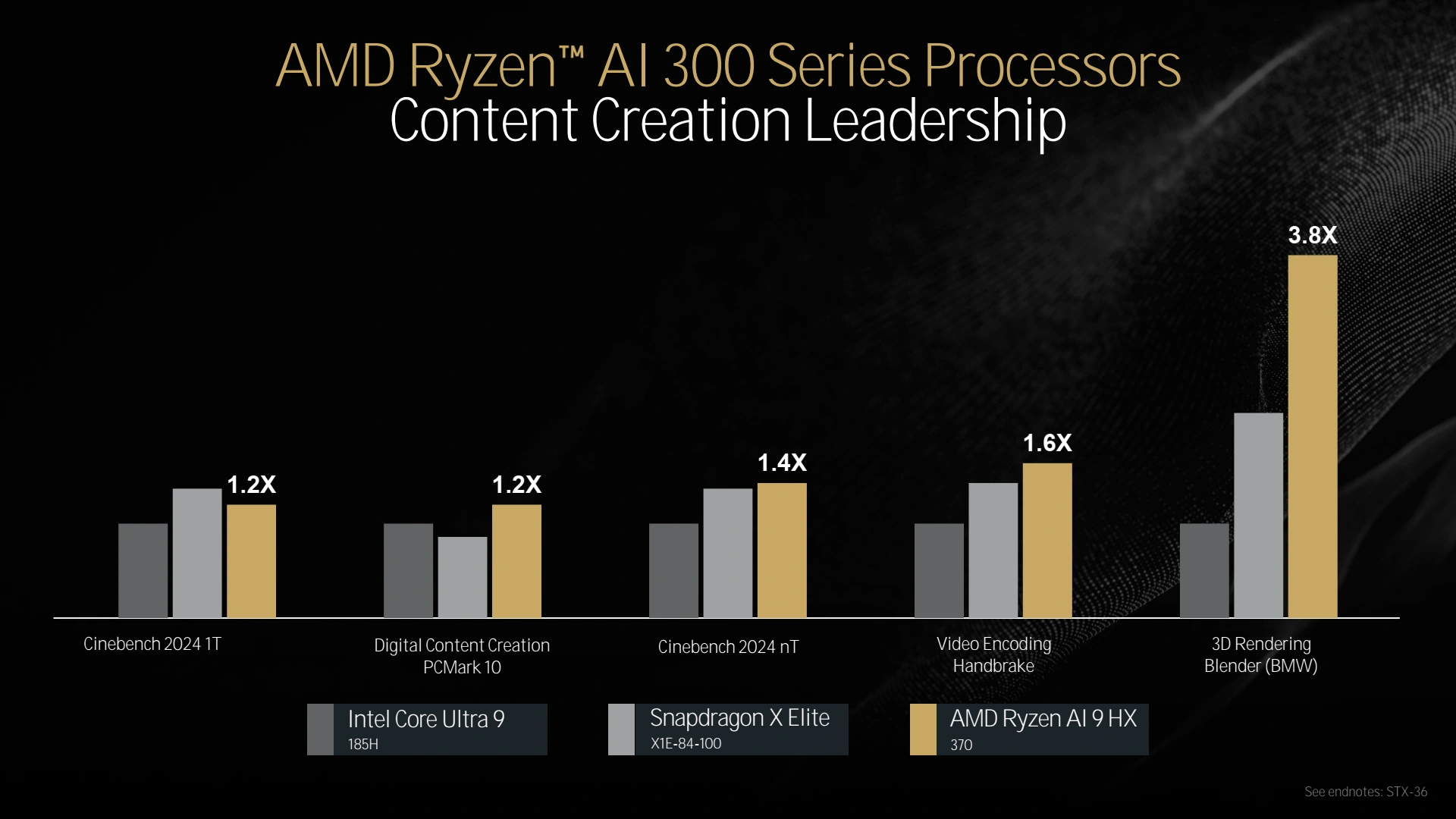

Au-delà de la gamme de processeurs pour PC de bureau, AMD a également touché 2 mots sur le futur avec un Zen 6 déjà dans les tuyaux mais aussi à échéance plus proche les puces professionnelles Epyc au non de code Turin, embarquant jusqu'à 192 coeurs. Enfin, la déclinaison mobile de Zen 5 aka Strix Point a eu le droit aux honneurs. Basée sur un die monolithique, on peut espérer les voir arriver dans quelques temps sur PC de bureau au travers des traditionnels APU. En attendant, ils feront le bonheur des PC portables, et embarquent jusqu'à 12 coeurs Zen 5 dont 8 de type C (compact) disposant d'une fréquence de fonctionnement moindre. On retrouve également au sein de ce die le nouveau NPU XDNA 2 que nous détaillerons un peu plus bas et un GPU comprenant jusqu'à 16 CU et basé sur RDNA 3.5. Cette évolution de l'architecture RDNA 3.0 a pour objet d'améliorer drastiquement l'efficacité énergétique, un point clef dans le monde de la mobilité. Pour ce faire, AMD a principalement retravaillé son pipeline graphique pour limiter autant que possible les accès mémoire, qui sont très coûteux en énergie.

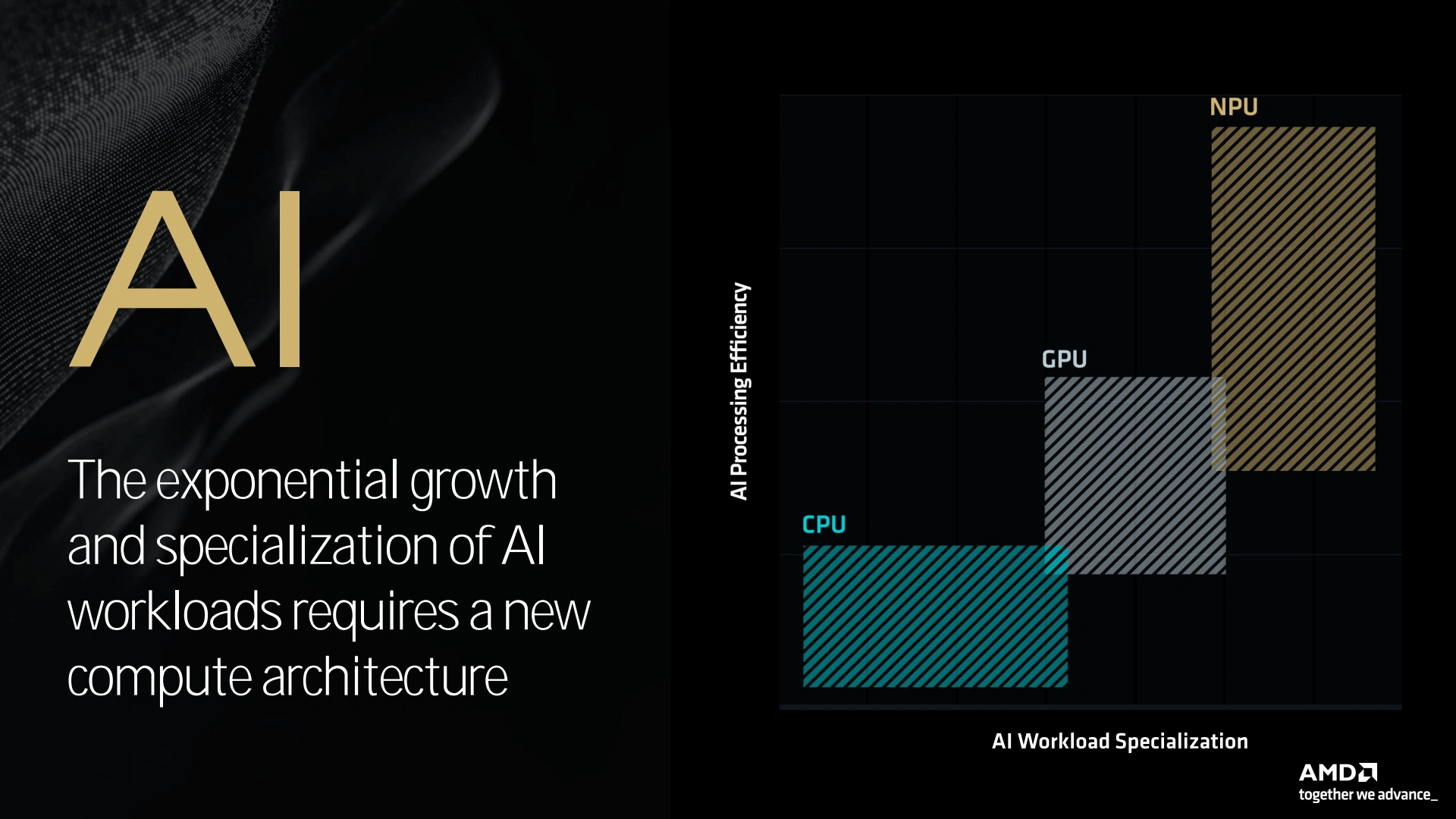

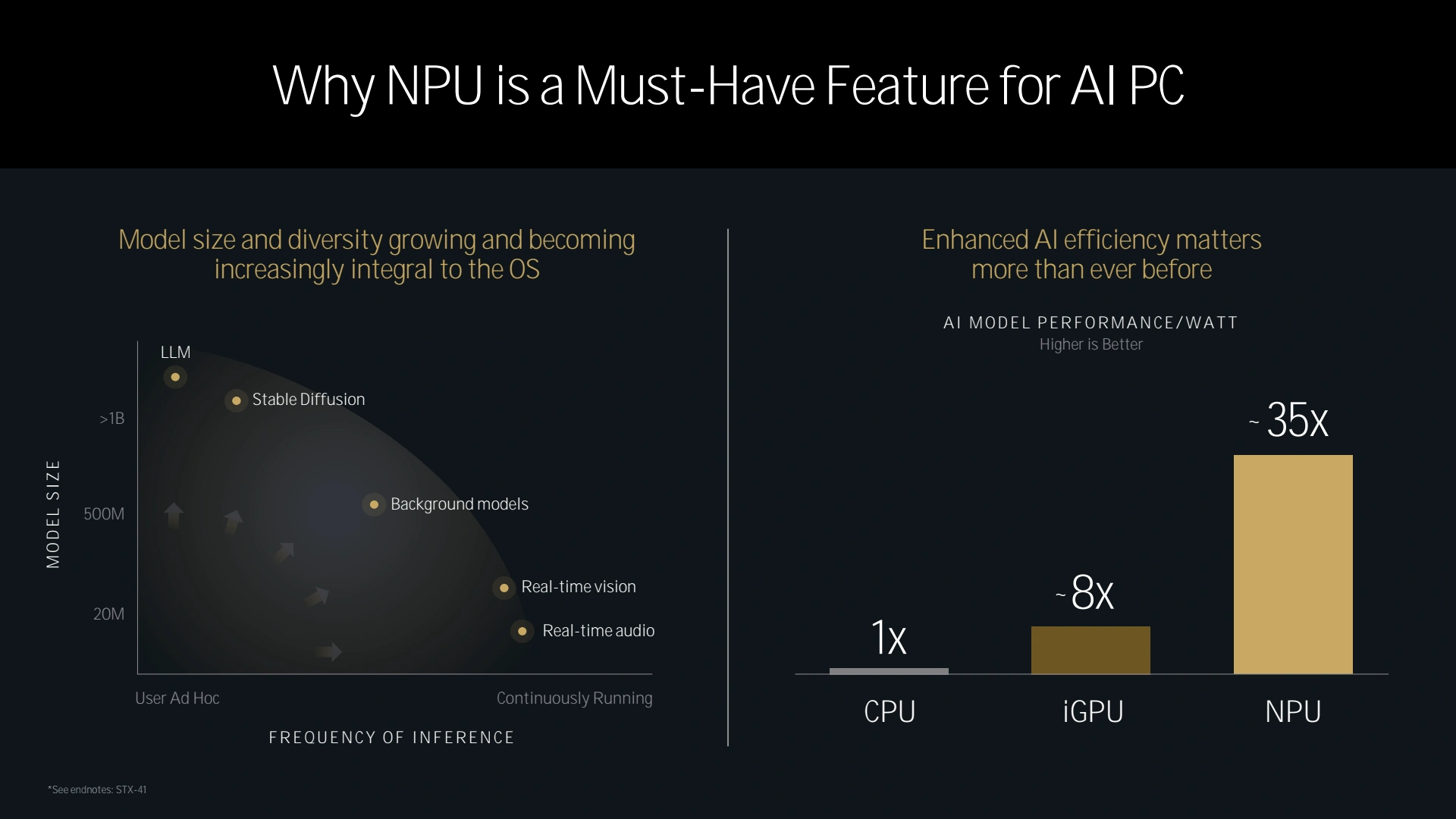

Quid de l'intégration d'un NPU de seconde génération ? Pour rappel, les tâches d'apprentissage ou d'inférence IA ont tendance à être similaires à une partie des calculs réalisés par les GPU pour les rendus 3D. C'est pourquoi ces derniers se sont imposés comme solution préférentielle face aux CPU. Toutefois, un GPU conservant une certaine flexibilité (certes moindre qu'un CPU), une partie de ses ressources matérielles sont inutiles et vont donc générer un surcoût (il faut bien graver sur le silicium lesdits transistors) et une efficience moindre (lesdits transistors ne pouvant pas être complétement inactivés) pour un usage purement IA. Ainsi, les NPU sont concentrés uniquement pour ce type de calcul sans autre forme de flexibilité, ce qui les rend moins dispendieux en termes de transistors et donc plus efficients (de 4 à 35 fois) et moins coûteux qu'un GPU ou CPU pour ces tâches.

Cette ultra spécialisation en fait des ASIC (Application-Specific Integrated Circuit). On pourrait très bien imaginer une puce gigantesque capable de rivaliser avec les plus gros GPU en termes de puissance de calcul brute et bien plus efficients, mais si les modèles venaient à changer drastiquement, son utilité deviendrait nulle. Un pari risqué au prix d'un wafer de dernière génération. Il est donc probable que les NPU ne concurrencent finalement les GPU que pour des exécutions locales et peu gourmandes, mais cela fait sens au sein du processeur central d'un PC portable par exemple. C'est en tout cas l'approche défendue par AMD qui voit un usage bien distinct des CPU/GPU/NPU dans le cadre de l'IA, et probablement l'occasion de rattraper une partie du retard concédé face aux verts.

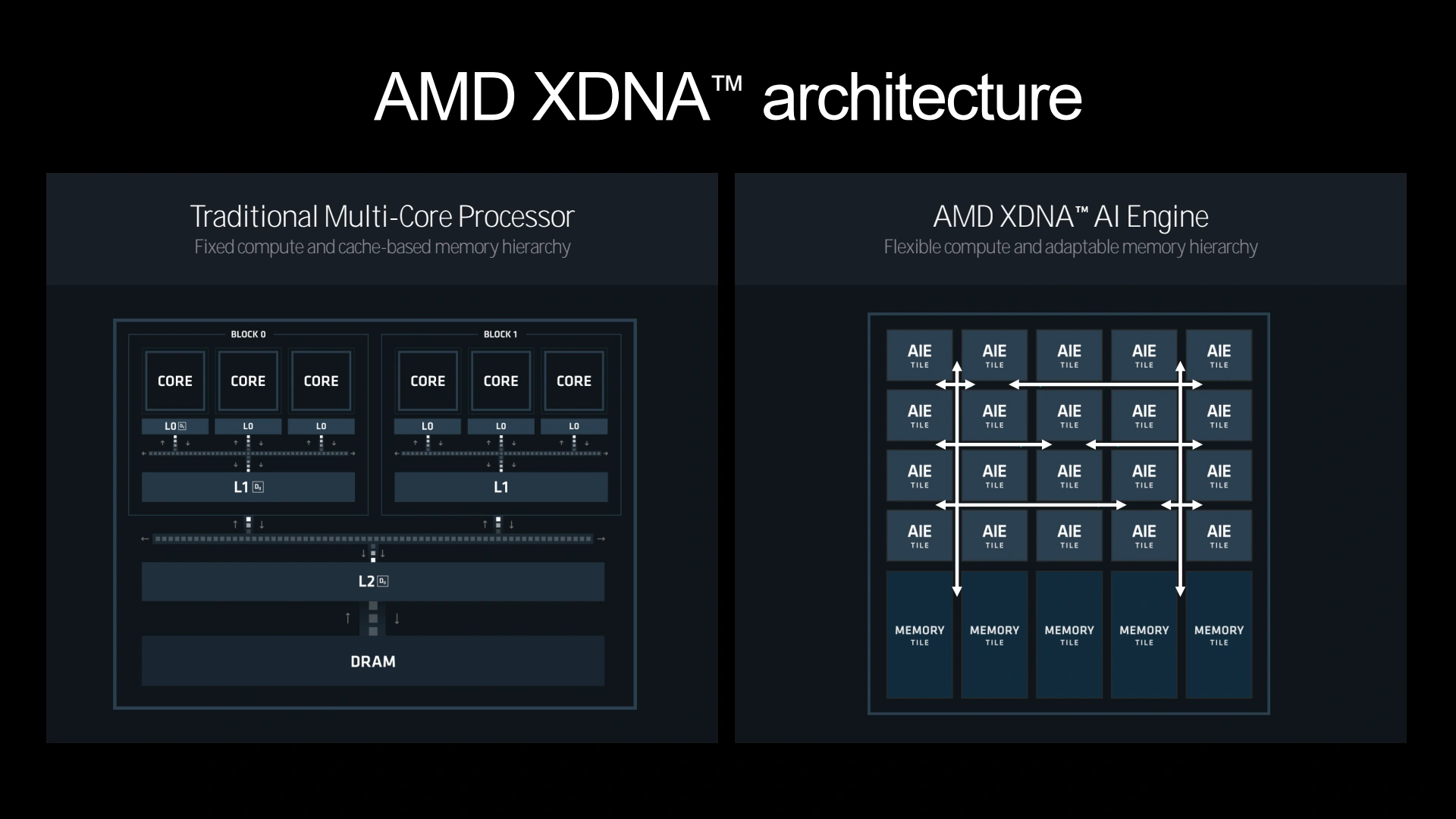

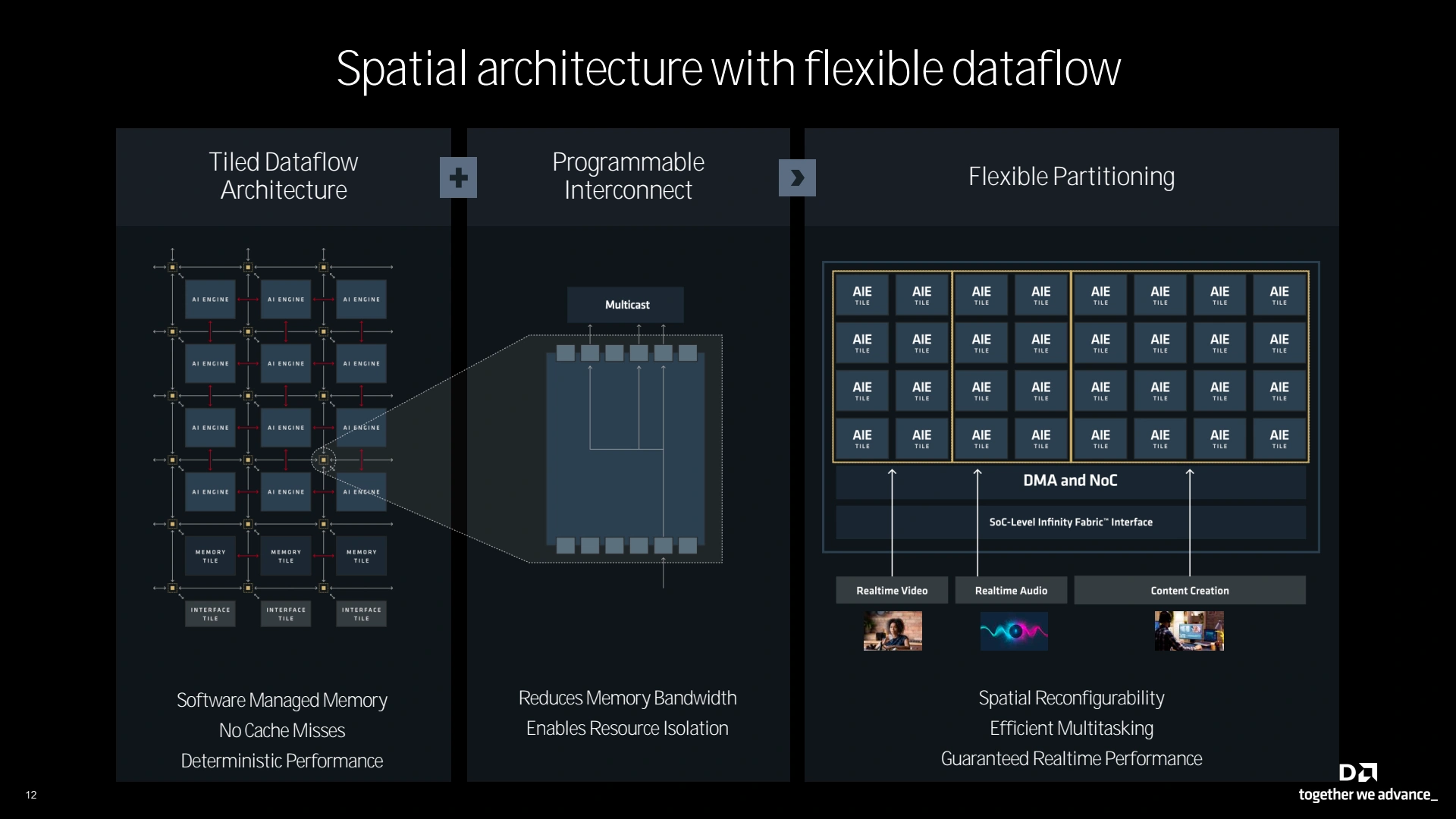

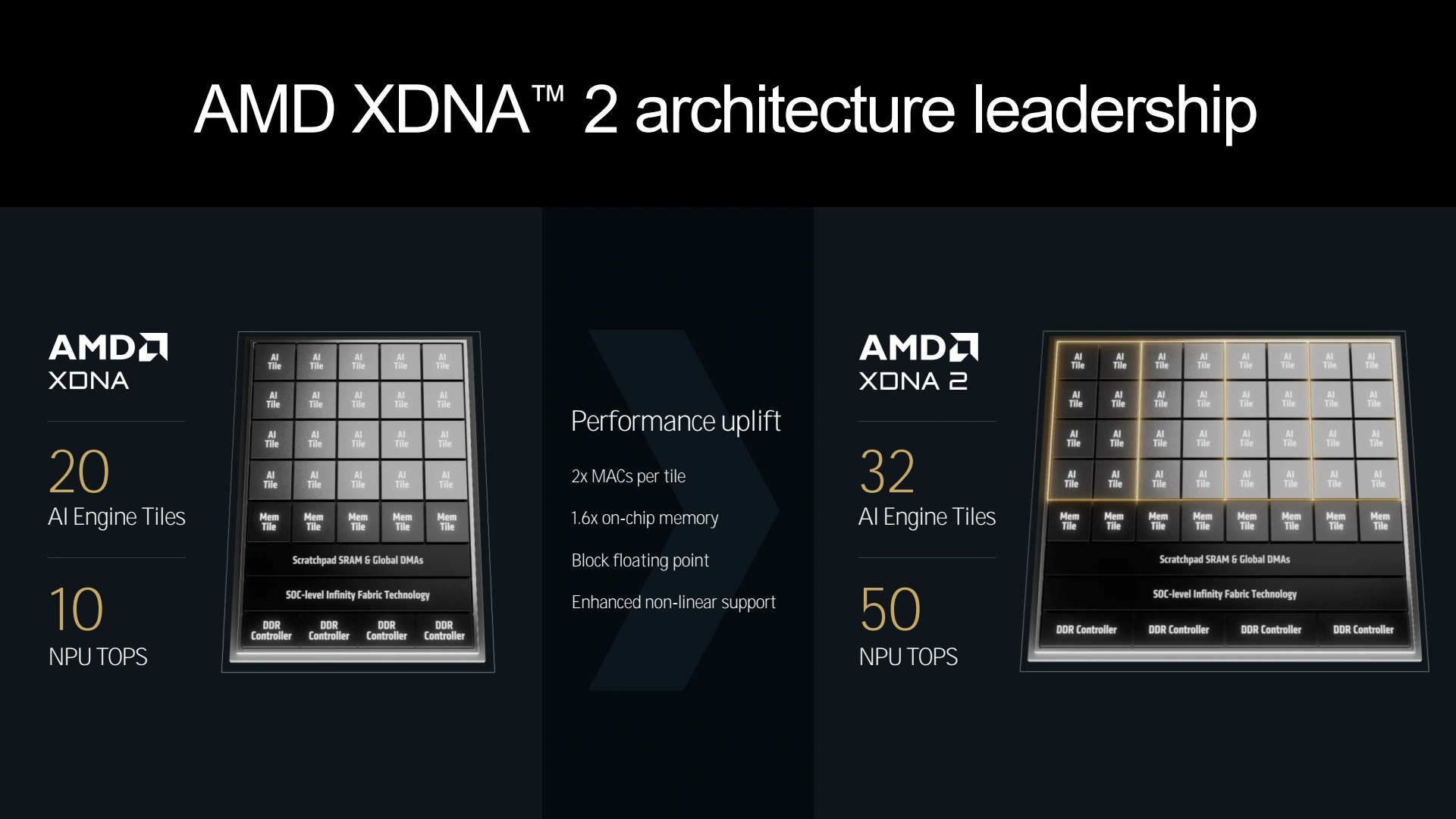

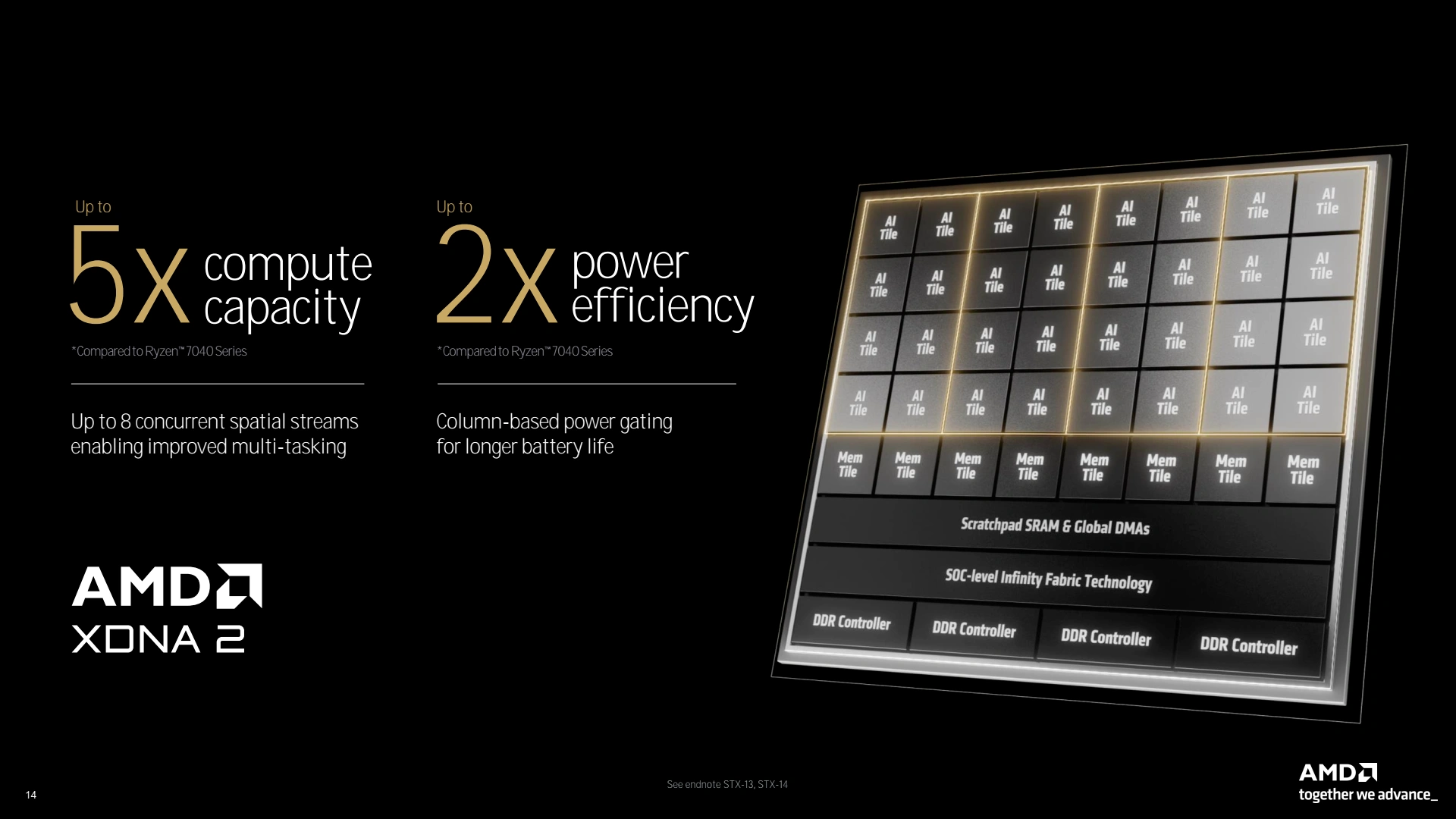

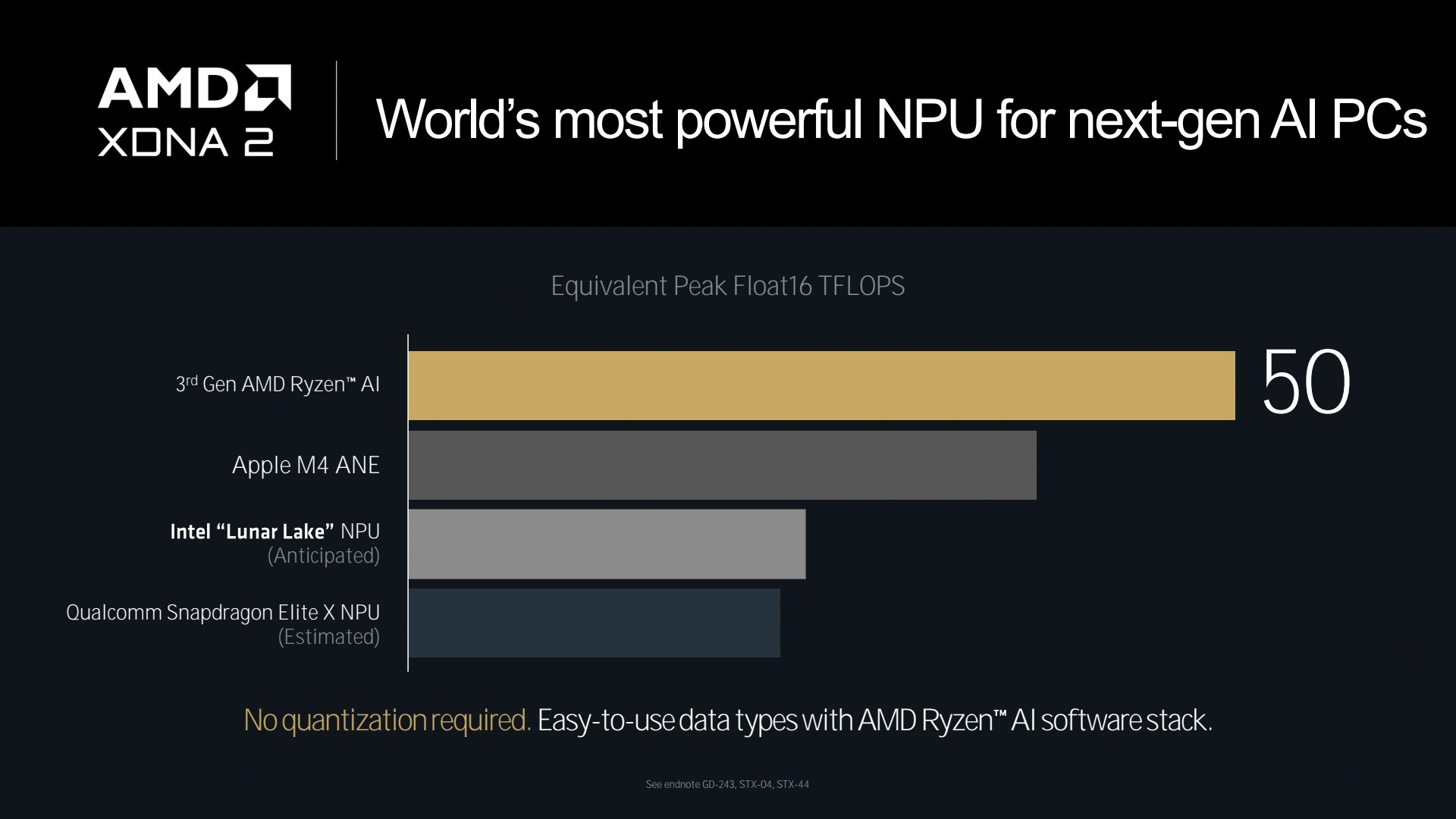

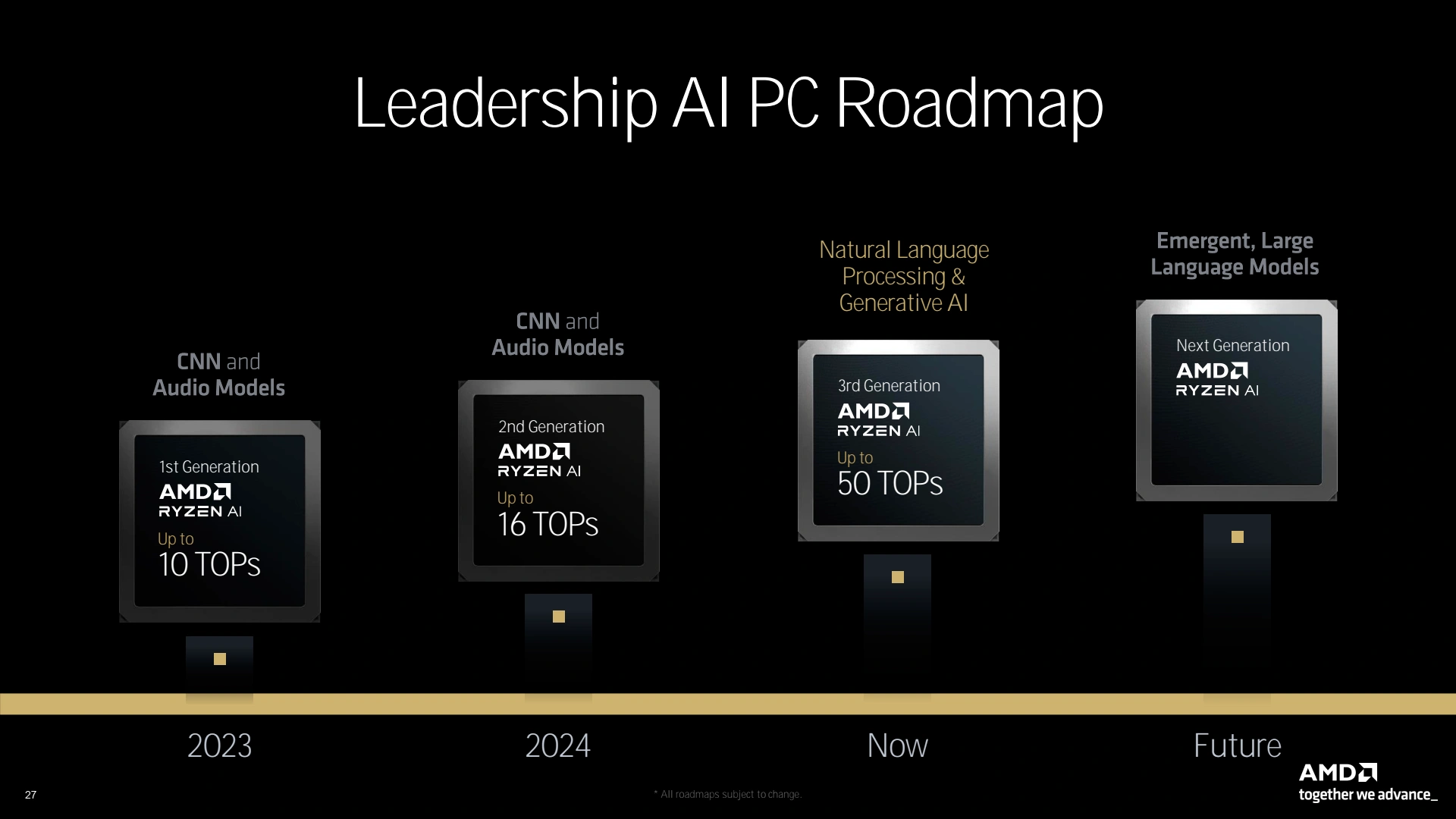

XDNA comme tout bon NPU, n’est rien de plus qu’une série d’unités de calcul matricielles reliées par un interconnect en mesh (on parle alors de réseau systolique) facilitant les échanges de résultats entre les accélérateurs adjacents, ce qui convient parfaitement aux couches d’un réseau appliquant leur transformation les unes après les autres. La génération 2 de XDNA passe à 32 tuiles pour les calculs contre 20 à sa devancière. L'interconnect gagne également en flexibilité ce qui permet de partitionner le NPU pour exécuter individuellement des tâches différentes. Le cache embarqué suit de son côté la progression du nombre d'unités de calcul pour une performance de pas moins de 50 TOPS, ce qui en ferait selon AMD, le NPU le plus performant intégré à un CPU grand public. Cela ne s'arrête pas à ce simple chiffre brute, car les valeurs sont souvent exprimées pour des calculs INT8, or, cela serait cette fois avec une précision équivalente FP16.

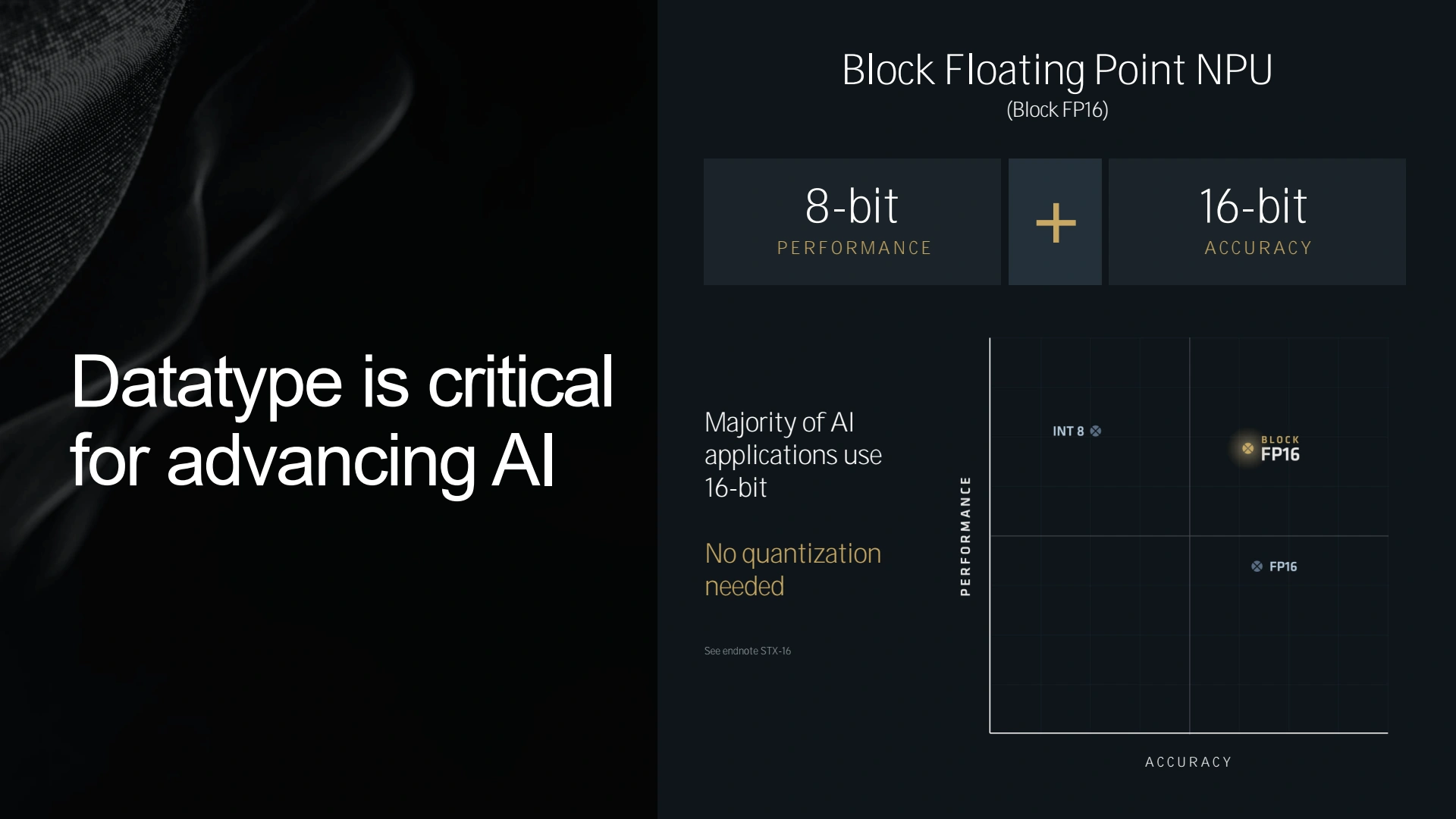

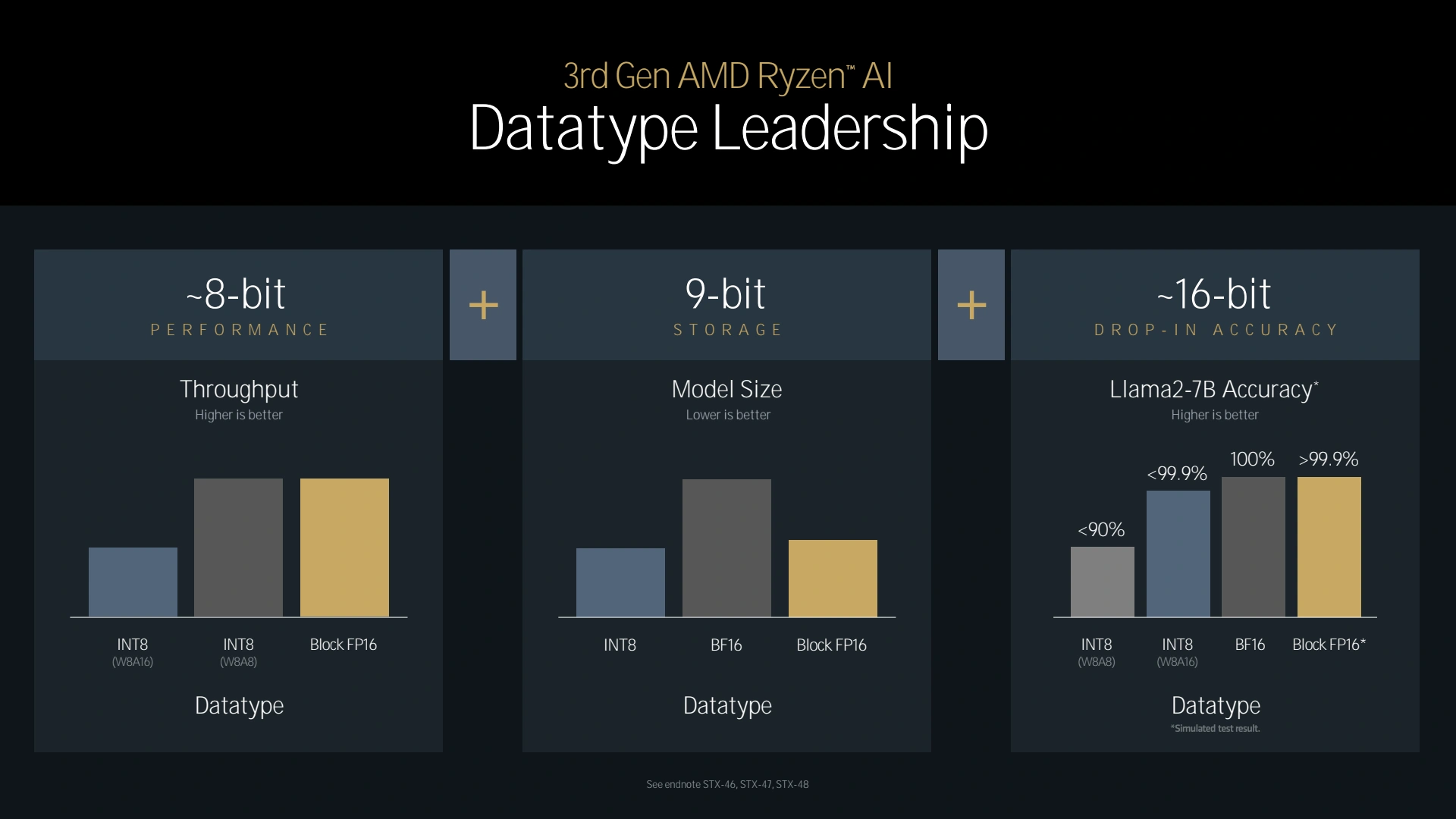

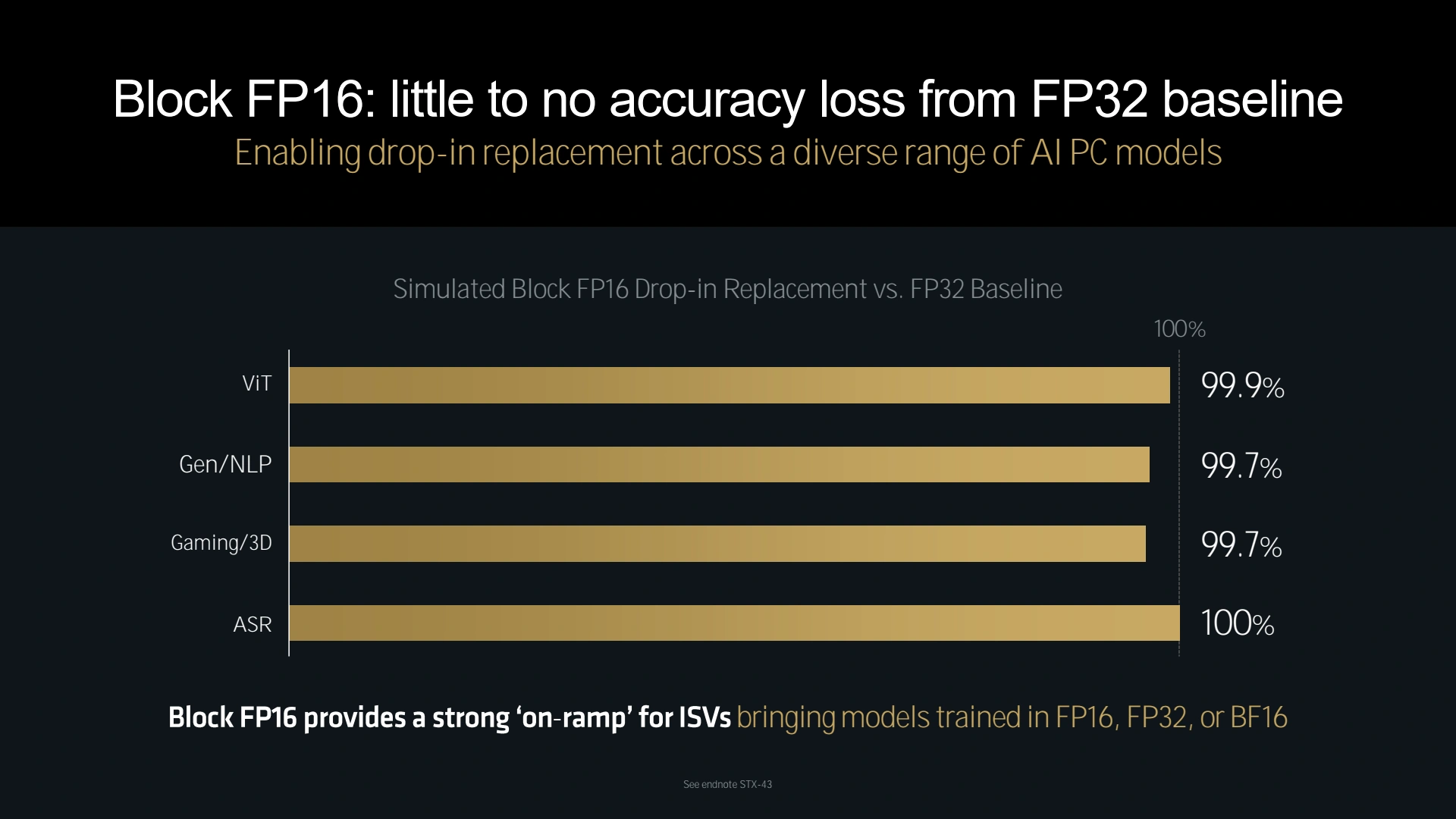

Car la grande force de ce NPU selon ses concepteurs vient de la prise en charge du format Block FP16. Kesako ? Un peu de lecture devrait répondre à cette question. Pour résumer (pour les paresseux), un nombre flottant FP16 est en fait codé de la façon suivante : 1 bit pour le signe (+/-), 7 bits pour un nombre entier que l'on nomme mantisse et 8 bits pour l'exposant qui va lui être appliqué. La formule pour calculer le nombre est donc la suivante : +/- mantisse x 2^exposant. L'astuce du block FP16 est donc de regrouper au sein d'un même block tous les mantisses qui partagent le même exposant, et ils sont nombreux dans le cadre de l'IA. C'est ce qui permet d'obtenir des performances proches de celles obtenues avec des calculs purement INT8, d'une précision proche du FP16 et avec une empreinte de stockage d'environ 9-bit selon AMD (il faut bien codé les blocks et leur exposant unique tout de même) tout en s'affranchissant de l'étape de quantization.

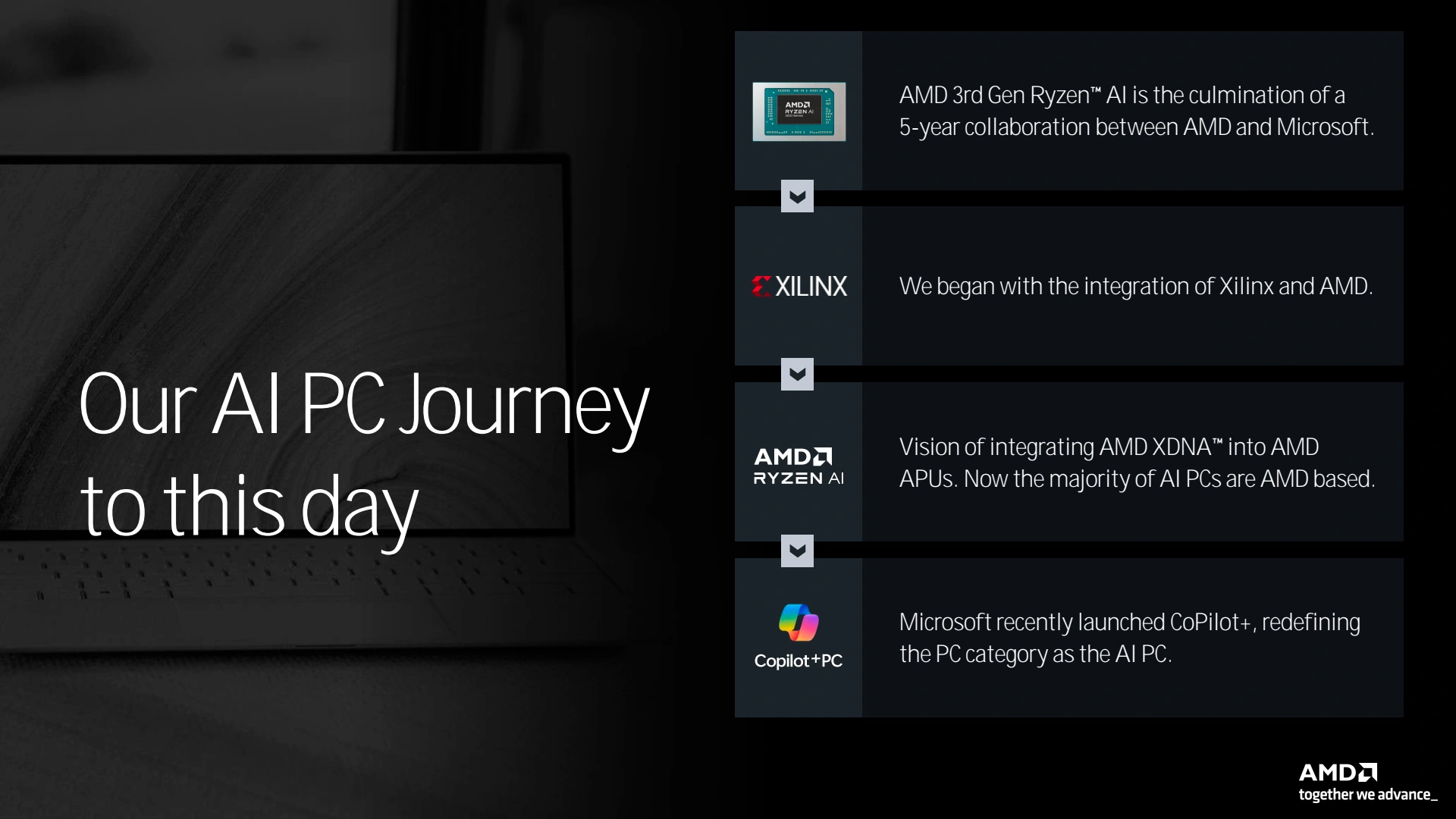

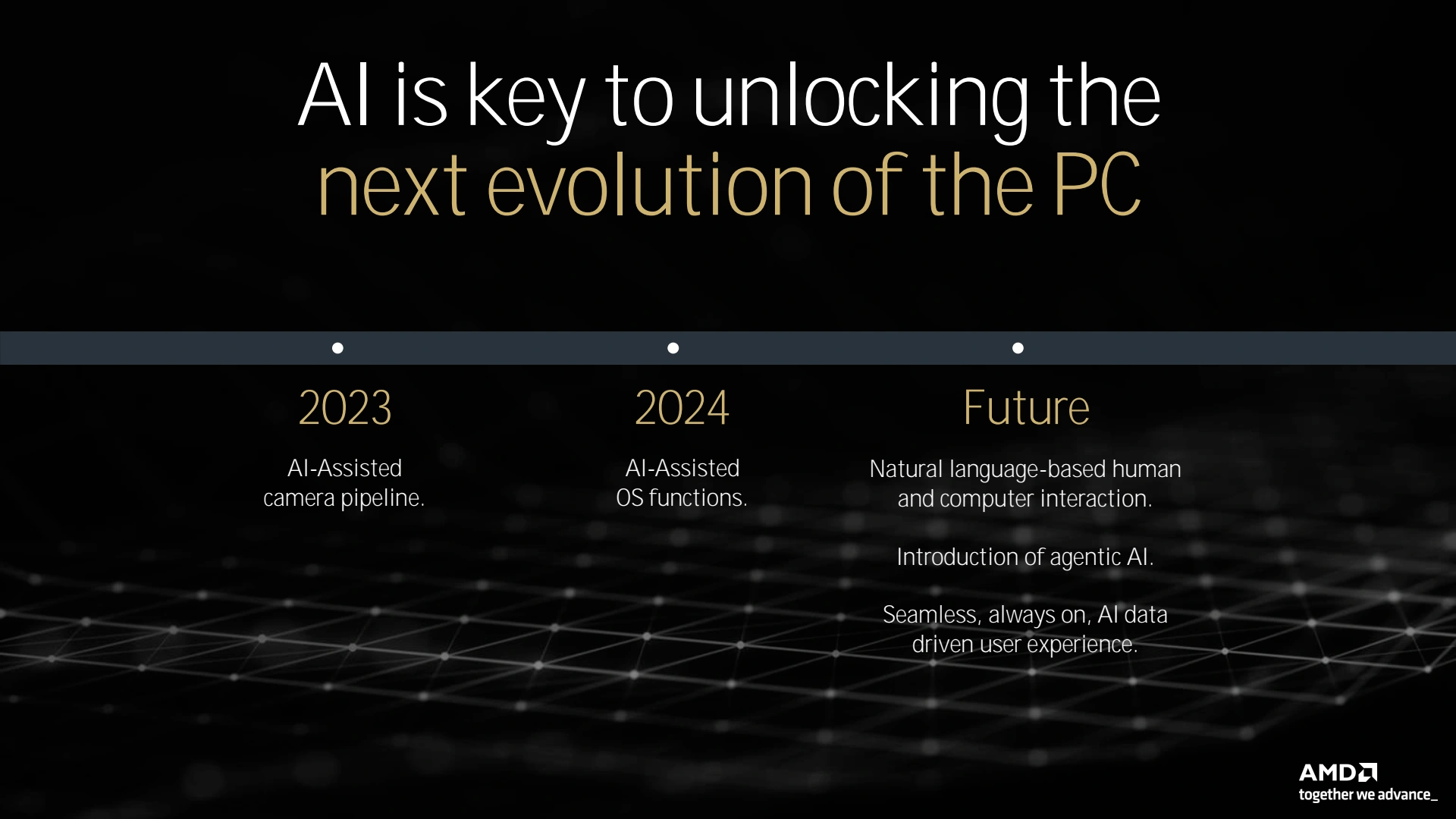

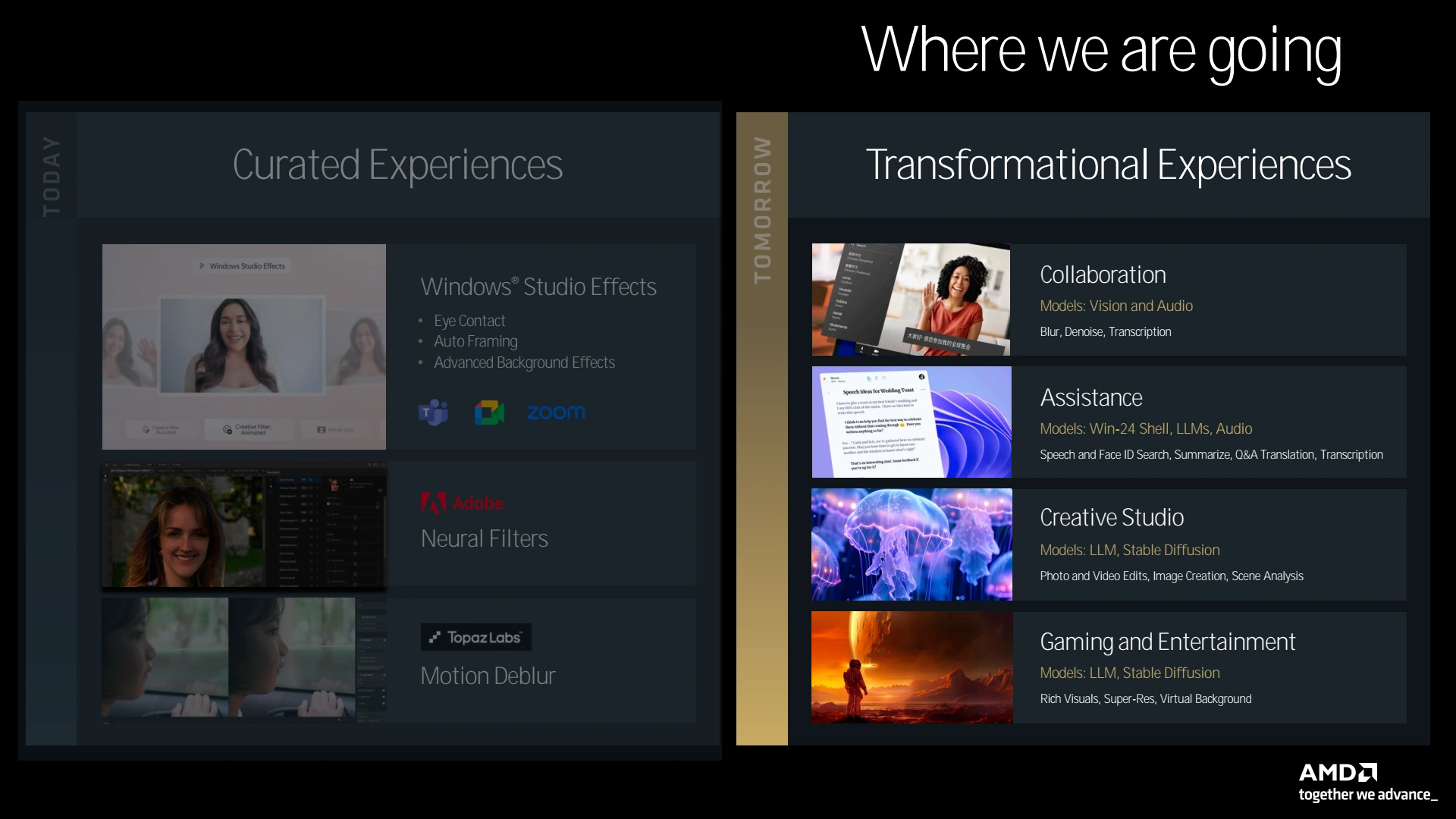

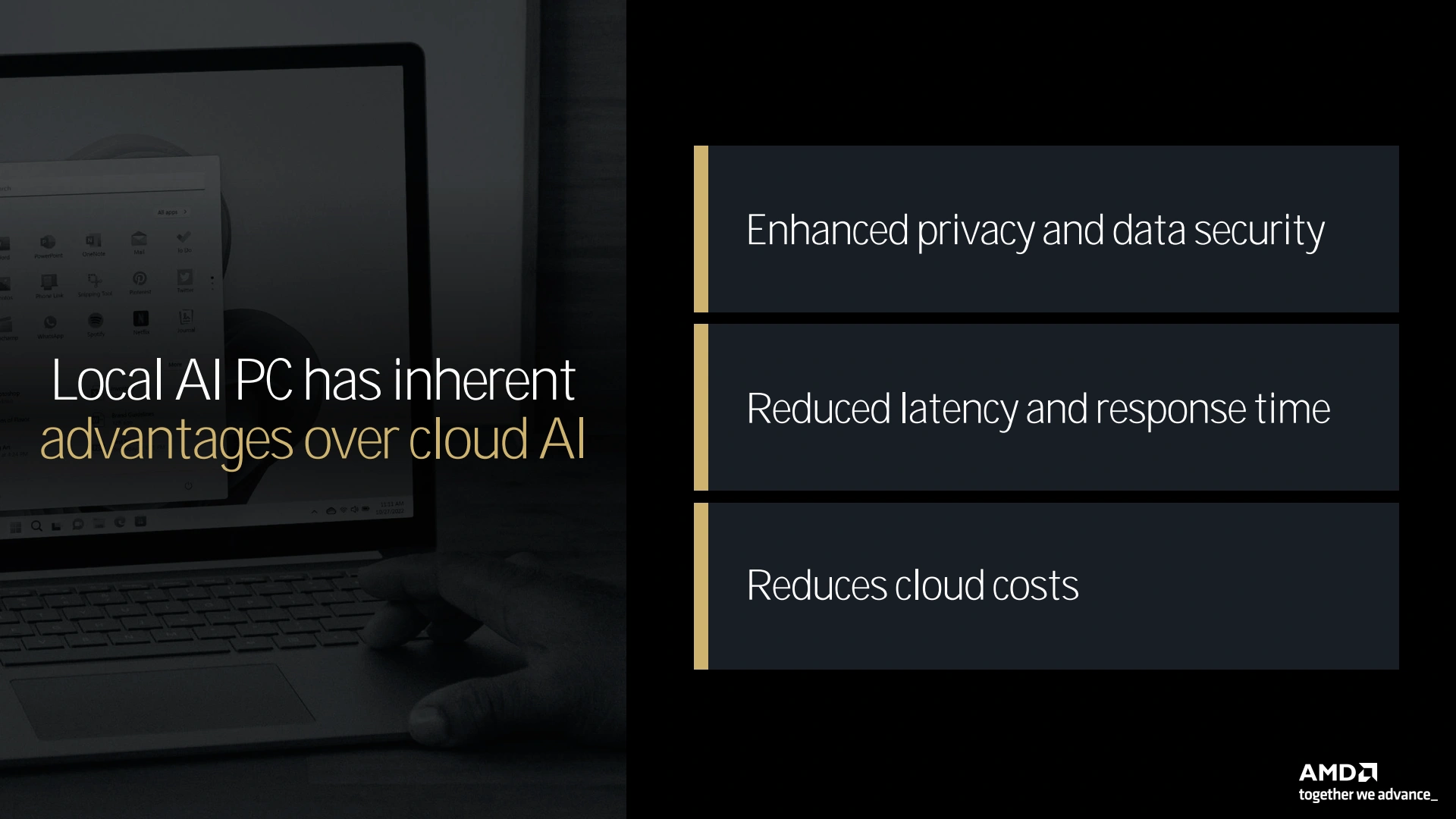

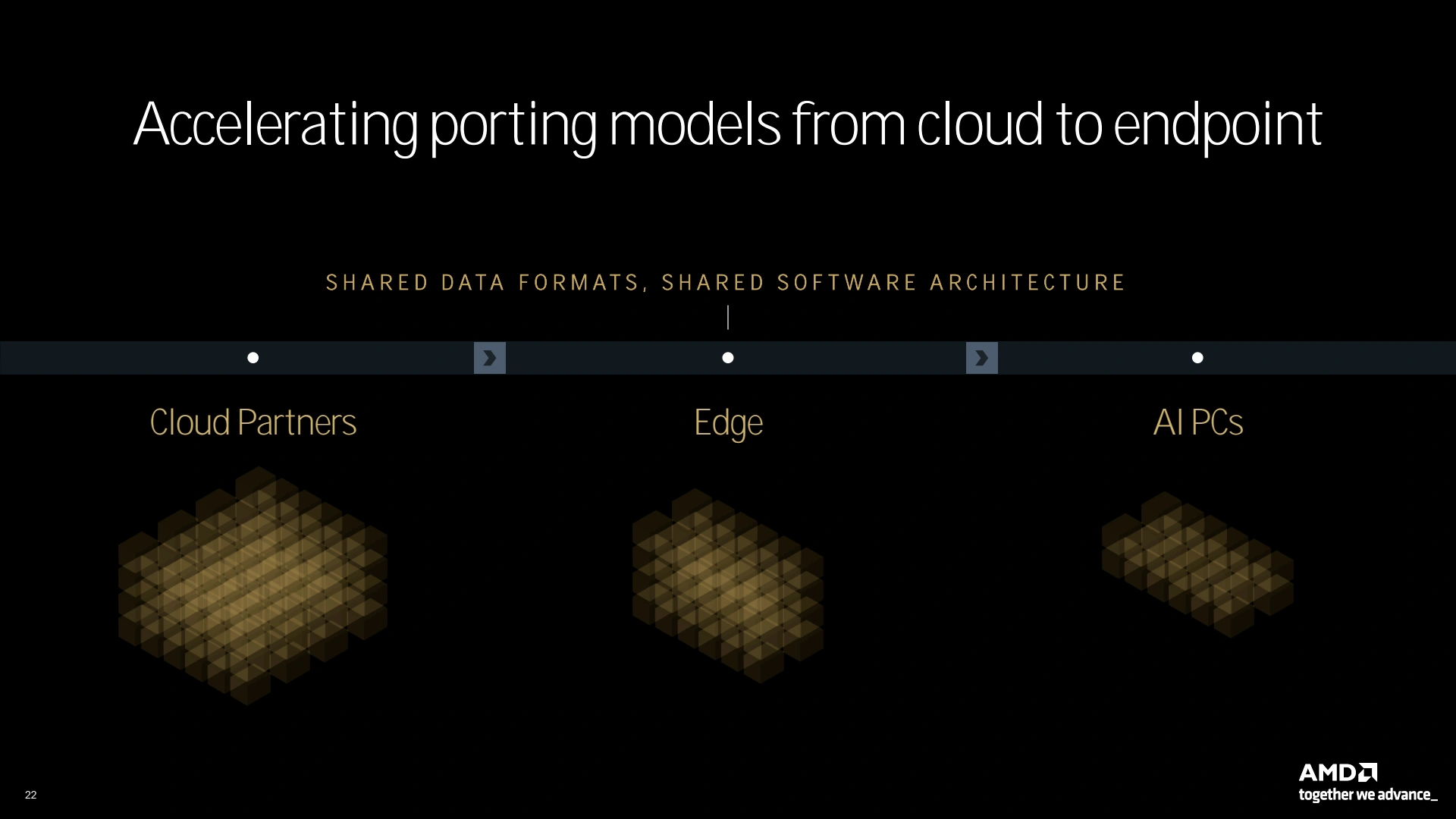

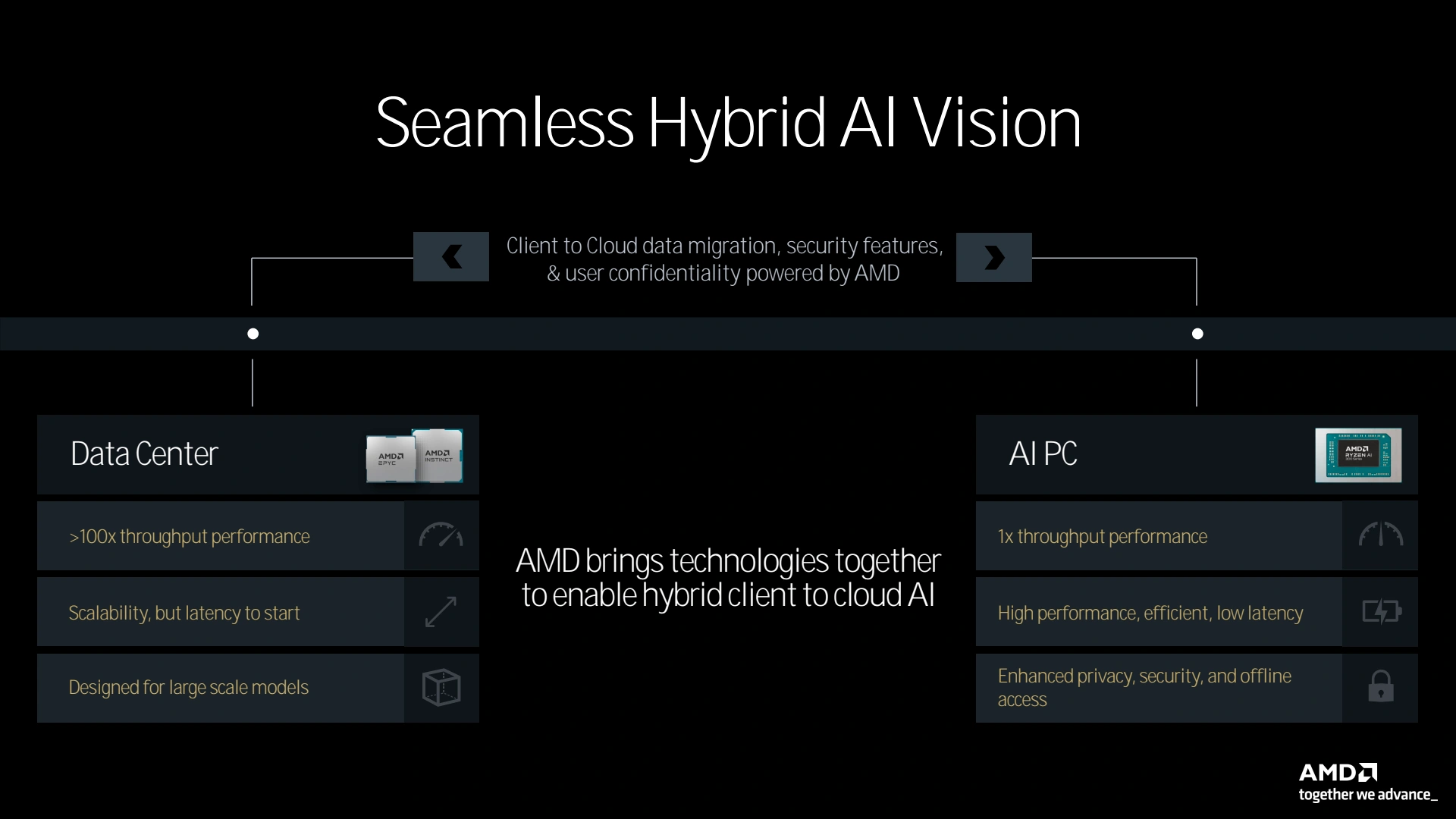

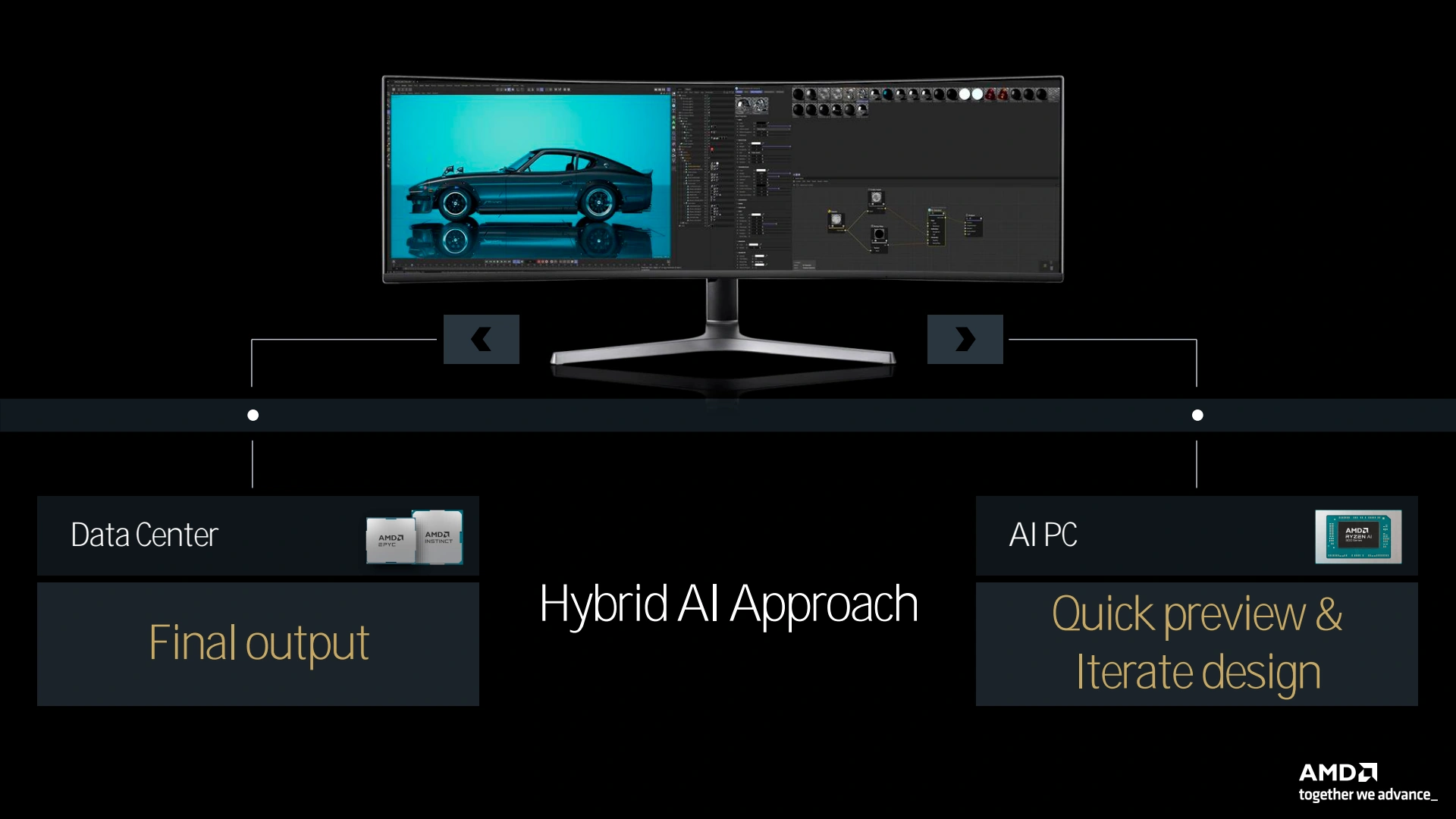

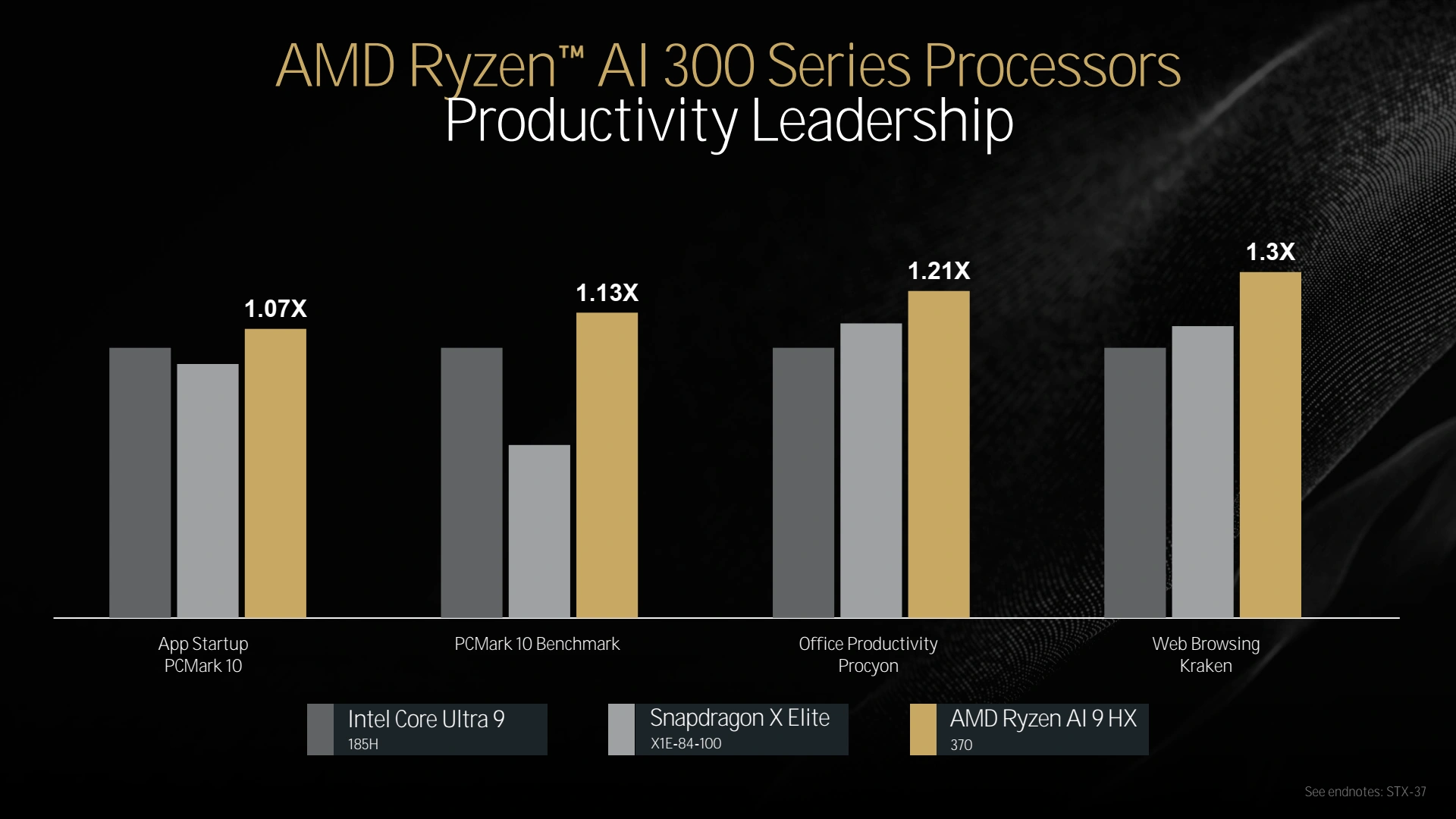

Mais le succès de Nvidia l'a démontré, le nerf de la guerre n'est pas que matériel, loin s'en faut. Il faut proposer les couches logicielles permettant d'exploiter le plus efficacement et simplement ledit matériel. AMD indique donc travailler main dans la main avec les développeurs, en particulier Microsoft. On notera malgré tout que ce dernier a délaissé pour le lancement de Copilot+ les traditionnels acteurs du monde PC que sont INTEL, AMD et NVIDIA, au profit de QUALCOMM et ce même si ce n'est que provisoire. AMD indique travailler également sur une approche hybride permettant dans certains cas de mixer une exécution local de l'IA et une exécution dans le cloud selon la charge et le besoin de confidentialité. Pour finir quelques mots sur les prestations "générales" à attendre des portables Strix Point.

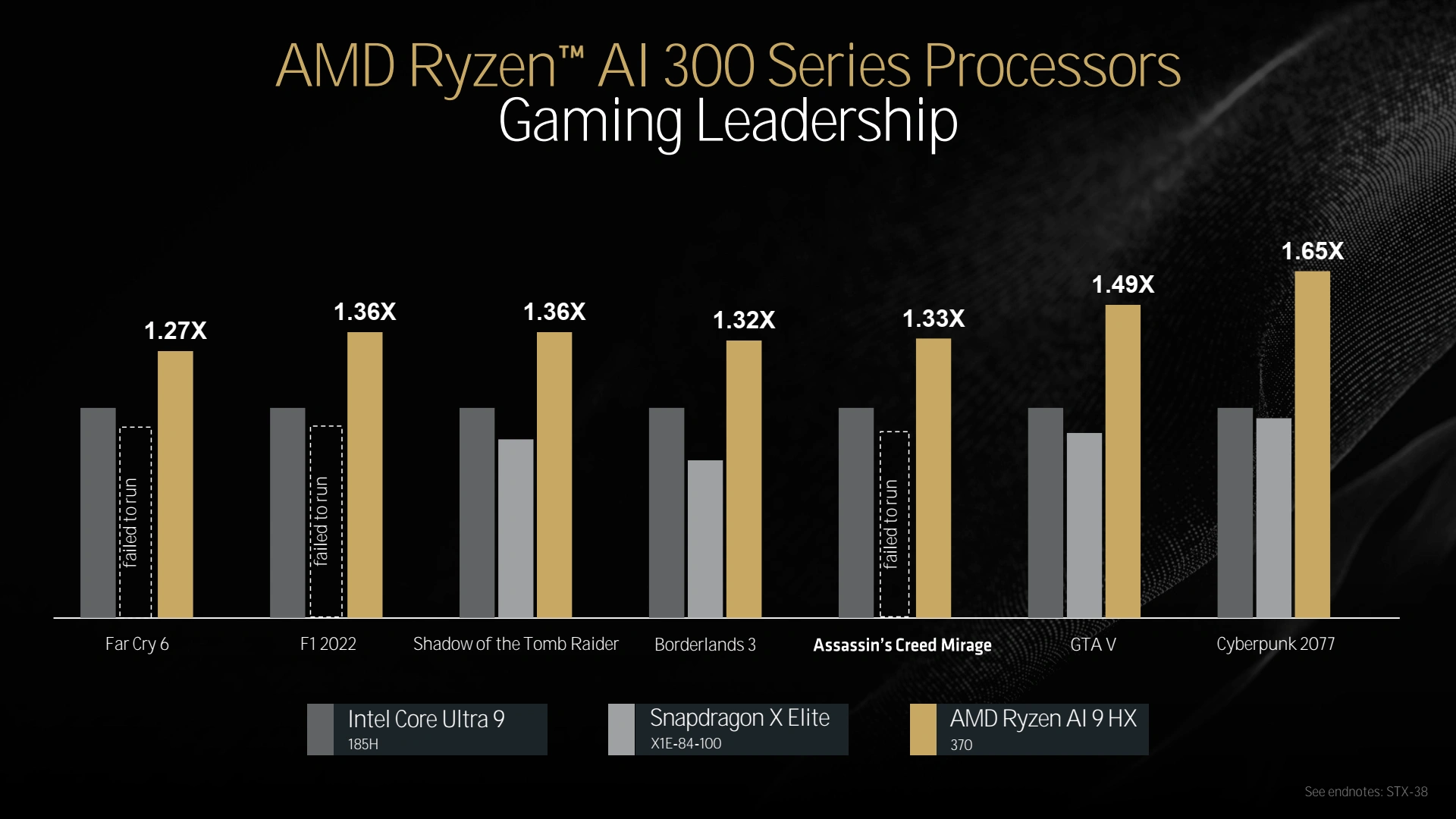

Les modèles exposés semblaient bien équilibrés et performants, avec un avantage substantiel en jeu vis-à-vis des modèles concurrents n'utilisant pas de GPU dédié. Tout cela méritera comme d'habitude d'être vérifié au travers de tests indépendants. De notre côté, nous vous donnons rendez-vous dans quelques jours pour en apprendre un peu plus et vous donner notre avis factuel sur Zen 5.

Pas d'info particulière sur le cache L3? Paraissait (dans des leaks) qu'ils avaient pas mal retravaillé la manières dont les cœurs piochent dedans et se le partage.

Non, c'était bien le chipset le facteur limitant. Sur les 7000, le lien était déjà en Gen 5 côté IO die (pour la totalité des 28 lignes pcie) mais bien de la gen 4 côté chipset. C'est ça qu'on aurait voulu voir évoluer côté ASMedia. Une occasion manqué...

(ils ont même pas osé parler d'Excavator, dans les architectures de l'ère AM4 😅 )

Non, comme indiqué la gamme Desktop a été le parent pauvre de cet event. J'espère davantage d'info d'ici les tests.

Certes, mais il était possible aussi d'imaginer 8 lignes en Gen 4 comme la concurrence si ASMedia voulait s'éviter l'implémentation de la Gen 5 au niveau du chipset, mais bloqué par le CIOD cette fois. A priori l'une comme l'autre solution n'ont pas trouvé grâce aux yeux des concepteurs .

Oui, pourquoi pas sur les version E. Sacrifier un m2 pour coller chacun des deux Promontory sur 4 lignes exclusives, ça aurait pu être une configuration intéressante. Mais ça n'aurait été qu'une question de choix marketing, pas besoin de modifier l'IODie pour cela. Par contre, passer de 28 à 32 lignes pcie, là ça aurait nécessité un nouveau socket (peut-être pour AM6?), parce que je doute qu'ils aient prévu du rab sur AM5.

(ahah, excellent ma citation dans la boîte de coms. Mes cours de latin 😍)

Vraiment hate de voir en 2025, les laptops Zen 5 avec des GPU dédié AMD sous RDNA 4.

Hello,

Est-ce qu'il y a dans les petites lignes de la présentation (on voit des refs à certaines notes parfois) des détails sur la puissance de calcul présumée des NPU RDNA2 ?

Nan parce que là comme ça, 50 TFLOPS 16 bits équivalents (bon, déjà ça ne veut pas dire grand chose) j'ai un peu de doutes. C'est quand même plus que la puissance de calcul présumée d'une NVIDIA A40, donc si jamais on a la magie (ou la triche employée sur le nombre) ça serait intéressant. Même si ça parait un peu gros quand même, juste à la fois curieux et dubitatif sur ces chiffres.

On part de 10TOPS pour les 7000 (celle-là on est bon, t'y crois?), à 16TOPS pour les 8000, après overclocking, puis à 25.6TOPS sur les 9000, en passant de 20 à 32 tuiles, et peut-être 51.2 TOPS en prenant en compte le 2x MACs (késako?) per tiles?

Sinon va faire un tour chez Anandtech, ils ont souvent les diaporama complet, avec la totalité des slides (dont les footnotes), à la fin de leurs articles.

Mais les TFLOPS de RDNAx et les TOPS de XDNAx ne doivent pas être comparable, ça c'est certain.

Le soucis, c'est que sur les générations précédentes, on parle de TOPS en 8 bits entiers, là on parle de TFLOPS en 16 bits flottants, niveau calculatoire c'est extrêmement plus élevé. C'est là où sans le détail complet, ça peut faire très rapidement plus chiffre vendeur que réalité sur le terrain (comme souligné dans l'article, il faut voir l'effort côté logiciel).

Alors oui, ce n'est pas équivalent (et j'ai fais un lapsus entre RDNA et XDNA dans le post d'avant, quel con ><), n'empêche que ce sont quand même des gros chiffres pour du co-processing, ça serait bien d'avoir toutes les conditions du fabricants qui permettent d'y arriver.

Et je suis allé chez Anandtech, il n'y a pas le détail sur l’article concernant la même actualité 😢

Normalement, c'est 50 TOPS officiellement. Et oui, en entier 8bits.

Après, possible qu'ils aient lâché un 50 TFLOPS sur une de leur slide (je ne l'ai pas vu passé). Là, la magie doit probablement venir de leur Block FP16, presque aussi rapide que leur INT8 et presque aussi précise que leur FP16, affirment-ils (5ème paquet de slides, slide 8 et 10/11). Toute la magie est expliqué sur l'autre article d'H&C, référencé dans le billet.

Je les ai trouvé, les notes de la partie IA. C'était cette fois explosé en plusieurs diaporama (9499 à 9502). Et si ils étaient tous en ligne (enfin, il me semble qu'il manque tout de même ceux de la partie gpu), ils ne les avaient pas tous référencé dans leur articles.

https://www.anandtech.com/Gallery/Album/9502#29

Ils parlent bien de mesure en 'Block Floating Point'

Ah yes, merci beaucoup (désolé, étant en vacances j'ai pas l'occasion de regarder mes mails et internet si souvent que ça).

Il faudra voir sur le terrain ce que ça vaut, il y a plusieurs fois des "projected" pour les performances, et aussi à quel point ces block floating point unit sont si efficace (j'ai lu l'article d'origine fait par Nico, mais comme tout bon papier de recherche, j'attend de voir ce que ça donne au final).

L'autre point c'est d'espérer que cela ne sera pas trop complexe à utiliser aussi, par exemple s'il faut réentrainer, modifier profondément le code etc... Bref, sur le papier très intéressant, mais tant que ce n'est pas sorti pour de bon, le domaine de la recherche sur le ML m'a bien appris une chose, c'est d'être patient et voir la finalité.

Les "projected", je crois qu'ils font référence à Lunar Lake et d'autres processeurs pas encore sortie (snapdragon). Ils se "projettent" en tête, mais faudra attendre leur sortie pour confirmer.

Si les calculs se font en 8-bits la grande majorité du temps, et que l'exposant n'est calculé qu'une fois tous les 16 ou 32 coefficients, ça peut ne pas être déconnant.

Et à priori, les coefficients FP16 peuvent être converti en Block FP16 sans trop de perte, d'après ce que j'ai compris. Pour le reste, à voir... Mais si ça s’appuie des travaux de Microsoft, il devrait à priori déjà y avoir un peu de support côté soft.