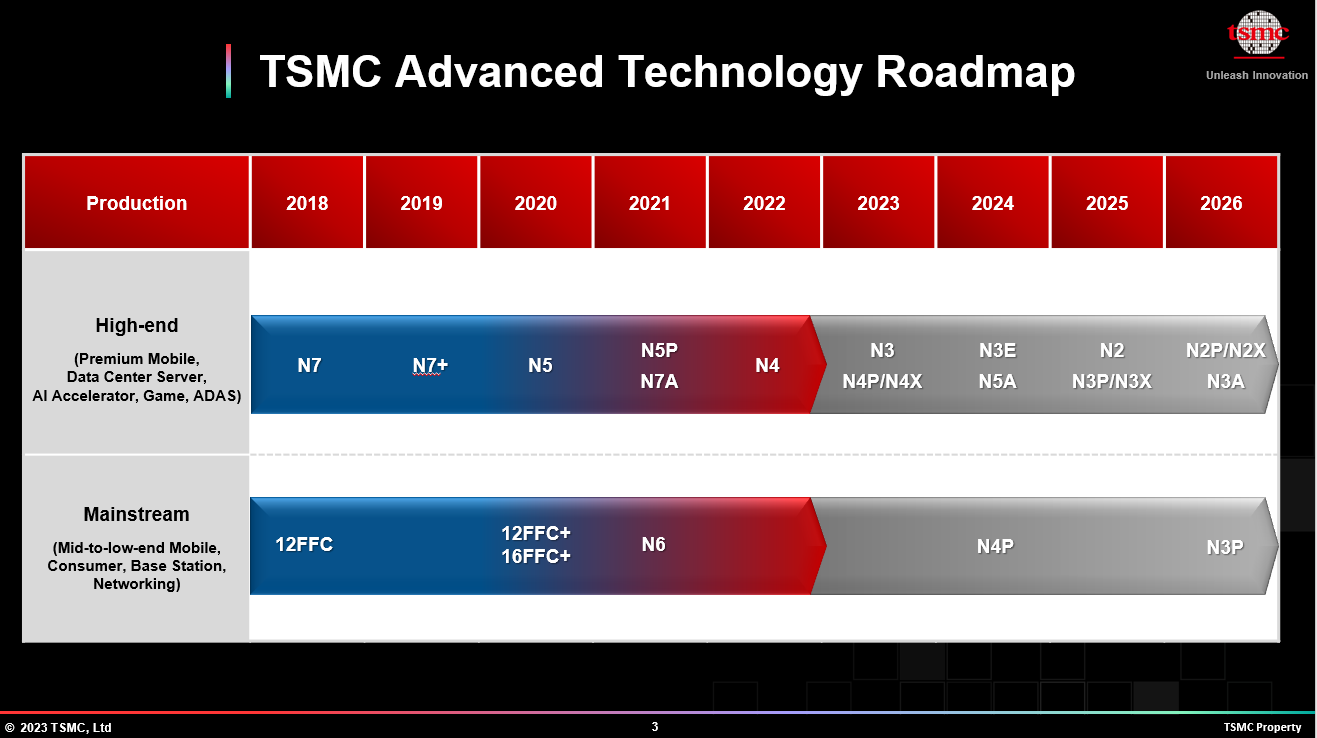

TSMC a profité d’un salon aux USA pour clarifier, rappeler ou encore donner plus de détails sur ses projets en matière de processus de fabrication, objets d’une lutte très intense entre les 3 derniers participants — à savoir TSMC, Samsung et Intel — dans cette course de plus en plus laborieuse et couteuse. Chez le fondeur taiwanais, ce sont le 3 nm et le 2 nm qui sont attendus de pied ferme. Commençons par le 2 nm, ou plutôt la génération N2. Il n’y aura pas qu’un procédé de classe 2 nm, mais plusieurs variations comme le fondeur a désormais l’habitude de le faire. Le N2 initial est planifié pour entrer en production de volume en 2025 et il sera le premier chez TSMC à utiliser des transistors gate-all-around ou GAA, surnommés Nanosheet chez le Taiwanais. Il offrira une densité mixte supérieure à 15 % par rapport au N3E. Deux variantes du procédé sont ensuite déjà planifiées pour 2026, année où elles devront normalement entrer en production.

D’abord, le N2P, qui introduira un système de lignes d’alimentation par le bas, la fameuse Backside Power Delivery, que l’on connait aussi sous le nom de PowerVia chez Intel. Celle-ci permettra d’améliorer les performances et la consommation des transistors Nanosheet, mais aussi leur densité. Hélas, mais c’est assez compréhensible, TSMC ne donne encore aucun chiffre très précis quant aux avantages du N2P par rapport au N2 original. À noter que TSMC accusera donc théoriquement d’un retard d’environ deux ans pour l’intégration de cette technologie face à Intel - certes, en supposant que le fondeur américain y arrive en 2024 avec son 20A comme il le planifie toujours. Enfin, TSMC prépare aussi un N2X, un node spécialisé pensé spécifiquement pour les usages et les besoins en high-performance computing (HPC). Les bénéfices de celui-ci dépendront a priori avant tout du niveau de la design technology co-optimization (DTCO), en somme du travail de co-optimisation effectué pendant la conception de la puce à fabriquer sur le procédé.

La nouvelle feuille de route permet aussi de découvrir les domaines d'usage prévus pour chaque procédé et doncd'avoir une petite idée de ce qui nous attend côté CPU et GPU.

Mais avant le 2 nm, c’est d’abord au 3 nm de jouer, aka la famille N3. Pour rappel, c’est la dernière génération à base de transistors FinFET pour TSMC. Le fondeur pense que celle-ci restera en service pendant de longues années, notamment pour servir une clientèle qui n’aura pas nécessairement besoin des prochains procédés de pointe à base de GAA. Comme toujours, il n’y a pas qu’une seule proposition au menu, mais quatre : N3 (aussi nommé N3B), N3E, N3P et N3X. TSMC avait aussi brièvement parlé d’un N3S avec une densité maximisée l’année dernière, mais le fondeur n’en a pas reparlé depuis. La production en volume du N3(B) a en principe déjà commencé fin 2022, mais aucune puce l’exploitant n’est encore arrivée sur le marché. Il se dit parfois encore que les rendements ne seraient pas exceptionnels. Difficile de savoir si c’est vrai, ou pas. De toute façon, de nos jours avec les fondeurs, tout est toujours on schedule comme ils disent…

Le N3P sera un « rétrécissement optique » du N3E avec des transistors améliorés, pour des performances supérieures, une consommation réduite et, bien entendu, une densité augmentée. Quant au N3X, il aura pour vocation d’offrir des performances « extremes » (d’où le « X ») en permettant des fréquences plus élevées — a priori + 5 % par rapport au N3P — pour certaines puces hautes performances, notamment les processeurs. De plus, TSMC affirme que les voltages pourront monter au moins jusqu’à 1,2 V avec le N3X, ce qui ne parait pas beaucoup dit ainsi, mais représentera apparemment un chiffre assez extrême pour un procédé de génération 3 nm. En attendant, le procédé qui concernera le plus grand monde et intéressera en principe le plus les clients de TSMC devrait être le N3E, avec ses caractéristiques un peu relâchées par rapport au N3B, et il serait actuellement aussi (évidemment) en bon chemin. (Sources : Anandtech, Anandtech)

On apprend que c'est le n4p qui sera la prochaine gravure "économique"

J'ai peur qu en 2024 seul apple soit en 3 nm

C'est bien dommage

C'est effectivement l'un des plus gros client.. Et en réservant les lignes pour les prochains Smartphones, il cannibalise les chaines de prod'..

Il a même pas besoin de canibaliser

Les rendements sont moyen d'après les fuites et wafer sont hors de prix

Faudra attendre le n3e qui n'est pas encore prêt

Tu as raison je parlais de la chaine N5 my bad, on verra par la suite..

Pour les rendements, il y a à boire et à manger. D'un côté on nous dit qu'ils sont meilleurs qu'espérer, et de l'autre, que les rendements des puces Apple sont mauvaises.

Mais en fait, EE Time (qui est la source de la plupart des articles sortie sur le sujet), juge que ces 55% sont plutôt normal, à ce stade de production, et qu'ils augmenteront progressivement. C'est surtout Apple, qui a des besoin considérable, et le taïwanais n'arrivait pas à suivre.

Et les prochaines machines ASML pourrait aussi changer la donne, en 2024, pour le N3E. Côté tarif notamment.

Ouai, snif aussi que Zen 5 ne sortirait qu'en N4. Le N3 ira probablement pour les Zen 5d et les APU, comme ce qu'on a vu avec le 5nm/4nm...

Pourquoi dommage ? Qu'est-ce qui presse tant finalement à passer au 3 nm ? 🙂

Et je préfère que ce soit Apple qui fasse cobaye qu'AMD ou NVIDIA 😄

Bah parce que sens nouvelle gravure dur d'évoluer

Selon certains spéculateurs, AMD devrait en resté à 8c par CCD avec ses Zen 5. Selon leur ouï-dires, le gain en densité du N3 serait moins bon qu'espéré.

Mais peut-être que simplement la raison en serait de leur choix de rétropédaler pour du N4, en fin de compte (car incapable de pousser les coudes et se faire une petite place à côté d'Apple, sur les bonnes lignes).

Donc oui, là l'impasse du N3 pourrait nous coûter une nouvelle petite augmentation du nombre de cœurs, pour la prochaine gen (sauf à y caser un ou deux chiplets de Zen 4d/Zen 5d).

On parle d'une utilisation du 3 nm pour les gpu en 2025 se qui va repousser la nouvelle gen

On était depuis un moment sur un rythme de nouvelle gen tout les 2 ans

Testa 2012 Fermi 2010 Kepler 2012 Maxwell 2014 Pascal 2016 Turing 2018 Ampère 2020 Ada Lovelace 2022 Blackwell 2025 ?