Bien qu’Intel soit principalement connu par le grand public pour son expertise dans le domaine des CPU, là n’est pas le seul secteur d’activité de la firme. Outre la fonderie — dont vous avez entendu parler à tort et à travers ces derniers jours —, les bleus ont également des pièces dans le domaine de l’IA avec Gaudi, ou des FPGA avec Altera. Alors, quand une implémentation de ces puces reprogrammable nous est présentée à l’occasion de l’événement Intel Foundry Direct Connect, nous pensons évidemment à cette dernière… mais non ! Chou blanc, c’est un Brian Faith, PDG de Quicklogic, qui est venu nous causer de ces puces peu connues.

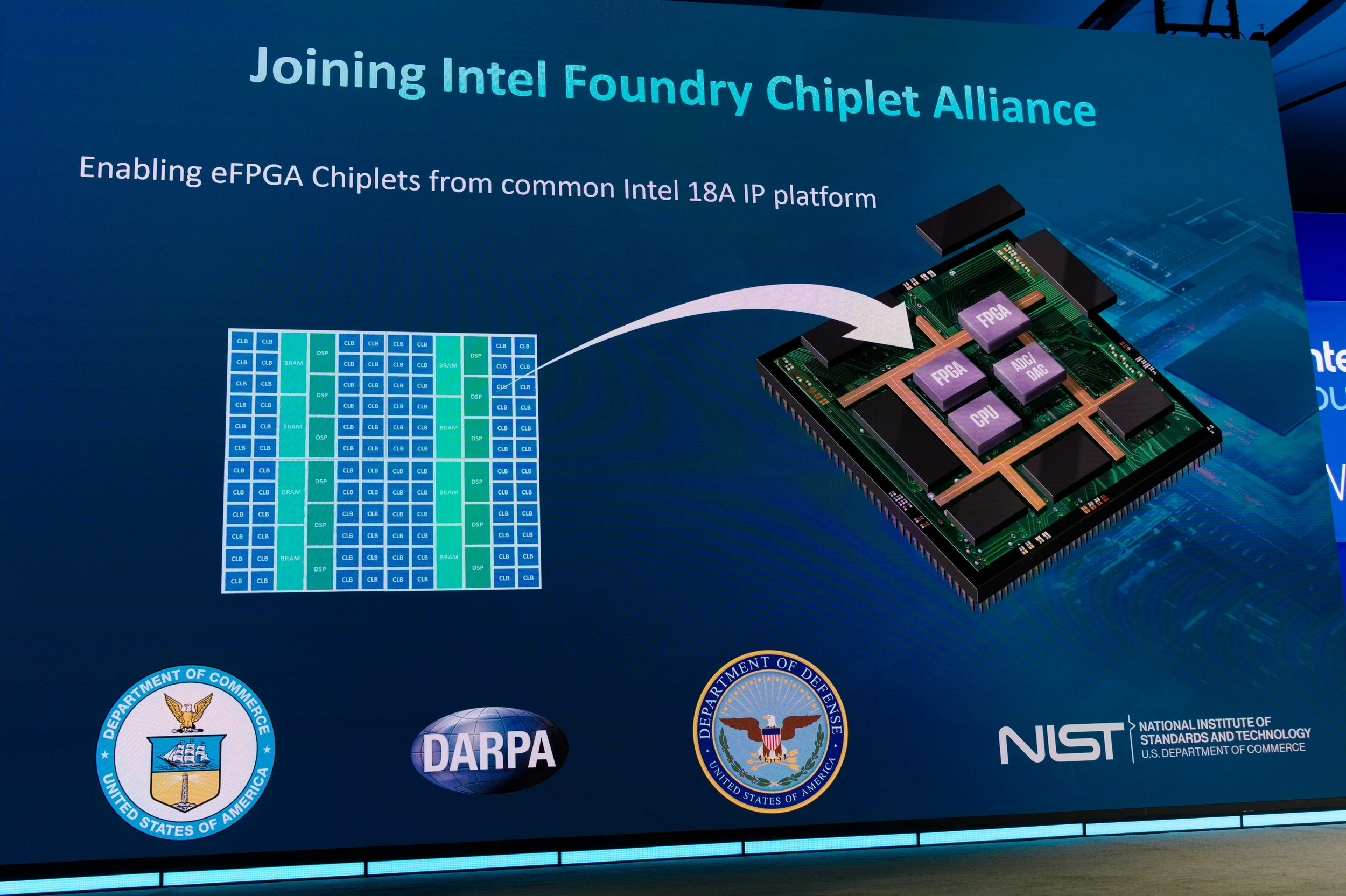

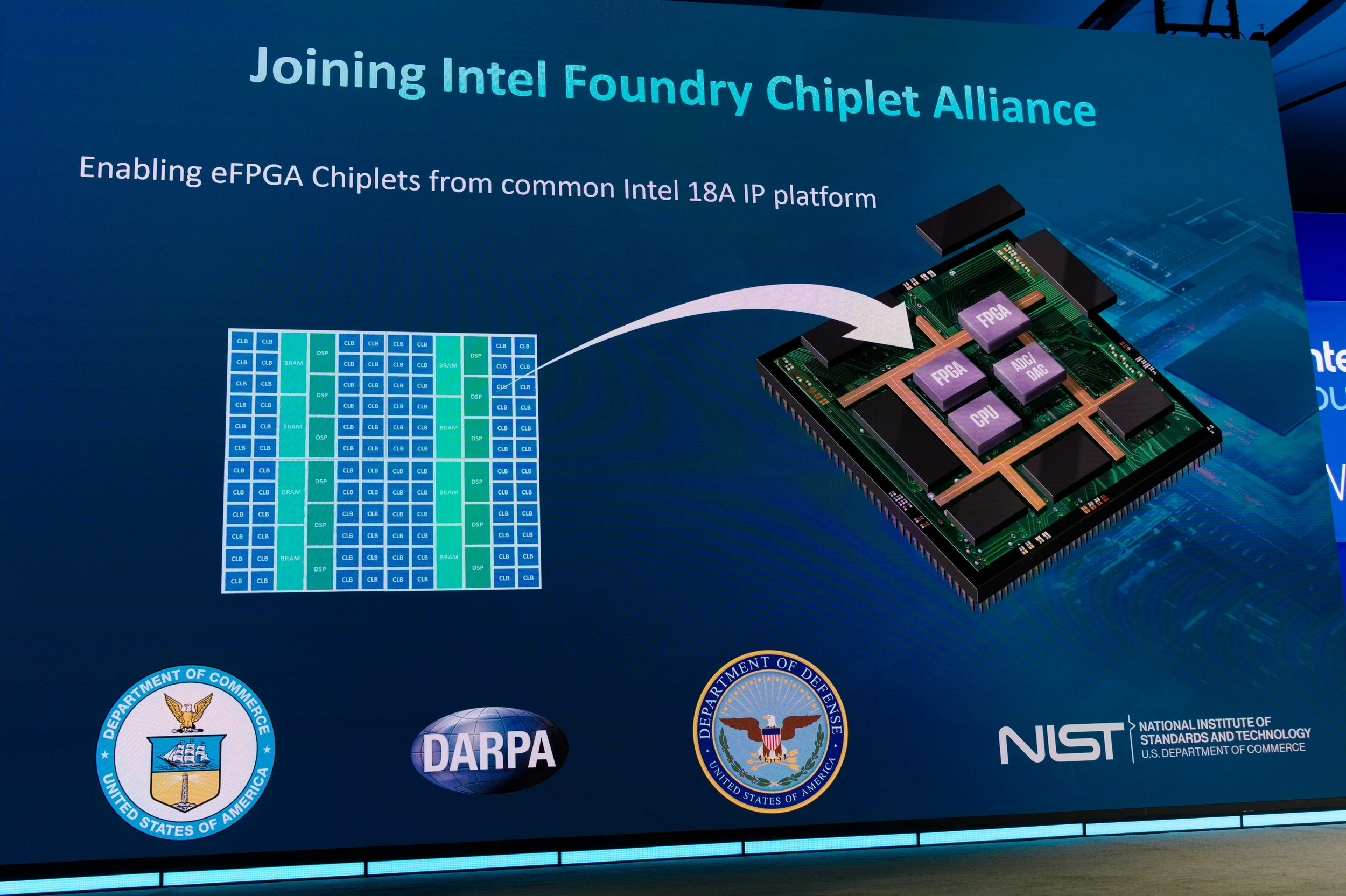

Commençons par la base : un FPGA, qu’est-ce que c’est ? Hé bien, à l’origine, il s’agit d’une puce servant à réaliser des opérations simples de traitement du signal sur des interfaces très haut débit via un traitement parallèle des informations, nommée Field Programmable Gate Array. Pour cela, une grille (le fameux Array) de blocs logiques (les Gates, ou CLB sur le schéma ci-dessus) est gravée sur du silicium et munie d’un interconnect programmable permettant de router des données d’un bloc à un autre. Rajoutez un peu de mémoire locale (BRAM), des petits accélérateurs locaux (DSP), et voilà le travail. Dans la pratique, un programmeur spécialisé passe quelques mois (ou plus !) à concevoir son design, qu’il livre à ses clients sous la forme d’un fichier de configuration nommé bitstream, qui peut être flashé sur la puce pour modifier sa configuration en moins d’une seconde. Pratique !

Désormais, les FPGA se sont légèrement dispersés dans leurs utilisations, avec des possibilités de substitutions aux circuit spécialisés ASIC (avec l’avantage du coût de développement et de production moindre, au détriment des performances), d’accélération de calcul de réseau de neurones (principalement en inférence sur du calcul entier) ou encore dans des cartes multi-usages où l’aspect reprogrammable s’avère terriblement utile.

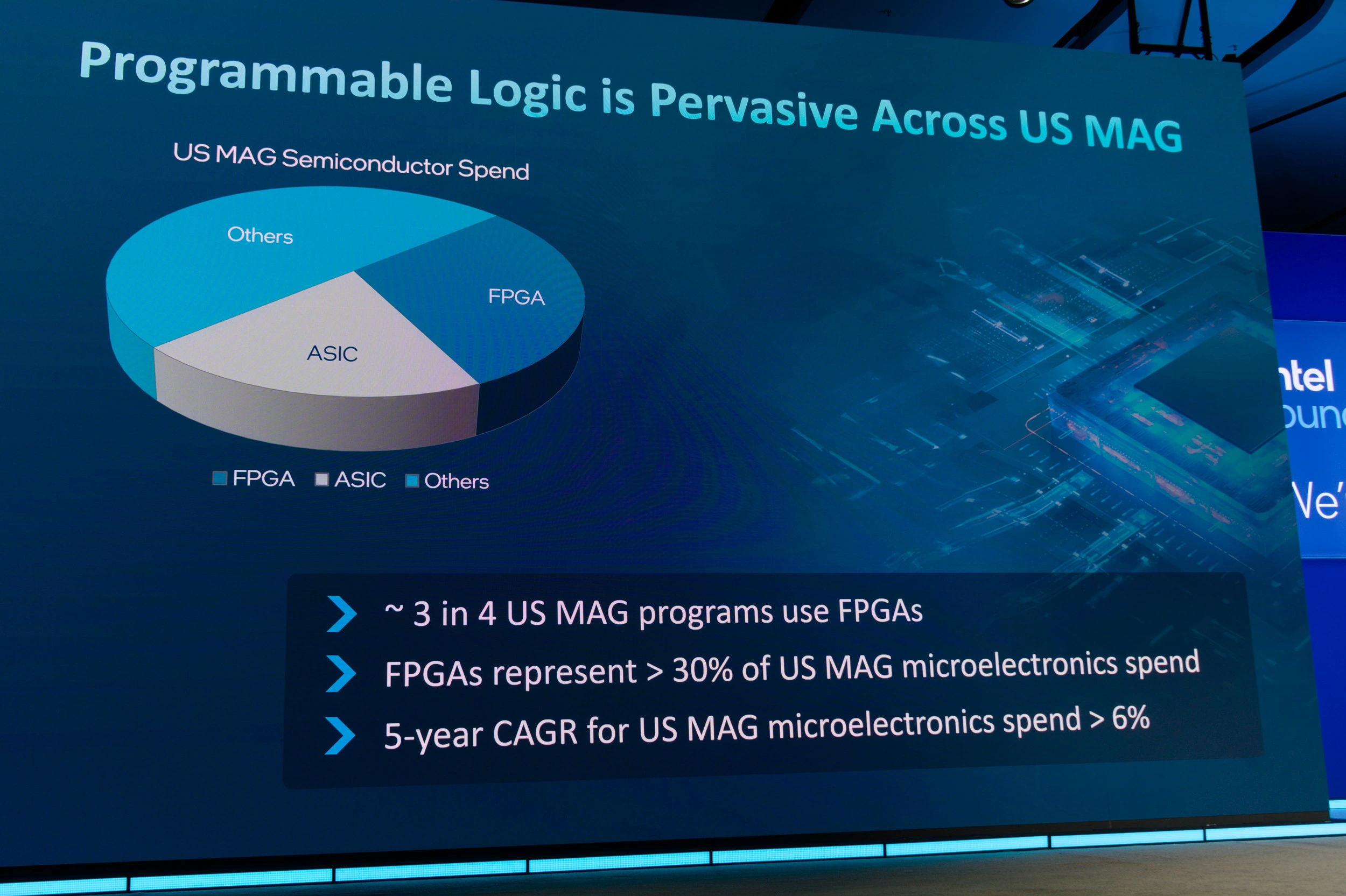

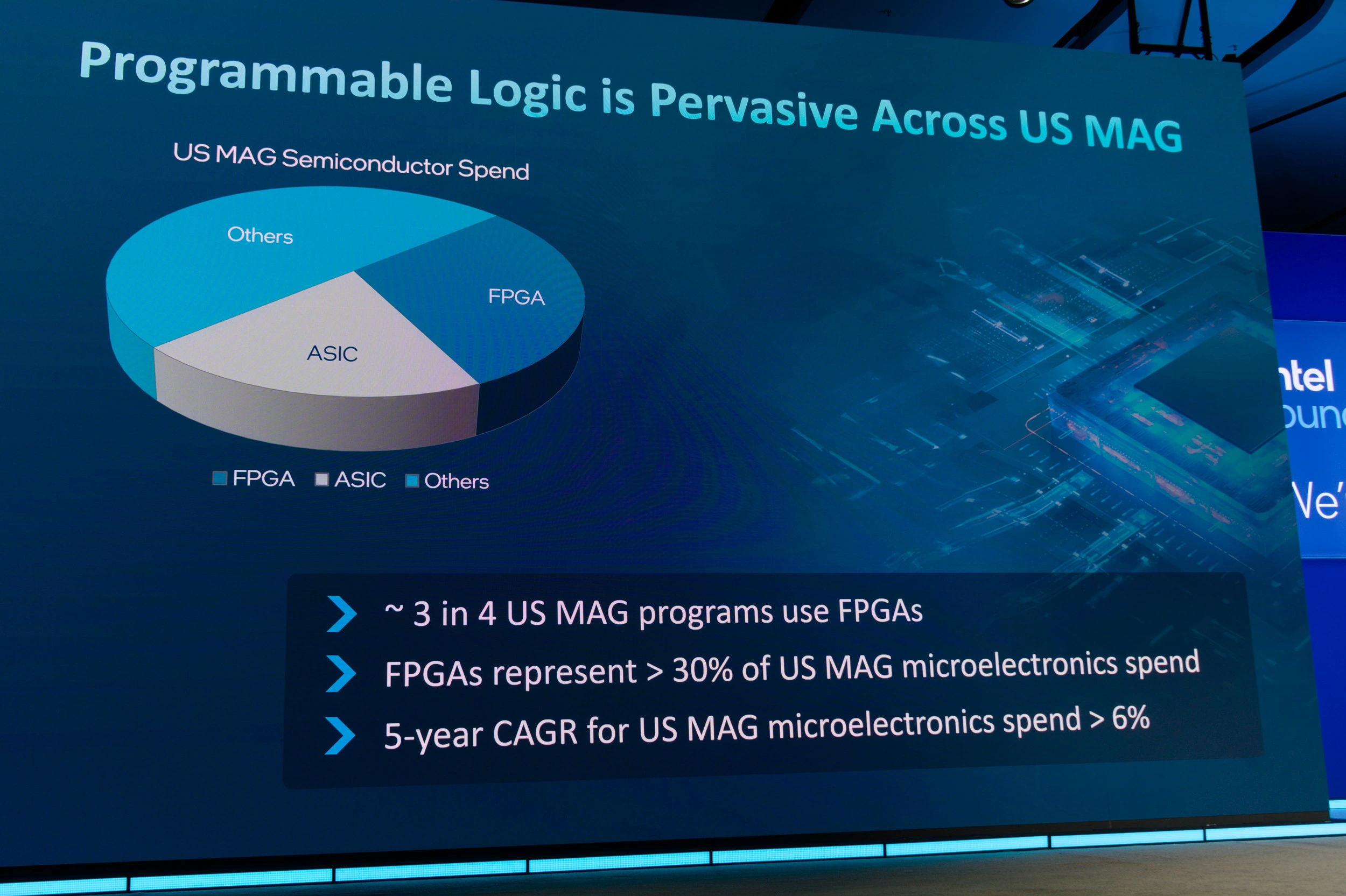

Avec plus de 25 % des dépenses en microélectronique du gouvernement américain, les FPGA dépassent de peu les ASICs !

Ces caractéristiques font des FPGA (ou eFPGA, pour embedded FPGA, c’est-à-dire la même chose, mais assemblé avec d’autres IP dans un SoC hétérogène) des candidats de choix pour l’industrie de défense/aérospatiale (MAG, pour Military, Aerospace and Government), dont les dépenses sont justement en hausse. En effet, la perspective d’un suivi long terme, de mises à jour aisément déployables et d’une certaine standardisation des composants à travers une ribambelle d’usage a de quoi attirer dans un domaine où le hardware comme le software est mis sous forte contrainte.

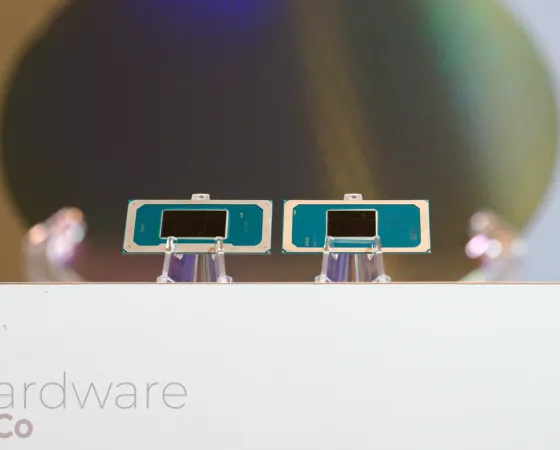

Tout cela est bien beau, mais quel est donc le rapport avec Intel ? Tout réside dans la finesse de gravure 18 A. En effet, cette dernière introduit deux éléments clefs : le GAA-FET, une nouvelle structure de transistor, et le Backside Power Delivery (nommé PowerVia par Intel), une méthode séparant l’alimentation de la puce des connexions entre transistors. Cette seconde technologie est extrêmement bénéficiaire aux FPGA : en effet, le goulot d’étranglement principal de ces puces se situe justement dans l’interconnect, car relier des blocs logiques entre eux de manière à pouvoir accéder arbitrairement à n’importe lequel est une contrainte coûteuse. Avant les PowerVia, les interconnections de signaux entre blocs devaient également être mêlée à l’alimentation électrique de ces derniers, prenant fatalement plus de place tout en contraignant l’architecture du fait des perturbations électromagnétiques induites par les fils apportant le courant. Avec les PowerVia, la partie alimentation se retrouve de l’autre côté du die, libérant ainsi les signaux d’information pure. Il en résulte un gain de 30 % réel en densité, ce qui permet de réaliser des chiplets sauce FPGA. Youpi !

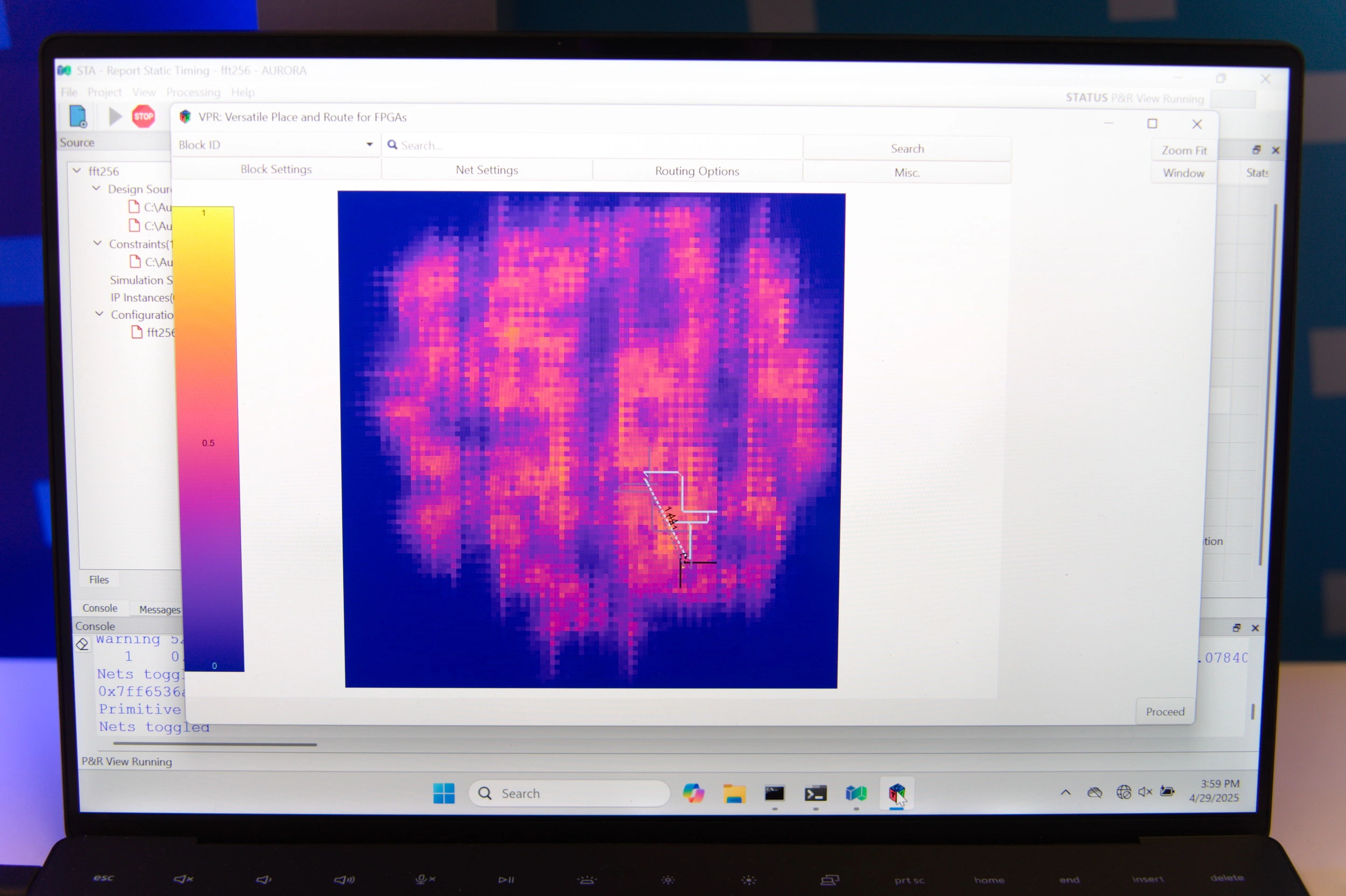

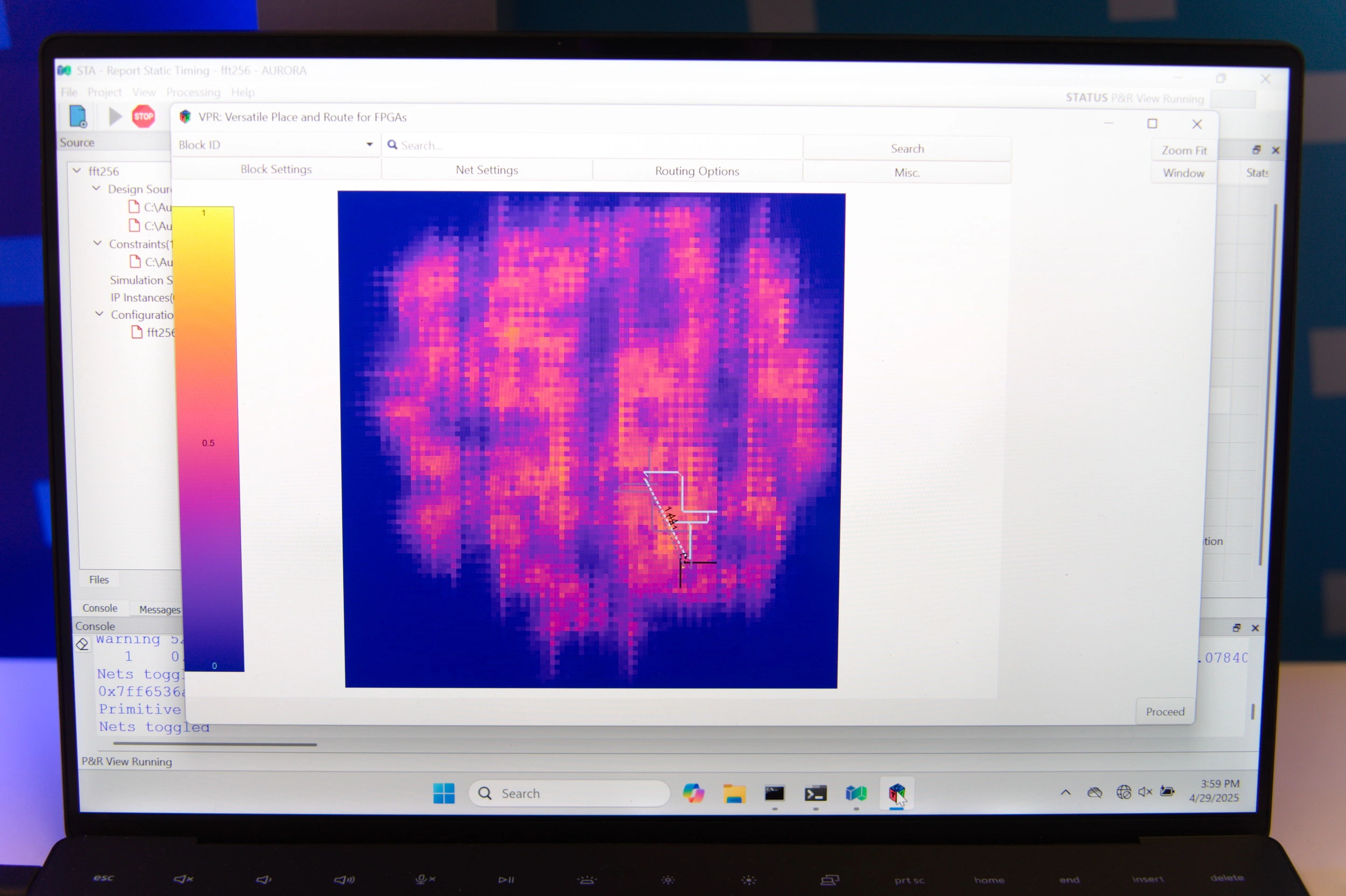

Et voilà une visualisation du résultat : un design, placé et routé sur le FPGA. Le jaune indique les zones plus ou moins occupées, et le chemin blanc un exemple d’interconnexion activée entre plusieurs cellules.

Nous ne sommes donc pas surpris de voir la maison-mère QuickLogic partenaire d’Intel dans le domaine de la défense et de l’aérospatial, qui plus est en suivant l’écosystème des chiplets. Il devient alors tout à fait envisageable de concevoir des tuiles FPGA intégrables directement dans les SoC, à la manière d’un GPU, d’un NPU ou des encodeurs médias qui sont désormais standards dans nos appareils. À ce propos, Apple avait justement intégré une carte FPGA de chez Xilinx dans un de ses Mac Pro (disparu depuis) pour accélérer le transcodage entre différents codecs. De quoi laisser imaginer une prolifération de cette technologie à l’avenir ? Possible, particulièrement si une demande d’efficacité énergétique à bas coût se fait sentir, encore faut-il avoir la possibilité de mettre à jour tout l’écosystème logiciel pour tirer parti du bousin. Il n’est alors pas étonnant que l’industrie grand public reste figée sur une collection d’accélérateurs indépendants désactivables, fonctionnant chacun leur tour de manière à maximiser la performance. Rendez-vous dans une poignée d’années pour faire le point sur l’évolution des besoins !

Espérons qu'Intel puisse utiliser ces technologies pour ses futurs CPU, histoire de ne pas laisser AMD en situation de quasi-monopole sur les CPU hautes performances...

Il serait cocasse (et dommageable pour l'utilisateur final) de voir la situation Core vs Bulldozer se reproduire, mais à front renversé.

La concurrence, cela n'a (presque, i.e. tant qu'elle reste loyale) que du bon, et pour l'instant, Intel est largué. Alors, même si je déteste leur métissage de coeurs P/E dans leurs CPU, je suis impatient de les voir revenir dans la course, ne serait-ce que pour aiguillonner AMD.