La micro-architecture Zen 5, sur le papier, cela donne envie. Comme nous vous le décrivions dans notre analyse, le design est pensé pour être « la fondation » de futurs évolutions — Zen 6 en tête. Ainsi, si certains choix peuvent sembler étranges (par exemple le manque d’équilibrage entre la bande passante L3 et le débit de calcul AVX-512), ces derniers se retrouvent justifiés en replaçant le cœur dans son contexte : une microarchitecture capable de s’étendre des processeurs basse consommation pour PC portables aux gros bousins sur serveur multipliant les tâches lourdes comme le machine learning. Rajoutez que l’ensemble n’est pas construit ex nihilo, puisque Zen 5 reprend les grande lignes de Zen 4 et permet ainsi de moderniser certains composants interne pour les architectures futures : vous l’avez compris au titre, tel est le cas de la prédiction de branchement.

Déjà, késako ? La prédiction de branchement permet au processeur de deviner en avance les instructions suivantes à exécuter à la suite à un saut (nommé, justement, branchement). Ces sauts sont très courants dans les programmes (environ 20 % des instructions !), et la plupart d’entre eux sont conditionnels, comprenez qu’il faut attendre le résultat d’un calcul pour savoir où brancher. Une attente qui limite les performances, c’est pour cela que le CPU va utiliser des mécanismes de spéculation pour commencer en avance son exécution. Dans le cas où la prédiction était correcte, banco, sinon, une pénalité d’une dizaine de cycles a lieu le temps de nettoyer les calculs faux effectués en avance.

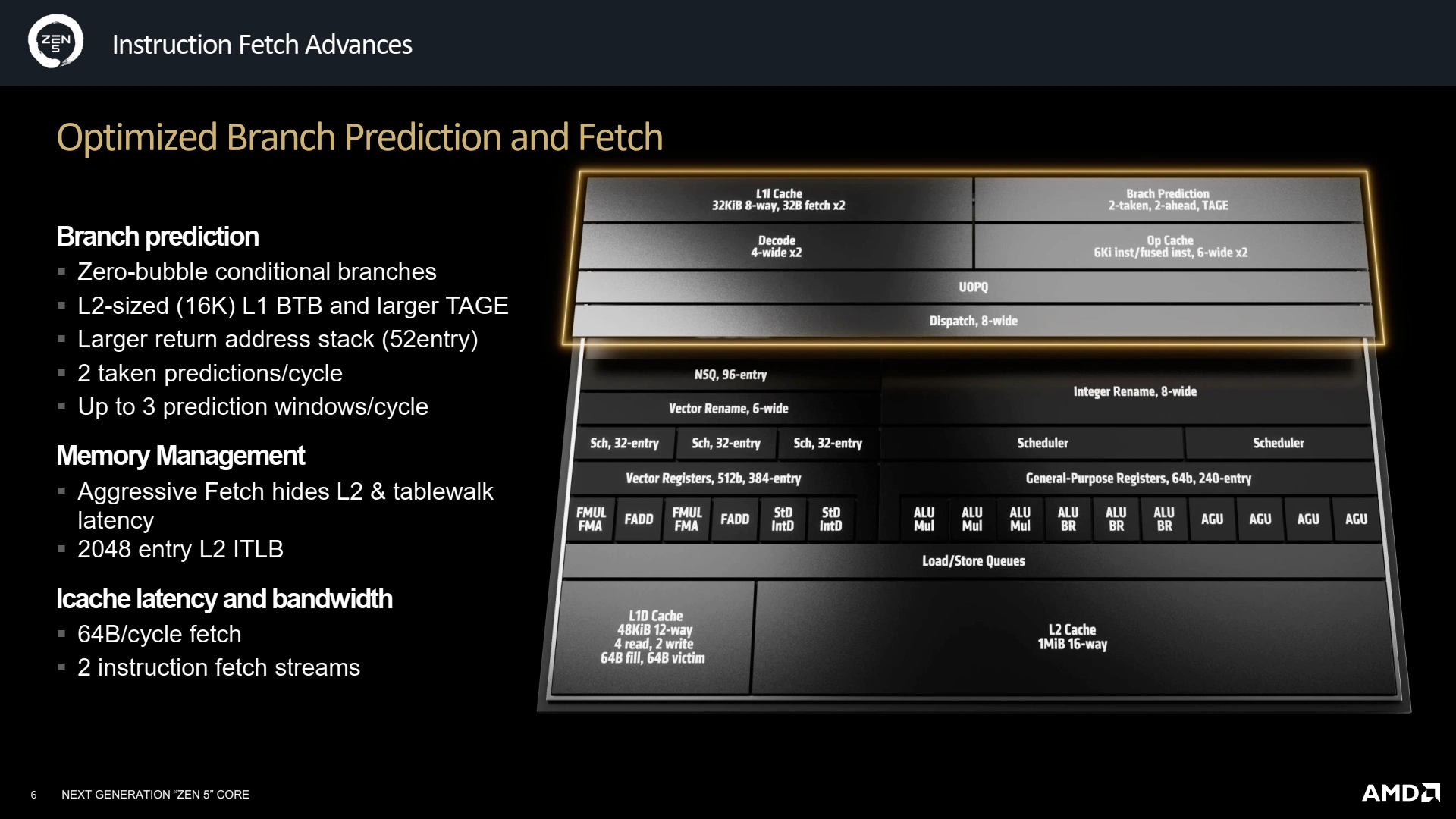

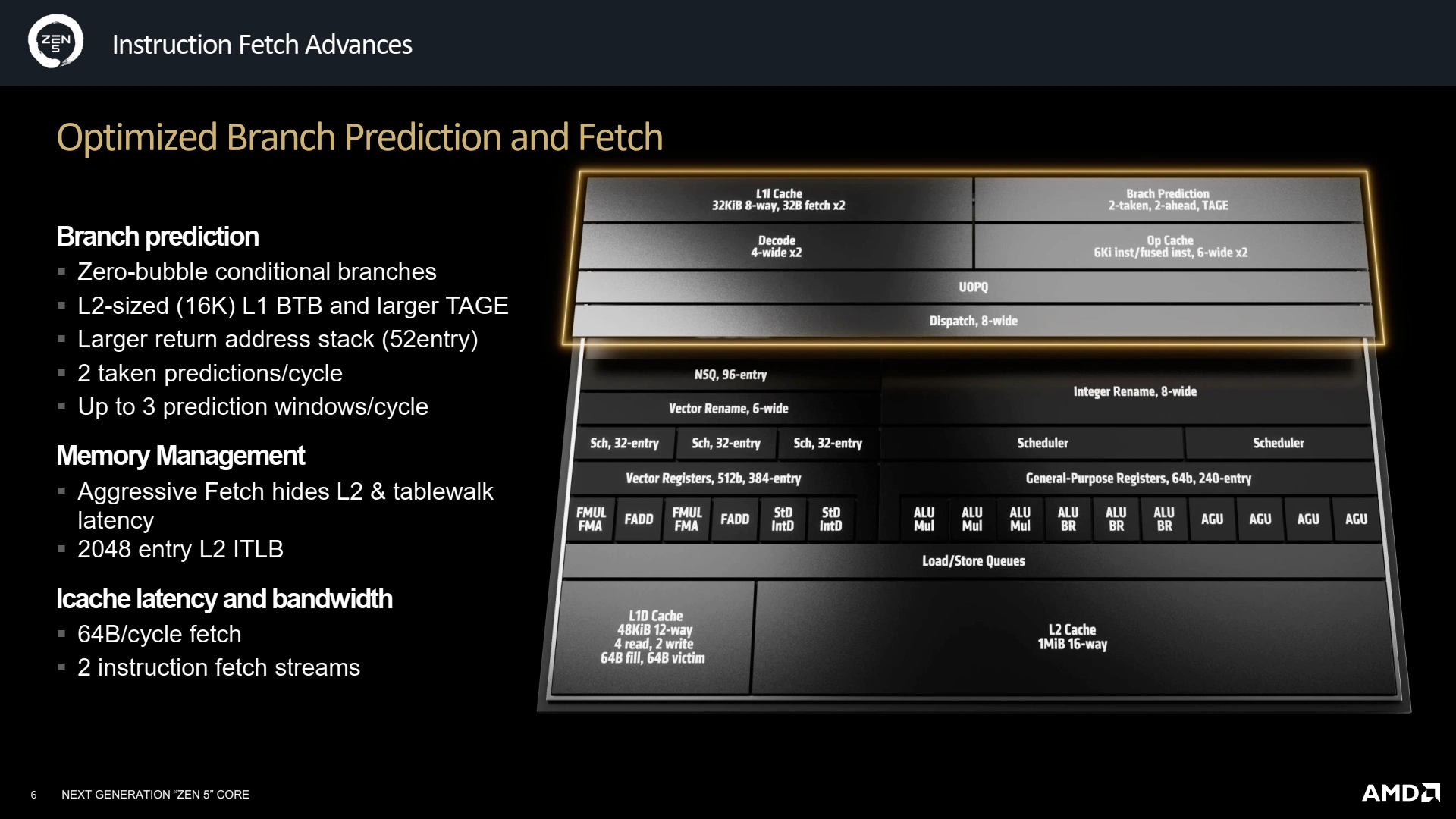

Les avancées de Zen 5, niveau prédiction de branchement.

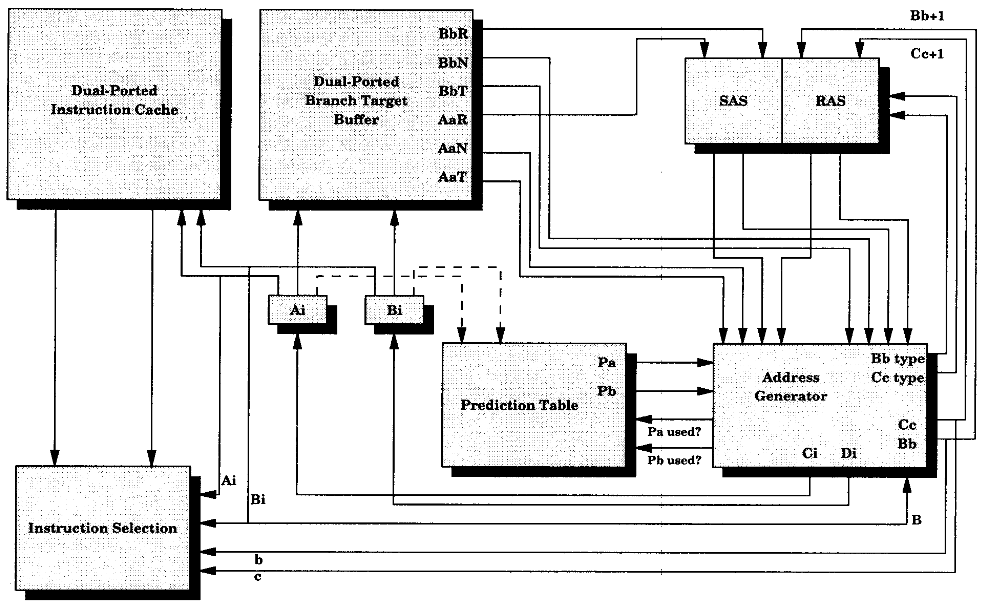

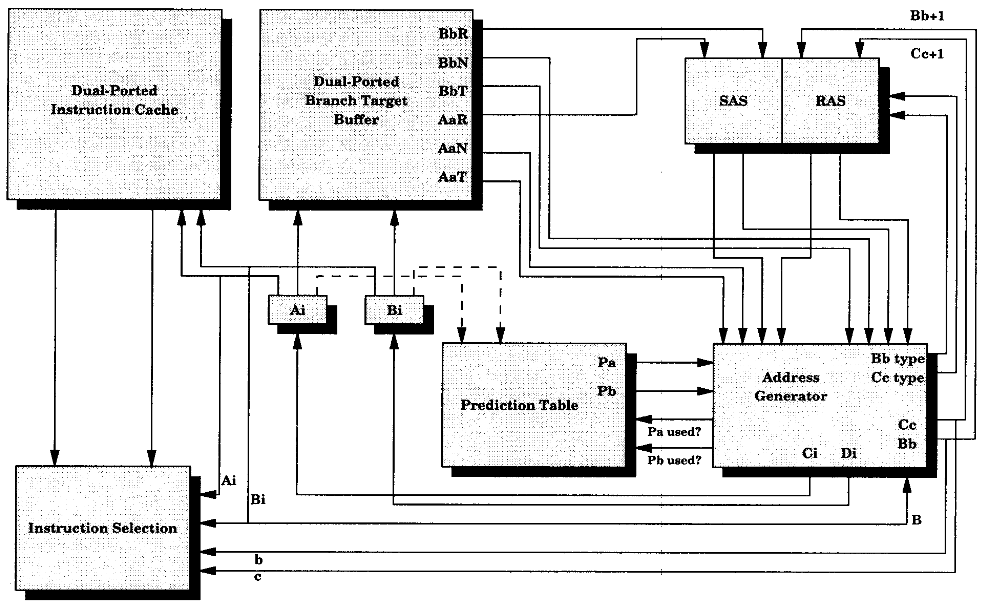

Dans le domaine de la prédiction de branchement, un nom émerge, et un français : André Seznec. Le monsieur a un cursus académique remarquable, a même été recruté par Intel avant de revenir dans le public. Il est à l’origine de l’état de l’art encore à l’œuvre dans les processeurs, le prédicteur TAGE ; mais ce n’est pas ce qui nous intéresse le plus ici. Non, il est surtout question d’un papier de 1996 (voilà qui ne nous rajeunit pas…) dans lequel notre chercheur (épaulé par d’autres membres : Stéphan Jourdan, Pascal Sainrat et Pierre Michaud ; la recherche en architecture s’effectuant rarement en solo) propose une méthode pour prédire non pas un, mais deux branchements (de bloc non-consécutif, les prediction windows) à la fois.

Dans les prémisses de la prédiction de branchement, doubler le débit du composé était une manière considérée pour augmenter toujours plus les performances des CPU, qui fut finalement abandonnée au profit d’une augmentation de la précision de la prédiction — notamment avec le fameux TAGE. Une des raisons était le coût prohibitif de ce doublement : la solution suggérée par Seznec demandant en effet de doubler l’étage de décodage des instructions ainsi que le Branch Target Buffer, une chose fortement coûteuse en 1996. Tiens tiens, sur le Zen 5 bien de 2024, nous trouvons justement un double décodeur et un L1 BTB qui a explosé à 16K entrés, surpassant le L2 (8K entrée) : AMD a très certainement été piocher du côté de ces idées-là. Cocorico !

Dans la pratique, cela signifie que Zen 5 devrait faire un usage toujours plus efficace de ses unités et être toujours plus rapide - particulièrement en utilisant le SMT -, et que - taille des buffers mis à part - le front-end ne devrait que peut évoluer sur la génération suivante... mais cela ne demeure que pure spéculation (ah ah) ! (Source : Chips and Cheese)

Interessant !