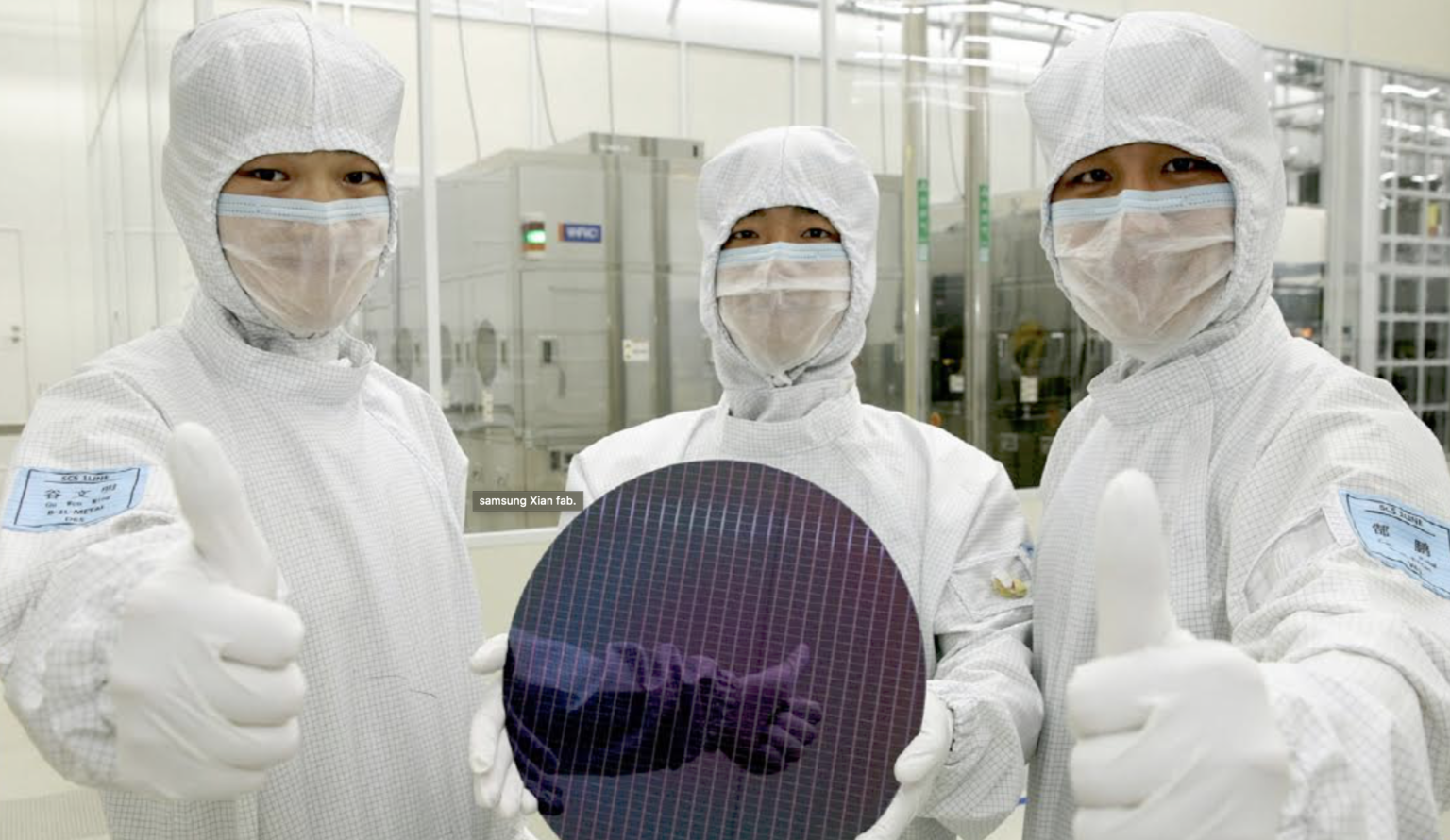

Tous les grands fabricants de mémoire ont aujourd’hui abordé la production de mémoire vive en se servant de machines lithographiques EUV plutôt que DUV pour leurs procédés de pointe. Certes, chacun y est un peu allé à son rythme. SK hynix et Samsung expérimentent ouvertement la DRAM EUV depuis 2020/2021, tandis que Micron avait longtemps repoussé la transition et rentabilisé l’usage de son outillage DUV pour la DRAM jusqu’au bout, non sans réussite d’ailleurs. Ce n’est que cette année en juin que l’américain a enfin rejoint la fête des ultraviolets extrêmes en annonçant la production en volume de sa première DRAM EUV pour 2025 basée sur le procédé 1y (1 gamma, toujours de classe 10 nm). Samsung et SK hynix vont commencer la production en volume de leur DRAM 1c avec une quantité a priori toujours inconnue (mais potentiellement comprise entre 2 et 5) de couches EUV cette année. La lithographie EUV pour la DRAM permet en principe d’augmenter la productivité d’un wafer, grâce à des puces plus denses et plus petites, ce qui en retour améliore la compétitivité des couts de l’entreprise.

En pratique, la production de DRAM avec une lithographie EUV reste un exercice toujours bien couteux à ce jour, car procédés et production sont beaucoup plus complexes, sans oublier que l’outillage EUV est particulièrement onéreux aussi. Bref, elle exige un investissement conséquent et les couts de la production seraient encore amenés à augmenter avec la 6ᵉ génération de DRAM de classe 10 nm. Heureusement, il y aurait une solution : la DRAM 3D ! Cette dernière reprendrait le principe de la NAND 3D en empilant les transistors verticalement les uns sur les autres sur plusieurs niveaux. Avec cette méthode, il sera possible de loger plus de bits sur une même surface, ou d’obtenir des puces jusqu’à 30 % plus petites à capacité égale par rapport à une DRAM 2D conventionnelle. Il est question aussi d’utiliser la technique du "wafer bonding" pour connecter deux wafers ensemble sur toute leur surface. Cette évolution assez radicale de la conception de la mémoire vive, apparemment de plus en plus nécessaire pour des raisons de couts et de limites techniques de la DRAM actuelle, exigerait également de nouveaux matériaux.

La bonne nouvelle, c’est que selon un chercheur de chez SK hynix, la DRAM 3D serait la clé pour réduire de moitié les couts de production à partir d’un procédé EUV ! Ce serait évidemment non négligeable. En tout cas, ce n’est certainement pas par hasard que le passage à la DRAM 3D est déjà sur la table chez tous les fabricants concernés. Samsung vise officiellement 2030 pour le lancement commercial d’une puce DRAM 3D avec la technologie de Vertical Channel Transistor (VTC) et 16 couches selon une structure 4F2. Chez SK hynix, il plutôt question de Vertical Gate DRAM, toujours avec un layout 4F2, mais d’aucune date encore pour l’instant. Enfin, officieusement, Micron planifierait aussi une première DRAM 3D, toutefois avec 8 couches seulement pour commencer. (Source : The Elec, via Computerbase)

C'est sur qu'avec l'I.A., les besoins en RAM vont exploser

Un modele tel que celui-ci :

https://huggingface.co/imi2/airoboros-180b-2.2.1-gguf/tree/main

nécessite 192 Go de RAM pour fonctionner a l'aise, 128 Go au minimum

Il faudrait pourtant calmer cette inflation parce qu'une partie du prix est lié à l'inflation, à la crainte de pénurie or quand les States et la Chine s'opposent, que le premier impose à ses alliés de ne pas vendre les technologie à Pékin et que la Chine limite fortement l'exportation de terre rares, ça fait exploser les prix.