C'est à San José, au cœur de la Silicon Valley, qu'Intel a donné rendez-vous pour ses innovations days, cuvée 2023. Le géant des semi-conducteurs doit faire face depuis quelques années à des vents contraires importants et une concurrence féroce. Après une perte de leadership au niveau des process de fabrication au profit du Taïwanais TSMC, il a vu son éternel rival AMD lui tailler des croupières dans le domaine des CPU, tant grand public que professionnel avec une architecture performante et une approche en chiplets clairement pertinente. Enfin, NVIDIA a préempté le domaine de l'intelligence artificielle avec ses accélérateurs se vendant comme des petits pains.

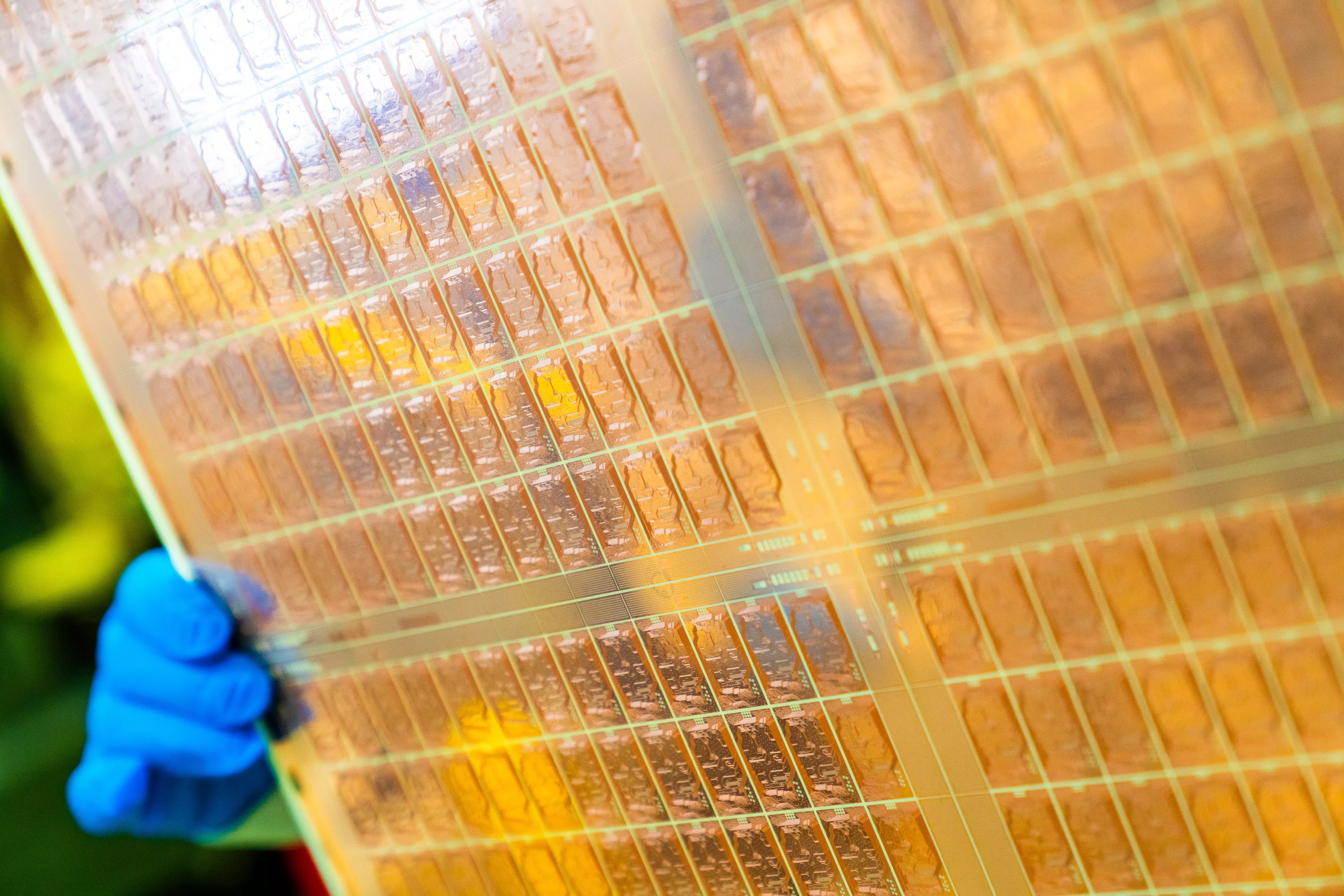

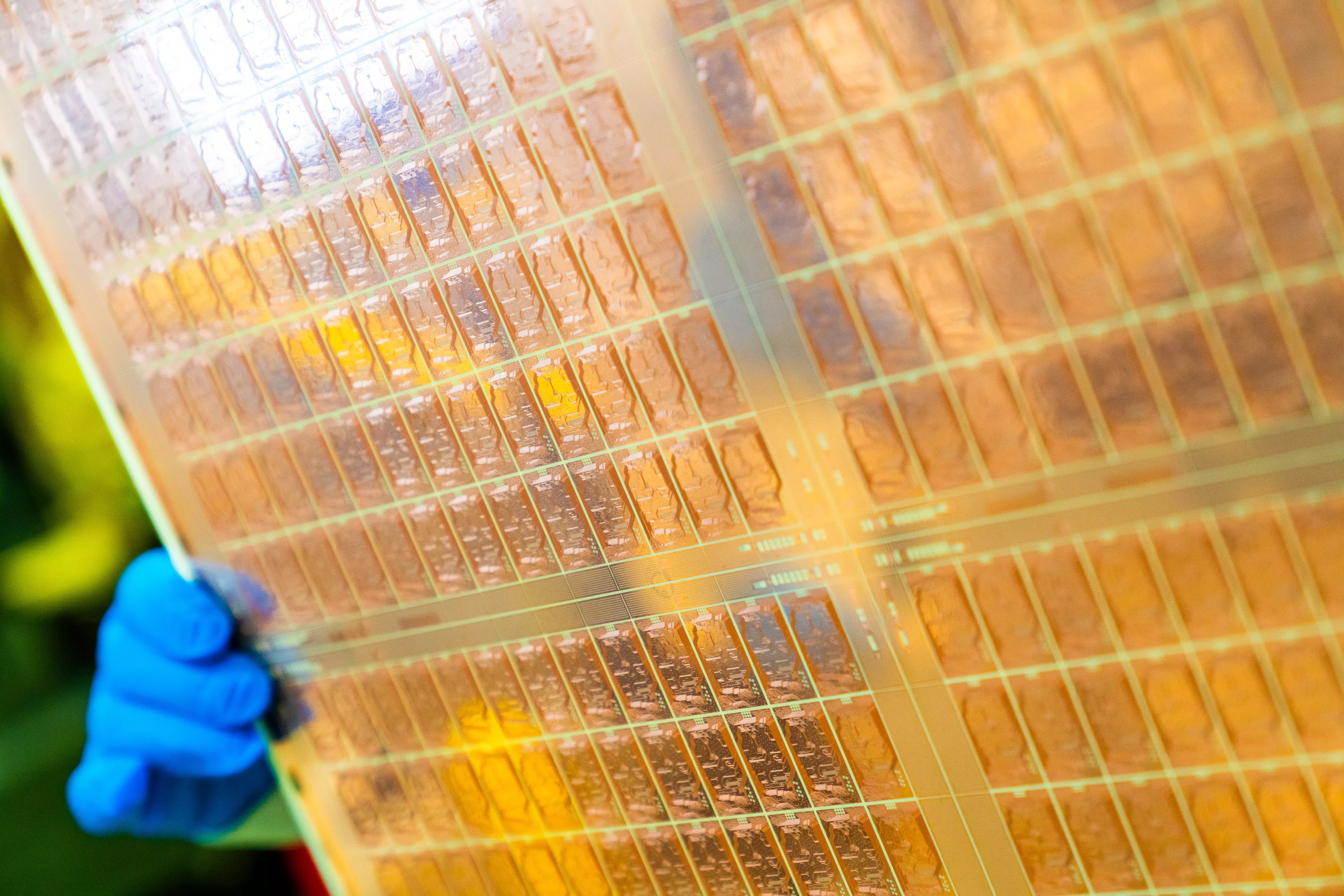

Bien décidée à ne pas se comporter en victime expiatoire, la société basée à Santa Clara affine sa stratégie et met les bouchées doubles pour rattraper son retard dans tous les domaines. Ainsi, les bleus confirment qu'ils sont toujours en bonne voie pour atteindre leur objectif de 5 nœuds de gravure en 4 ans. L'Intel 7 (ex 10 nm) est déjà en production de masse et sera complété sous peu par l'Intel 4 d'ores et déjà prêt pour les puces Meteor Lake. L'Intel 3 est attendu pour la fin d'année (Xeon 5ème Gen) conformément au planning, enfin les premiers Wafers Intel 20A sont sortis d'usine pour les premiers tests des puces Arrow Lake, destinées au marché computing en 2024. À noter que ce nœud de gravure est également le premier à introduire les technologies PowerVia (découplage des interconnexions d'alimentation) et RibbonFET successeur du FinFET et capable de délivrer la même quantité de courant avec une empreinte physique moindre).

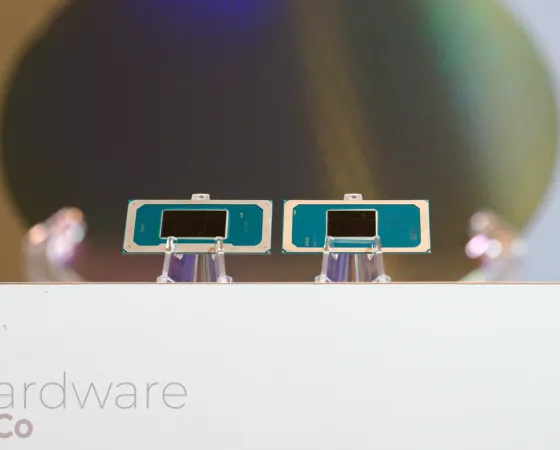

Tout ceci porte à 4 le nombre de nœuds de gravure, le cinquième nommé Intel 18A et reprenant les technologies sus-nommées, est attendu pour le second semestre 2024. Pour parachever son retour à la pointe de la technologie des procédés de fabrication, Intel indique vouloir adopter des nouveaux matériaux et substrats à l'avenir comme des packagings à base de verre (image ci-dessus) , qui devraient voir le jour dans quelques années et permettre de densifier encore davantage le nombre de transistors au sein d'une puce multidie. À cet égard, Intel annonce avoir développé une technologie nommée UCIe (Universal Chiplet Interconnect Express), permettant l'interconnexion de chiplets en provenance de concepteurs et fondeurs différents. Plus de 120 sociétés auraient déjà manifesté leur intérêt pour la chose (dont AMD, Samsung, Nvidia, Qualcomm) et un essai a été mené avec succès en accouplant une puce gravée en Intel 3 avec un chiplet conçu par Synopsys et gravé via le N3E de TSMC.

Au-delà de tous ces aspects technologiques, Intel pousse également à un écosystème logiciel bonifié par la disponibilité d'un Cloud dédié à l'IA. Via ce dernier les différents développeurs vont pouvoir accéder à des ressources matérielles et logicielles facilitant la tâche des développeurs en leur permettant de développer et expérimenter leurs application d'IA. Tout cela se fait au travers de oneAPI, standard ouvert multi-constructeurs afin de tenter d'enrayer le succès de CUDA. Pour faire tourner tout cela, Intel commercialisera le 14 décembre de nouveaux Xeon (5ème génération) ainsi que des Core Ultra que nous détaillerons dans de futurs billets.