Le moins que l’on puisse dire, c’est que le lancement des nouveaux processeurs Ryzen 9000 ne se fait pas sans douleur du côté d’AMD. Lancement retardé, performances en-deçà des espérances, ventes en retrait, tout ne s’est pas passé comme prévu et il est maintenant temps pour AMD de tenter de corriger le tir comme il peut et d’assurer une sorte de « service après vente ». Cela a commencé par de la communication pour tenter d’expliquer les résultats décevants obtenus par certains médias, puis en travaillant avec Microsoft pour améliorer les performances sous Windows 11. On enchaîne à présent sur un autre problème : des soucis de latences anormalement élevées entre les cœurs Zen 5, surtout si ceux-ci sont situés dans des CCD différents dans le cas des Ryzen 9 9900X et Ryzen 9 9950X.

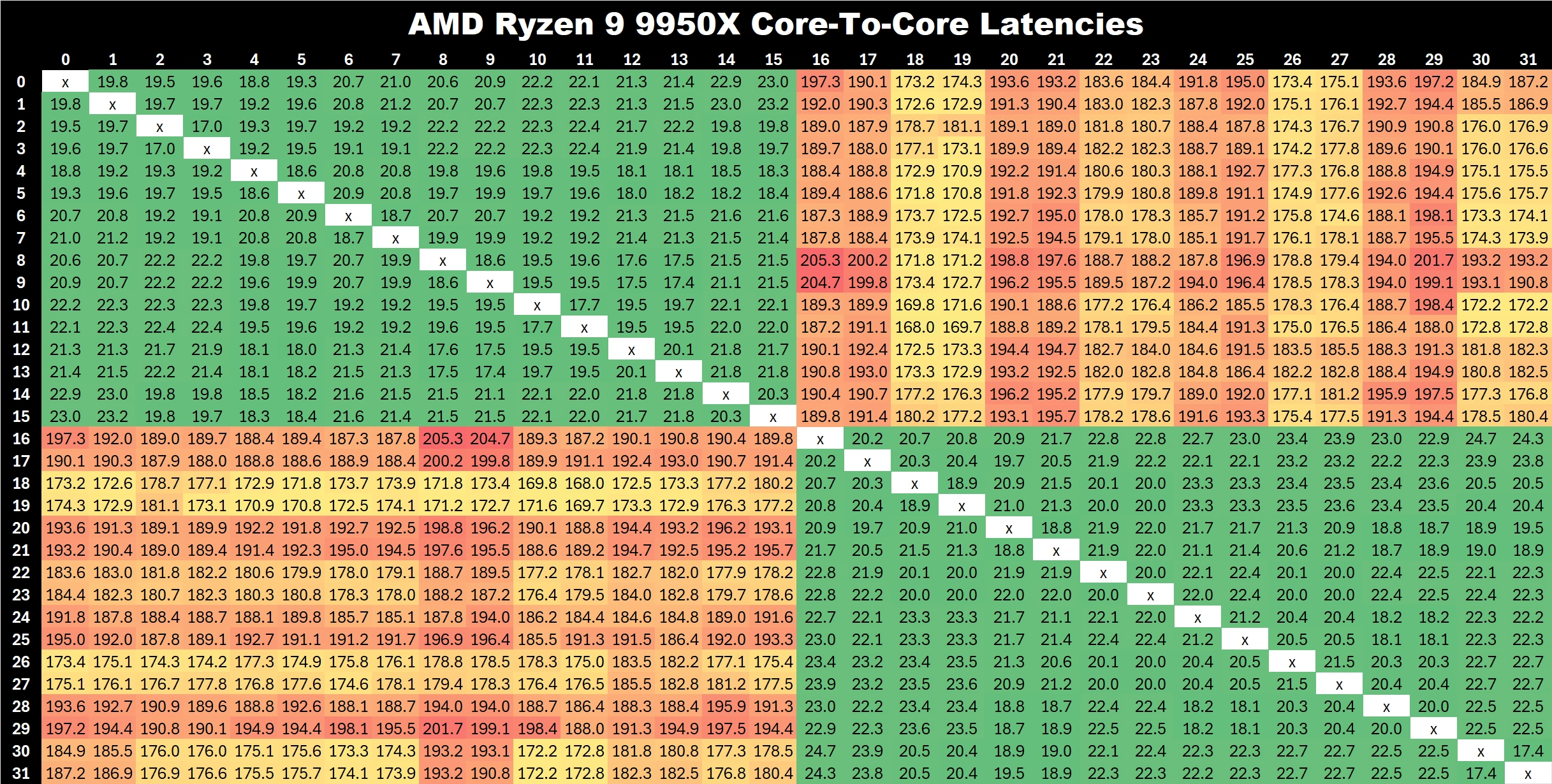

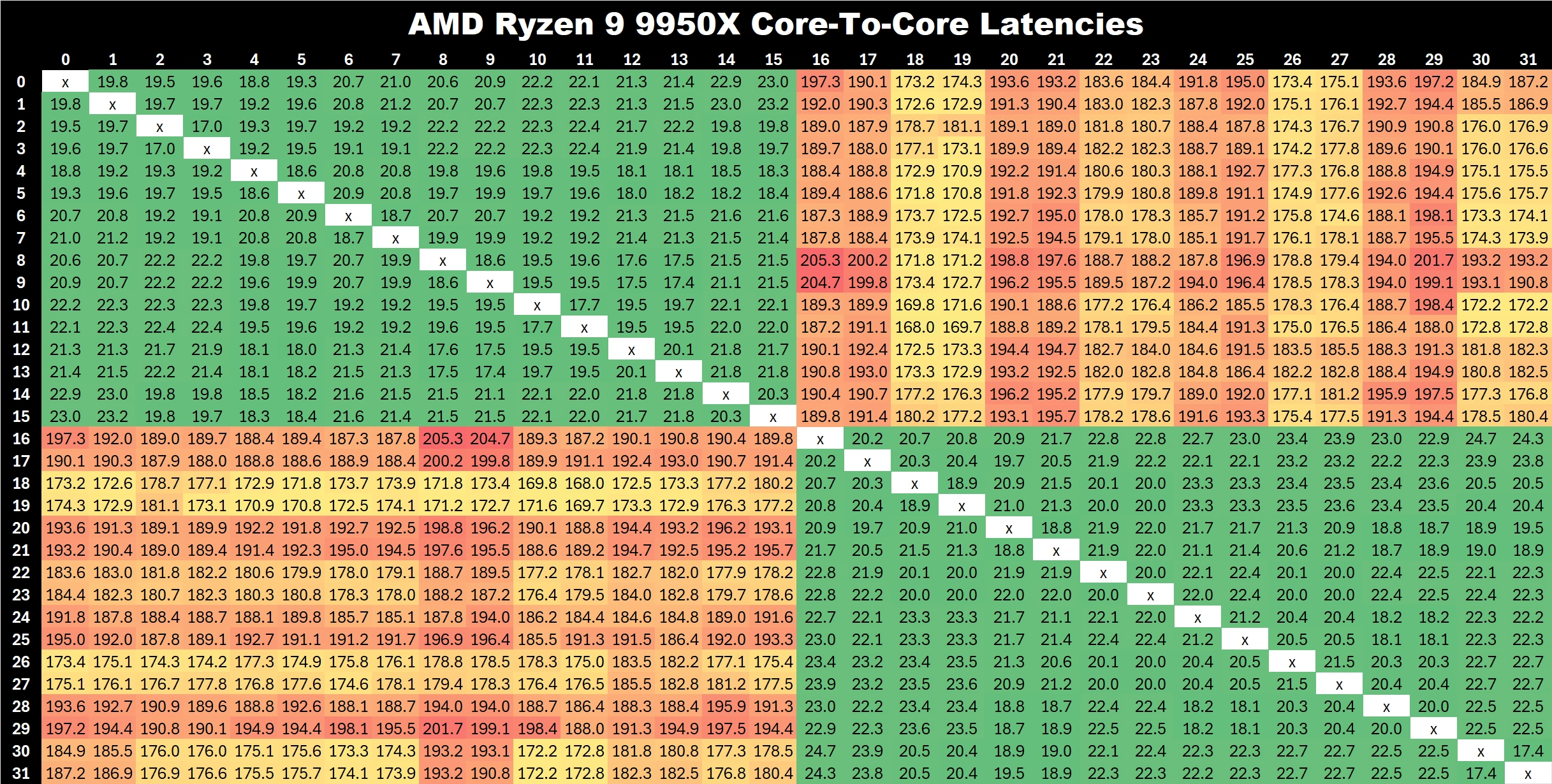

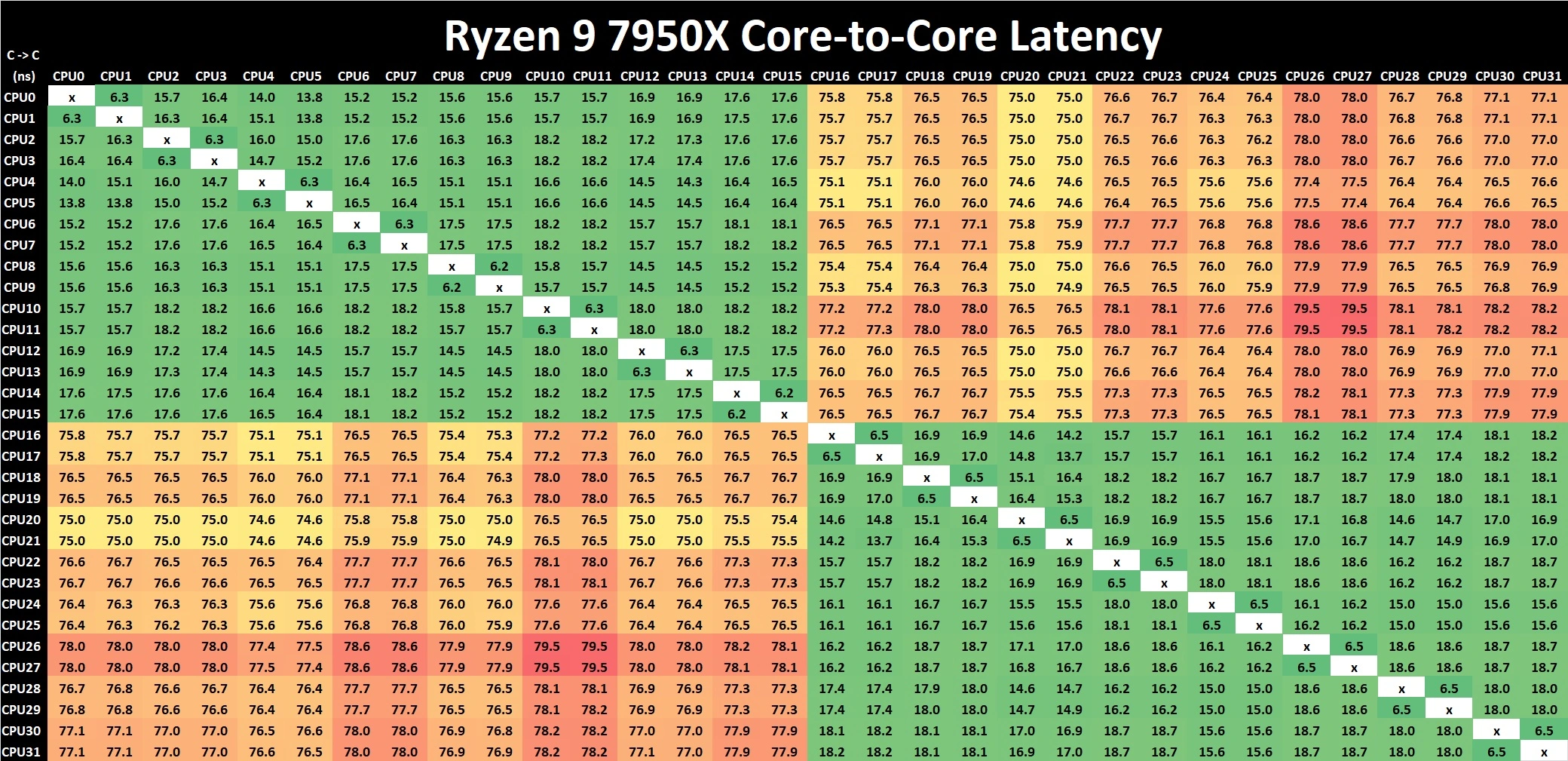

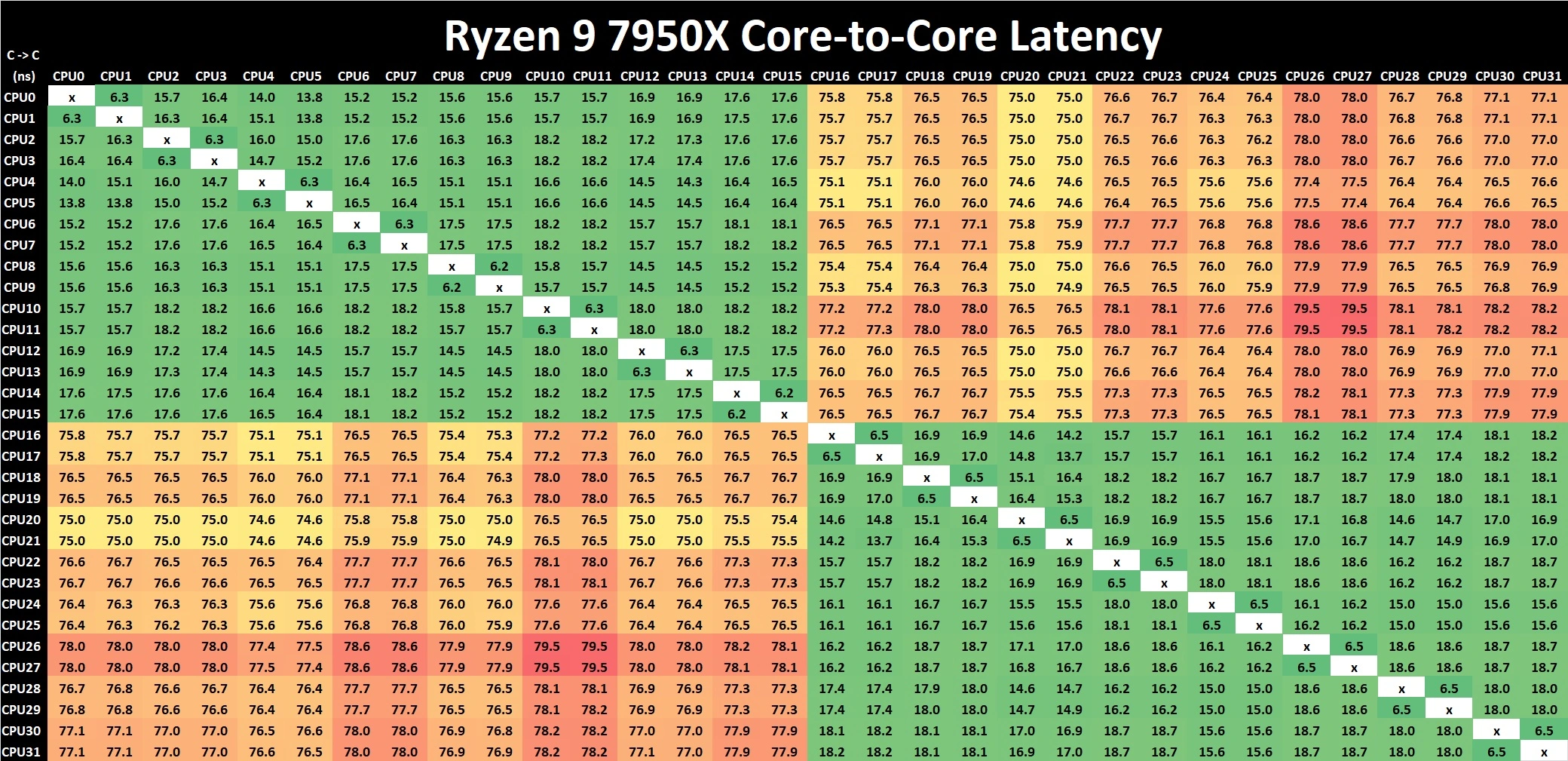

Les chiffres obtenus par nos confrères d’Anandtech sont édifiants. Les latences augmentent légèrement pour les échanges entre cœurs situés sur un même CCD, avec une moyenne de l’ordre de 20 ns pour le 9950 X Zen 5 contre 17 ns pour le 7950 X Zen 4. Cela pourrait s’arrêter là et n’être pas trop inquiétant, mais quand on passe aux échanges entre des cœurs qui ne sont pas situés sur le même CCD, on arrive dans le cas du 9950X à des latences moyennes de l’ordre de 200 ns contre 77 ns au 7950 X. On n’est pas loin de latences multipliées par trois, ce qui est tout de même problématique et anormal. Si vous vous demandez comment se débrouillait la génération encore avant, le Ryzen 9 5950X Zen 3 de la plateforme AM4 obtient des latences entre cœurs en tout point similaires à celles obtenues par le 7950 X Zen 4… Outre cela, un autre détail saute aux yeux : la latence entre cœurs jumeaux (c’est-à-dire des cœurs logiques partageant le même cœur physique grâce au SMT) est aussi élevée qu’entre cœurs du même CCD sur Zen 5, là où Zen 4 se permettait 6,5 ns seulement (soit quasi 3 fois moins). Cela semble pointer vers un passage forcé par le cache L3, même entre SMThread : peut-être un autre bug, à moins qu’il ne s’agisse d’une mesure d’isolation des thread afin de se prémunir des attaques type spectre.

La bonne nouvelle, ce serait qu’AMD aurait conscience (encore heureux nous direz-vous) de l’existence de ces latences trop élevées, et serait en train de travailler dessus dans l’optique de les corriger à l’avenir. L’information nous vient de Geekerwan lors d’une de ses vidéos sur Bilibili, relayée par @9950pro sur X .com :

Geekerwan : AMD will fix Zen 5 C2C latency issue. https://t.co/v1ru4UXQmS pic.twitter.com/3u0pAmBuwV

—HXL (@9550pro) August 27, 2024

On imagine que cela passera par un nouveau BIOS et nous vous tiendrons évidemment au courant lorsque d’autres informations, on l’espère officielles, seront publiées à ce sujet.

Y'aurait-il le même tableau "contrôle" sur les anciennes générations Zen ?

Chui intéressé par les latences sur les Zen2 et Zen3 ? C'est informatif pour le multithread.

La par exemple : https://www.anandtech.com/show/16214/amd-zen-3-ryzen-deep-dive-review-5950x-5900x-5800x-and-5700x-tested/5

Une rapide recherche google avec "zen x core to core latency" vas t'aider.

Bon, les bogues dans les nouveaux CPU, c'est parfaitement "normal", et en fait quasi systématique pour les x86 (dont la complexité est devenu totalement démente par la faute d'une ISA complètement dépassée et pas conçue à la base pour ce qu'on lui fait faire, qui en plus doit se traîner des modes de compatibilité surannés en pagaille: modes 32 bits, 16 bits, mémoire segmentée et autres joyeusetés du genre).

Mais là, j'ai tout de même la franche impression que le contrôle qualité chez AMD est totalement défaillant !... S'ils ne s'aperçoivent que maintenant que les latences sont anormalement élevées, alors soit l'équipe QA n'a pas fait son travail, soit on ne lui a pas laissé suffisamment de temps pour le faire. AMD aurait dû attendre un petit trimestre de plus pour lancer ses Zen 5 (de toutes façons, Zen 4 est déjà excellent face à Raptor Lake, et ce dernier rencontre tellement de soucis qu'il n'est plus vraiment un concurrent sérieux), le temps de peaufiner l'AGESA, de pied-au-cul-ter Micro$oft pour qu'il mette l'ordonnanceur de Windaube à jour, et de s'assurer que tous les petits soucis de prime jeunesse sont corrigés !

Bref, j'ai bien fait d'attendre pour acheter un Zen 5: les choses devraient se décanter (et les prix baisser) d'ici la fin de l'année...

Le billet ne dit pas qu'AMD a découvert le "problème" qu'une fois les CPU en vente. Je me soucis plus du control qualité d'intel...

Et les performances déjà bonnes des 9000 ne feront que s'améliorer, on est pas sur des patch intels qui font baisser la perf...

Bah déjà la latence entre CCD le fait d avoir conserver l ancien i/o die de la "plateforme" zen4

Ça doit pas aider tu multiplié les voies dans un CCD zen5, mais tu laisse le mm "poste de péage à barrière" au bout de l autoroute, et derrière ça reste une départemental

Ça prouve d autant plus que les core zen5 vise avant tout le marché serveur

Et qu ils ont fait des économie de chandelle si la plateforme bureau à coller ça sur un châssis de zen4

Coller un moteur 500chevaux sur une golf ça en fait pas une lambo

Le proco est hyper efficace et fonctionne mieux que la concurrence. Ils doivent avoir des centaines d'ingénieurs / docteurs qui bossent donc s'ils ont fait ce choix, il doit y avoir une bonne raison, surement le cout / compatibilité !