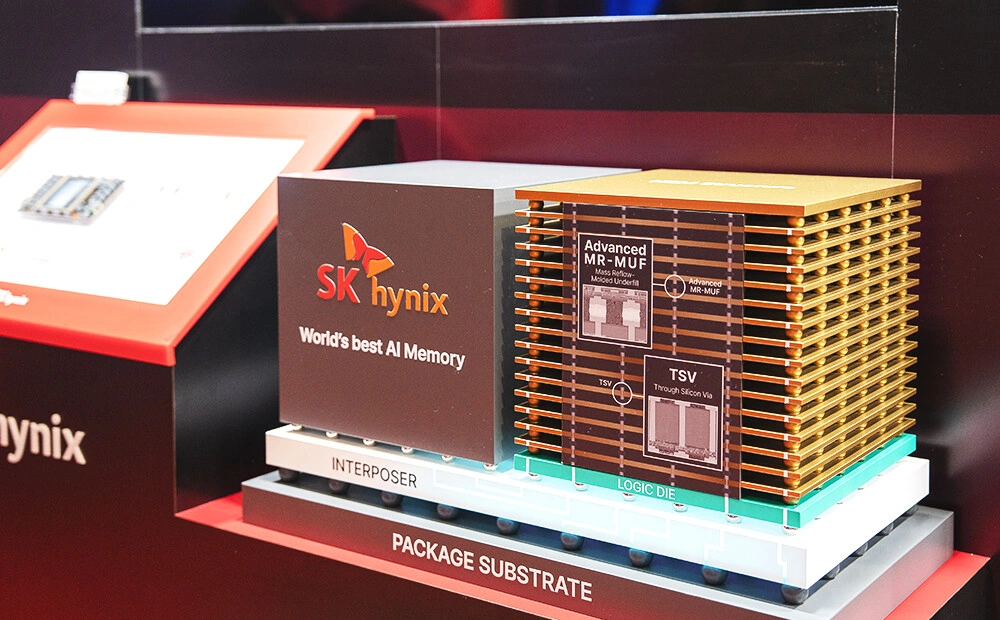

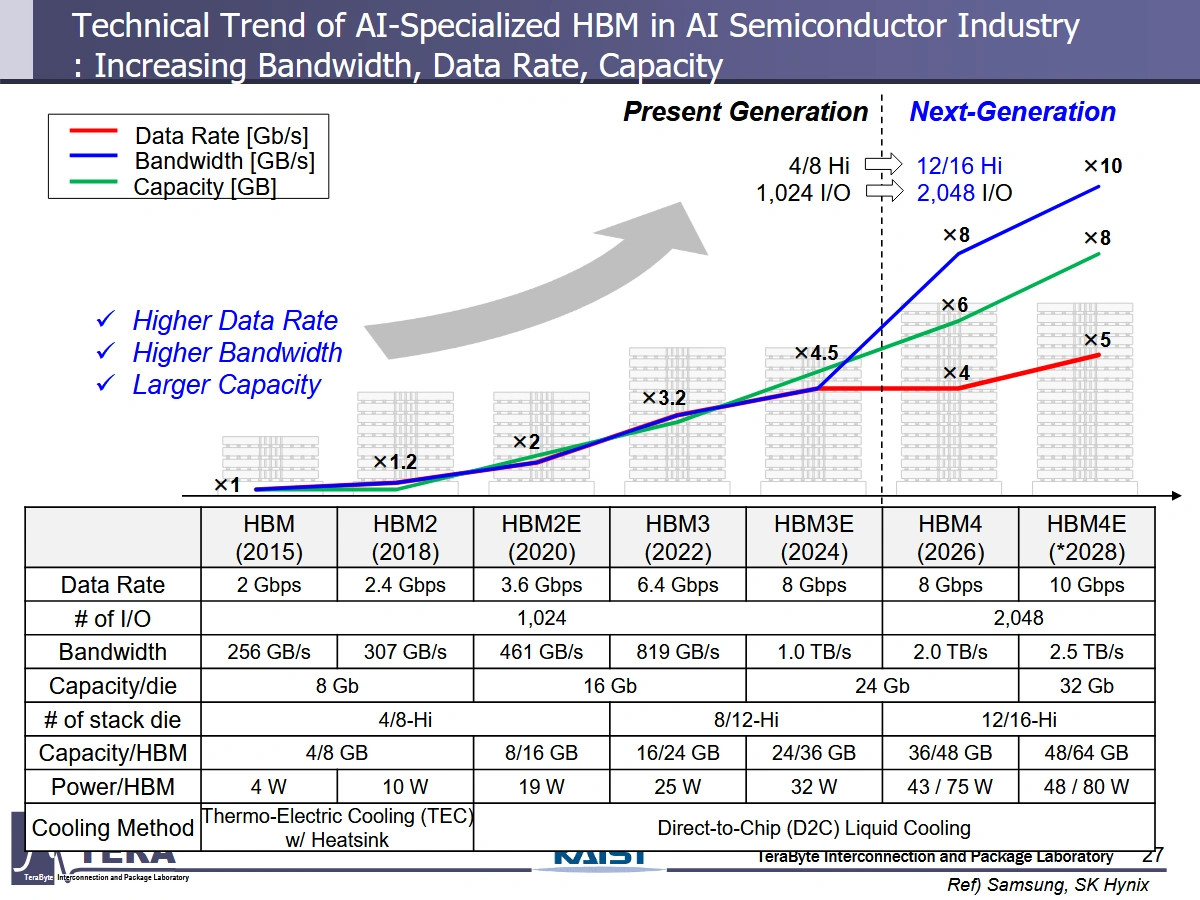

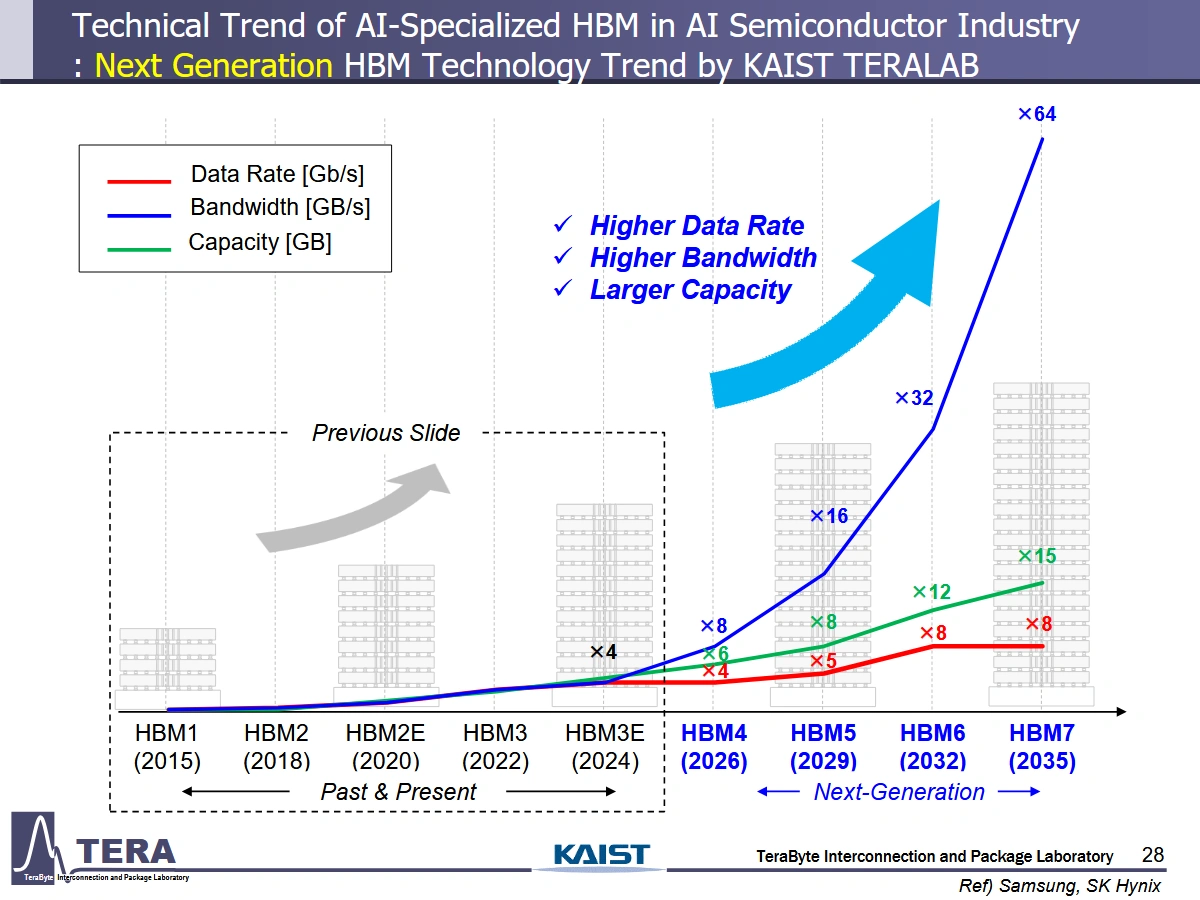

Lors d'un grand atelier, l'université KAIST (Korea Advanced Institute of Science and Technology), un institut majeur du pays, a publié un papier de 371 pages détaillant, entre autres, les évolutions de la High-Bandwidth Memory (HBM) de la HBM4 de 2026 à la HBM8 de 2038 ! Ce long document couvre de nombreux détails techniques habituels comme la bande passante, la capacité, la taille du bus et la consommation, mais identifie aussi l'adoption de diverses nouveautés technologiques.

Attention, ce papier n'est pas une feuille de route commerciale, mais est une spéculation portant sur l'évolution technologique théorique de la HBM basée sur les tendances actuelles. Autrement dit, c'est un aperçu de ce qui est envisageable aujourd'hui pour ce type de mémoire, cherchant à poser les bases pour les futures technologies et du travail à accomplir au fil des prochaines années. Au passage, à partir des calendriers connus des fabricants, KAIST a également tenté de prédire partiellement le futur de l'accélérateur IA.

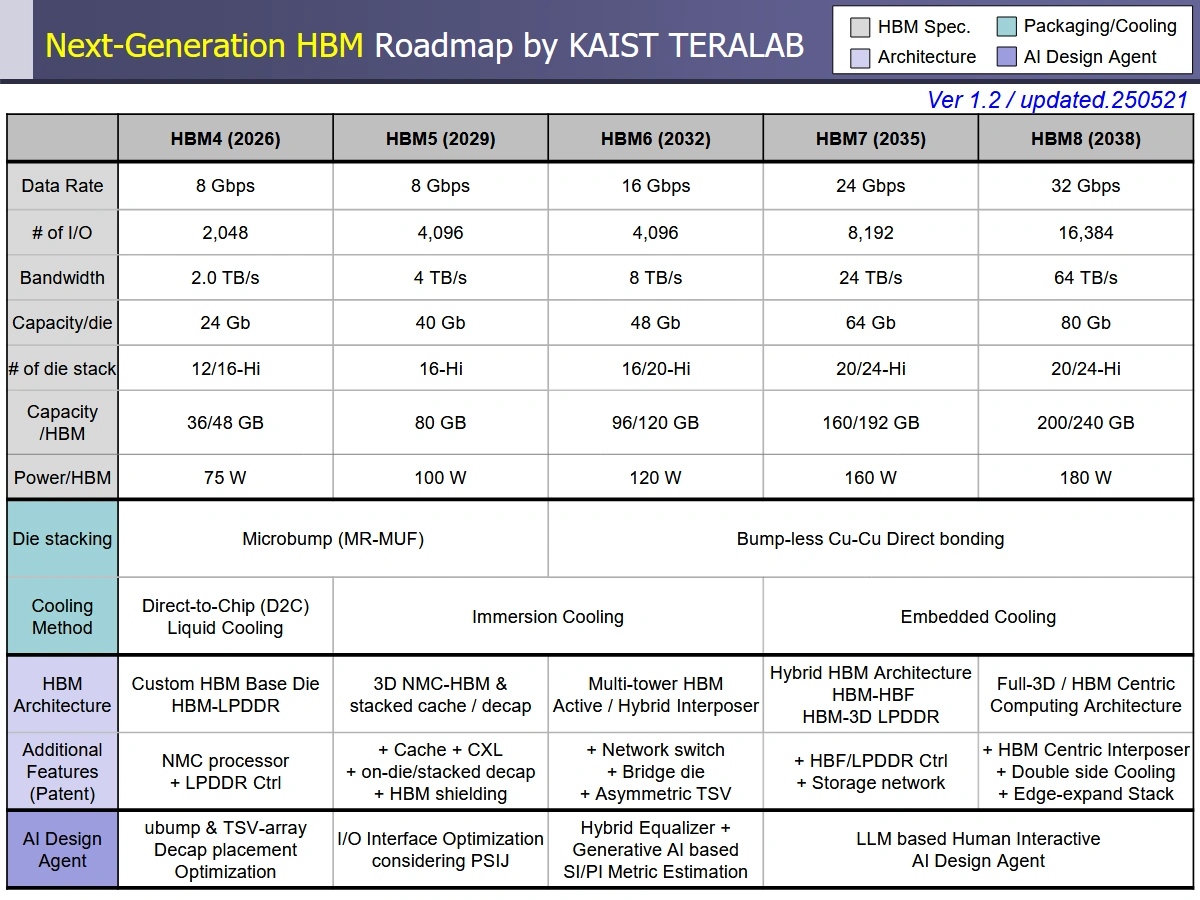

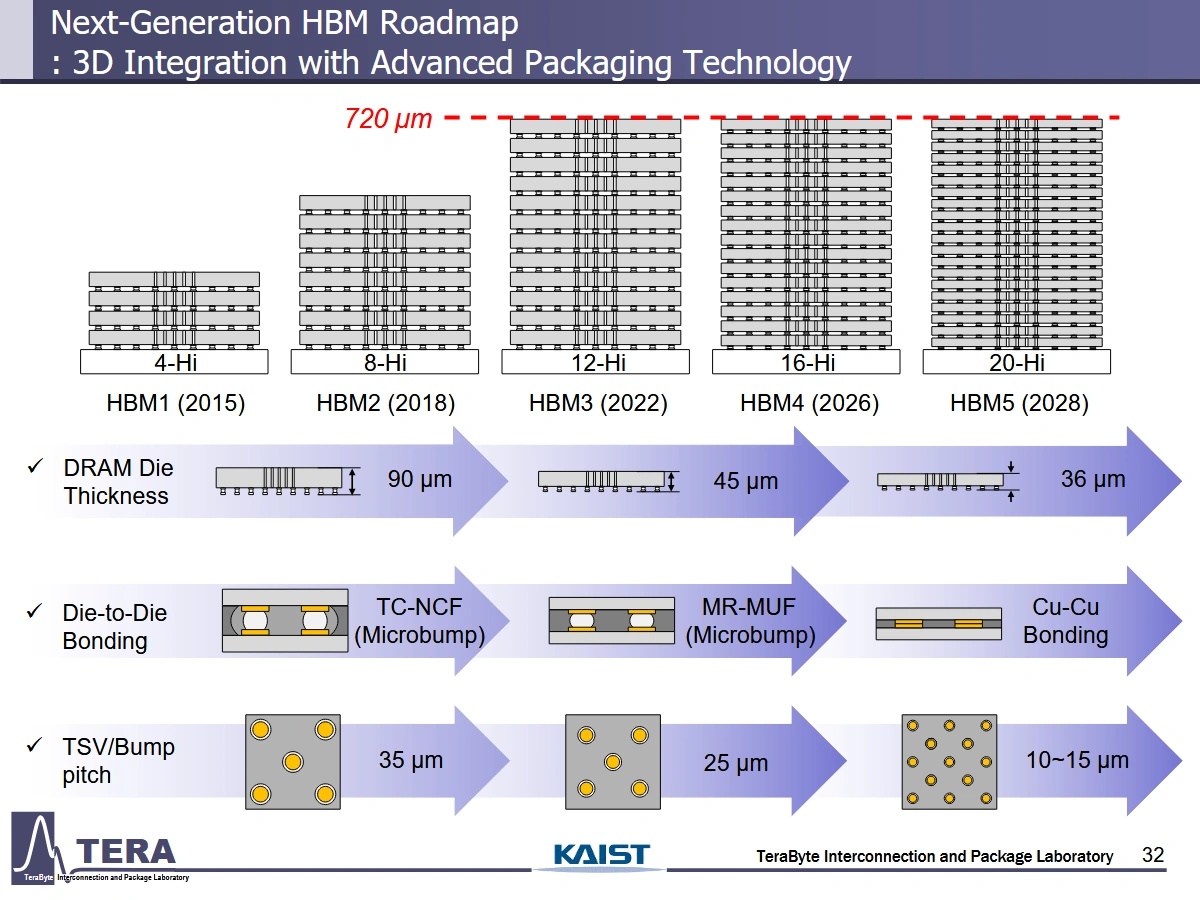

L'évolution de la HBM de 2026 et 2038 pourrait être assez dramatique, avec une augmentation progressive, tantôt explosive, des prestations offertes ! De 8 à 32 Gb/s, d'un bus de 2048-bit à 16 384-bit, d'une bande passante de 2 To/s à 64 To/s, d'une hauteur de pile de 12 étages à 24, d'une capacité de 36 à 240 Go, d'une consommation de 75 W à 180 W... La HBM8 de ce futur spéculatif est un monstre ! Ajoutez à cela de nombreuses avancées en matière de conception, de refroidissement et de fonctionnalités clés et l'on obtiendra une future HBM qui serait largement méconnaissable par rapport à la HBM actuelle.

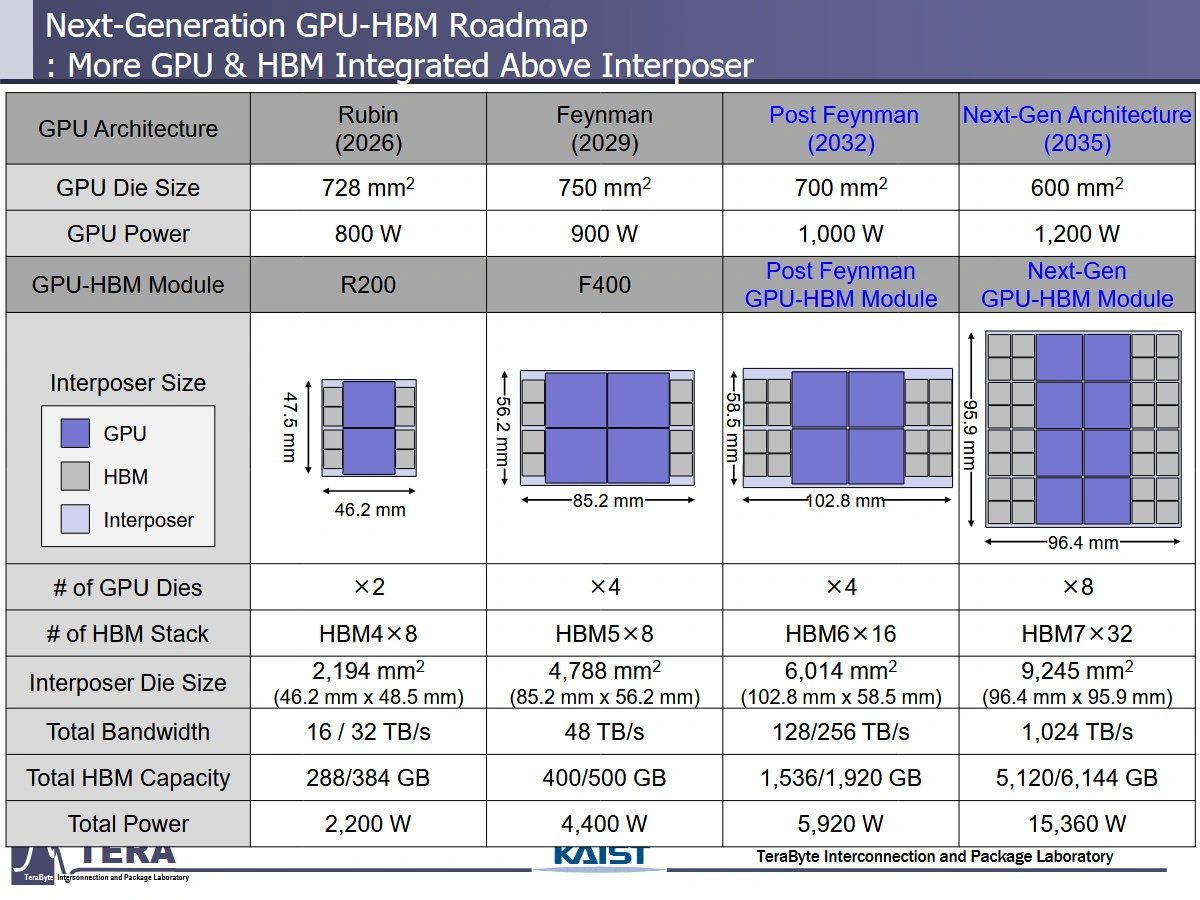

Côté GPU, KAIST est parti de Rubin (la future génération de NVIDIA pour les accélérateurs IA) pour présenter les développements possibles avec ce type de puce, en parallèle de la mémoire HBM, pour les prochaines années. Ici aussi, les projections sont pour le moins ambitieuses ! Pour Feynman, officiellement nommé par NVIDIA en mars dernier, il est imaginé un assemblage de 4 dies de 750 mm² associés à de la mémoire HBM5 pour une capacité totale comprise entre 400 et 500 Go. La consommation totale serait doublée par rapport à Rubin Ultra. On devine d'ailleurs sans mal que le dégagement thermique figurera assez indéniablement parmi les plus gros défis pour ces futurs accélérateurs, pour lesquels une enveloppe théorique de 15 360 W est même présentée comme étant une possibilité à l'aube de 2035 ! Notez d'ailleurs que KAIST entrevoit une certaine stagnation en matière de taille pour les puces, une contrainte qui serait alors contournée en assemblant tout "simplement" de plus en plus de puces avec de plus en plus de HBM.

Évidemment, bien qu'intéressant et méritant le coup d'œil, tout ceci n'est certainement pas pour demain et reste théorique ! Cette feuille de route suppose, d'une part, que les évolutions se poursuivent en ce sens et sans embuches, et d'autre part, le développement avec succès de nombreuses nouvelles technologies par les fabricants concernés. Bref, la HBM de demain pourrait ressembler à ça, ou pas... (Source : Tom's, Hardwarluxx)

Le PDF complet du papier de 371 pages de KAIST.

C'est très intéressante tout ça

Juste sur leurs projections ils oublient un truc l euv na va arriver pas pour rubin mais très probablement des son remplaçant

L euv na a plein de qualité mais elle oblige une taille maximale des die a 429 mm² du coup leurs projections sont un peu improbable

D'ici là je parie 2 Twix qu'on aura toujours des RTX avec 8 Go de VRAM... 😅

👀

Neural Texture Compression - Better Looking Textures & Lower VRAM Usage for Minimal Performance Cost