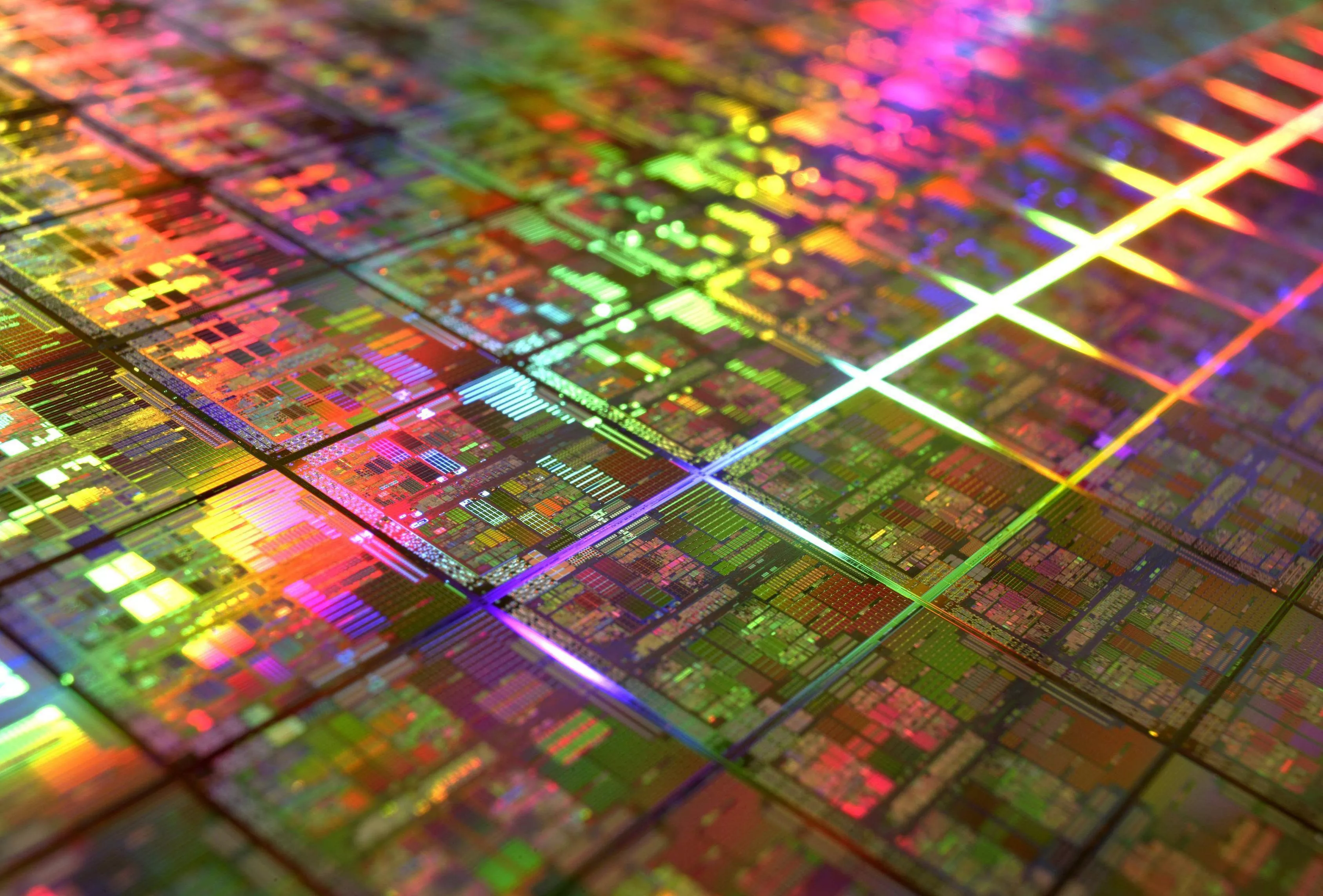

À chaque génération de cartes graphiques et de processeur, la comptine est la même : de manière à maximiser les rendements de production, une même puce est réutilisée sur toute la gamme, mais avec des cœurs/du cache désactivés. Par exemple, le GB203 de la NVIDIA RTX 5080 est également intégré dans la RTX 5070 Ti, une fois castré de 1 792 cœurs CUDA. En pratique, la raison est simple : produire des puces n’est pas un procédé parfait, si bien que des défauts de gravure sont présents sur certaines d’entre elles en sortie d’usine. Si l’on est chanceux — ou statisticien —, il est possible de désactiver la partie défectueuse et revendre la puce dans une gamme inférieure, perdant quelques cœurs, du cache ou encore un accélérateur au passage (citons les Intel suffixés F, sans iGPU).

Racontée de cette manière, la chose semble drôlement simple, pourtant derrière le terme de « défaut de gravure » peut se cacher une multitude de phénomènes aux conséquences plus ou moins graves. Voyons tout cela au microscope électronique à transmission.

Dans ces premiers cas, un corps étranger s’est retrouvé sur la galette de silicium : inutile de vous dire que les contacts ne vont pas aimer, particulièrement si ladite particule se révèle être conductrice !

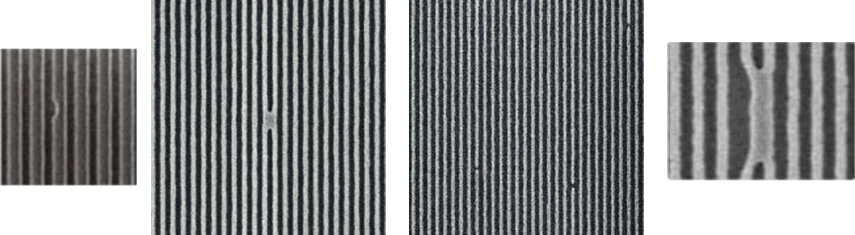

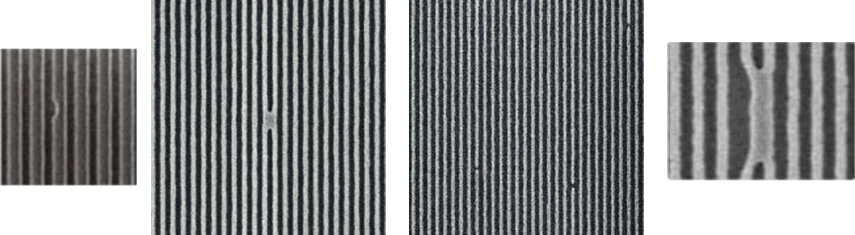

Plus embêtant encore, les câbles (lignes blanches sur ces images) peuvent dévier du tracé rectiligne qui leur est normalement imposé. On parle alors de morsure de souris (mouse bite, image de gauche) lorsqu’une partie de la ligne manque, occasionnant potentiellement des perturbations des signaux, voire des connexions rompues. En cas de surexposition, un phénomène de pinching peut également se produire : une semi-disparition de la piste. Si cela ne rend pas forcément le design inopérant, vous imaginez bien que des erreurs se produisent préférentiellement sur ces structures lors des overclockings ou d’augmentation un peu trop optimiste de la tension.

Pire, des connexions de ponts sont parfois présentes (bridge, seconde image en partant de la gauche), entraînant du parasitage entre deux canaux. À l’inverse, les contacts peuvent tout bonnement être coupés (troisième image en partant de la gauche), on parle alors de line breaks ou de gaps. Enfin, il peut arriver que des lignes fusionnent par capillarité, menant à des line collapse (image de droite ci-dessus). Là encore, le résultat est inutilisable !

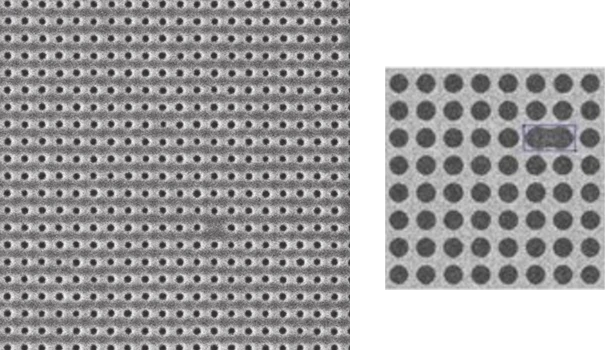

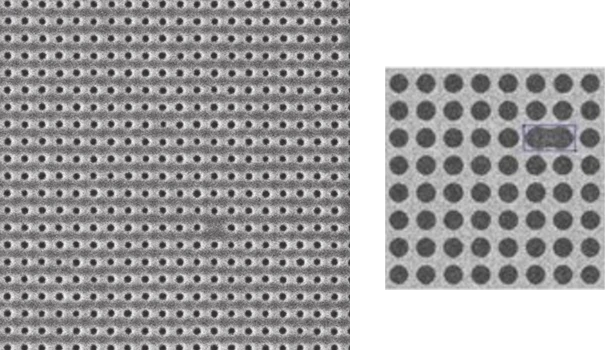

En outre, les interconnexions ne sont pas les seules sources d’erreur : les points de contact (là où la puce est soudée, ou sur les vias permettant les connexions entre couches) peuvent également être sujets à des défauts : soit par leur absence (image de gauche ci-dessus), ou par la jointure non désirée de deux trous adjacents. Dans un cas comme dans l’autre, mieux vaut compter sur de la redondance pour éviter d’envoyer les dies à la benne à ordure ! Voilà de quoi expliquer la présence de code de correction d’erreur directement dans le standard DDR5 — bien que la chose ait été déjà effectuée en interne depuis quelques générations.

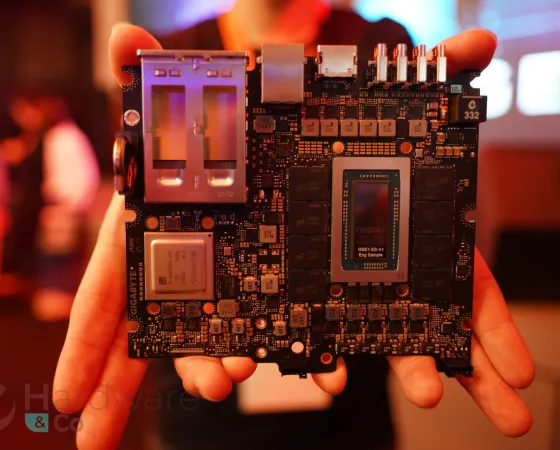

Une fois ces défauts détectés et identifiés en étudiant les puces défectueuses, les fondeurs doivent encore remonter à la cause du problème : mauvaise purification des composés, procédé de gravure encore mal maîtrisé, paramétrage de la machine insuffisant… les raisons sont multiples, et l’expertise nécessaire pour corriger tout cela ne court pas les rues ! De quoi expliquer la grande loi du semiconducteur : plus on produit, mieux on produit ; et, ainsi, justifier à la fois la domination de TSMC et le virage d’Intel en tant que fonderie ouverte aux designs tiers. (Source : Always Be Curious)

Petites erreurs que je suppose : "Mouse bite", image de gauche et pas de droite.

"Bridge", deuxième image et non pas la troisième.

"Line breaks", troisième image en partant de la gauche et non pas en partant de la droite.

Sinon, article très intéressant, merci !

Connerie de droite et de gauche, quand on se tourne ça change tout le temps ! Merci, je me suis effectivement emmêlé les pinceaux 🙏

@Montagnera

tu as un petit bouton [Signaler un truc] pour ça.

Intéressant, on n'a pas souvent l'occasion de traiter de ces sujets. Maintenant question : comment sont vérifiées les puces et comment sont-elles triées ? :)

Historiquement, il y a toujours eu un tri par test "automatique" des fréquences pouvant être atteintes.

En effet, par exemple, déjà à l'époque des Pentium, ce qui différenciait un P75 d'un P90 (P54C pour les deux), ce n'était pas le process de fabrication, mais seulement le test de monter en fréquence que pouvait atteindre le die. C'était d'ailleurs la raison pour laquelle un P90 coutait plus qu'un P75 => plus "rare".

La grande erreur dans la production de masse est de croire que tout est maitrisé et que les maths sont la réalité. Il n'y a rien de plus erroné. Dans le monde réel les quotas et autres marges d'erreurs sont la pour palier les disparités entre la théorie et la pratique, la conception et la production.

Comme évoqué par Nicolas D., à juste titre, => "peut se cacher une multitude de phénomènes aux conséquences plus ou moins graves"

Désormais, il apparait que le tri est bien plus complexe. Car il faut en premier lieu déterminer ce que l'on évoque dans les tris (impuretés wafers, défauts de gravure lithographique, ...)

Ce qui implique, vous l'aurez deviné, une multitude de méthodes (analyse électrique, visuelle, ....)

Exemples :

https://www.cityu.edu.hk/phy/appkchu/AP6120/5.PDF

https://www.asml.com/en/technology/lithography-principles/measuring-accuracy

Bonne journée.

Pour avoir travaillé dans une fonderie, je peux vous confirmer que c'est un univers impressionnant de précisions et de contrôles, mais hélas insuffisants.

Chaque machine, qui tourne H24, est calibrée avec une certaine marge d'erreur et est contrôlée plusieurs fois par jour via des wafers tests qui sont analysées avant et après passage dans la machine.

Le contrôle peut être visuel, mais de moins en moins vu les finesses atteintes.

Ce qui peut jouer énormément sur le rendement aussi, c'est le cumule de process aux limites fixées :

Et pour rebondir sur le commentaire précédent, dans le monde réel, il y a un élément terrible, et notamment pour nous, Français, c'est la discipline ou plutôt l'absence de discipline totale des employés en fonderie (dont j'ai fait partie). Les process d'habillement non respectés qui font entrer des micro/nano particules dans les salles blanches, les manipulations manuelles interdites mais faites quand même pour gratter qq secondes, le non respect de l'étanchéité des combinaisons pour x raisons (se gratter, se moucher, envie changer de gants, parler, s'embrasser...oui oui, j'ai vu de tout) fait que les contaminations aux particules d'origines humaines sont nombreuses. Et là, en sortie de chaîne, la puce peut tout à fait être fonctionnelle comme prévu mais rendre l'âme au bout de qq jours, semaines, mois... le temps que la partie organique en contact avec les circuits dégrade ces derniers de differentes façons. Ce qui est totalement invisible en SAV. Oui, dans la production de masse, tout est loin d'être maîtrisée.

C'est beau l'amour, même les transistors ils veulent parfois se rapprocher de leur confrère/soeur 🥰

Merci Nicolas pour ces infos et ces photos qui sont les premières du genre que je vois ! 👍

@ SaoYoh

Tellement vrais tes propos !

Je travaille dans le test et programmes de test en électronique, je vois ça presque tout le temps !

Les limites liées au design ainsi que le process peuvent causer de gros problèmes de rendement.

La discipline est aussi un vrais problème et aussi on est toujours trop pressé, la pression est élevée pour sortir les produits coute que coute...

C'est vrai que lorsque l'on ne baigne pas là-dedans, on s'imagine mal toute la complexité du process et ce qui peut se passer.

Merci pour la brève très intéressante et les commentaires également :-)