Avec l’émergence du machine learning, les processeurs ont vu leurs capacités de calcul augmentées par (encore) un accélérateur de plus : les NPU. Ainsi, un « processeur » haut de gamme est désormais un SoC (System-on-Chip), c’est-à-dire un assemblage de plusieurs blocs logique (on parle d’IP pour Intellectual Property afin de désigner l’architecture de ces blocs) qui intègre un CPU, un GPU, un NPU et divers autres accélérateurs dédiés à l’encodage et au décodage de média. Bref, un sacré fouillis dans lequel, fatalement, il y a matière à optimiser. Comprenez que tous les transistors ne sont pas actifs en même temps sur une puce, et donc que cette dernière est loin d’être utilisée à 100 % de ses capacités, même dans les tâches les plus lourdes.

Partant de ce constat — et oubliant visiblement qu’une des raisons à cela est de permettre de dissiper correctement la chaleur induite par le fonctionnement desdits transistors — la start-up Ubitium s’est mise dans la tête de créer un processeur universel, c’est-à-dire dont les entrailles sont reconfigurables de manière à s’adapter à la tâche souhaitée. Une puce reconfigurable, cela existe déjà et se nomme FPGA — une classe de processeurs offrant aux programmeurs/architectes quelques centaines de milliers de portes logiques programmables de manière à créer sur-mesure un circuit —, mais avec le désavantage d’une puissance diminuée d’un facteur 100 à 1000 par rapport à une implémentation « en dur » (des circuits nommés ASIC).

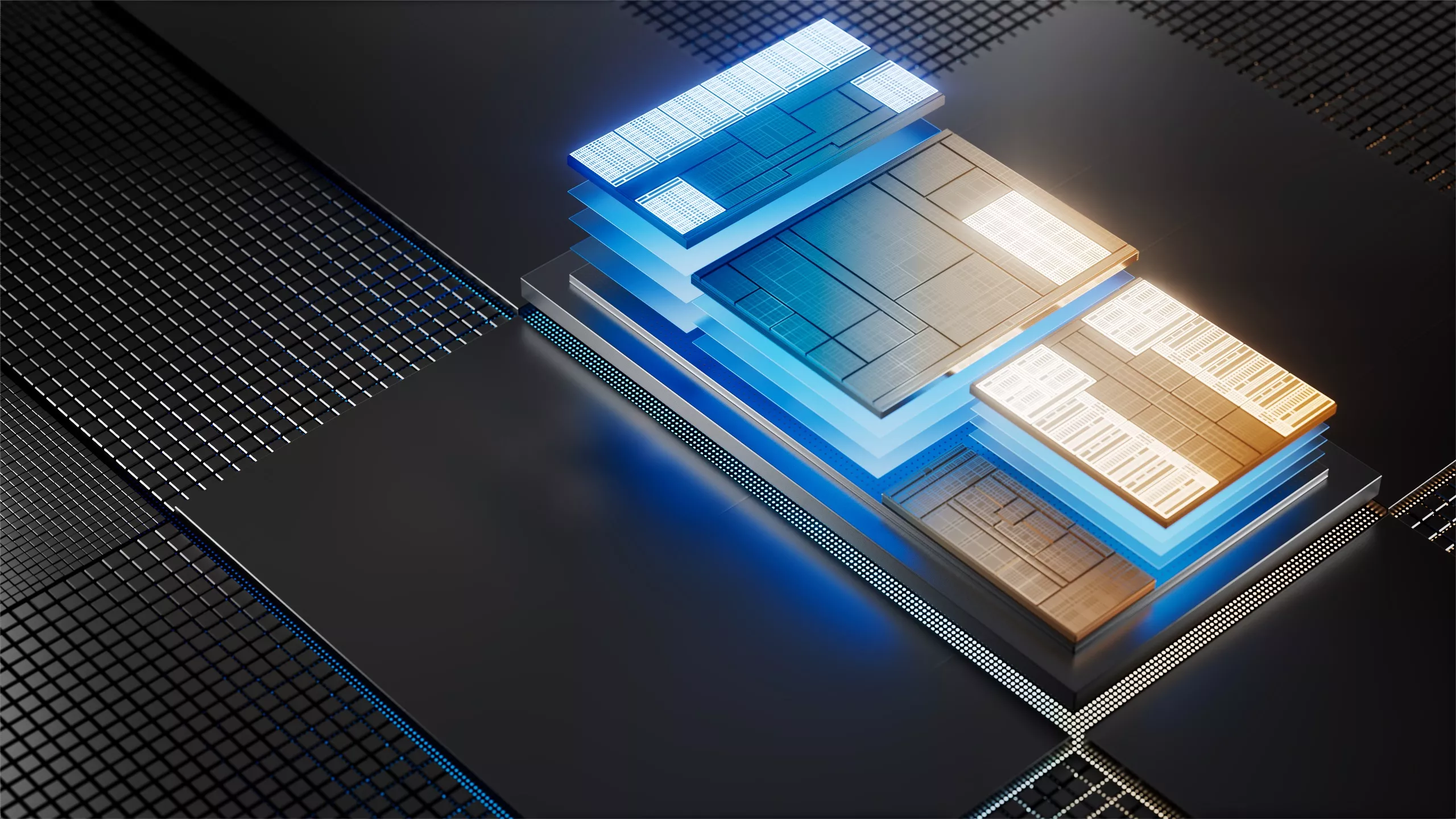

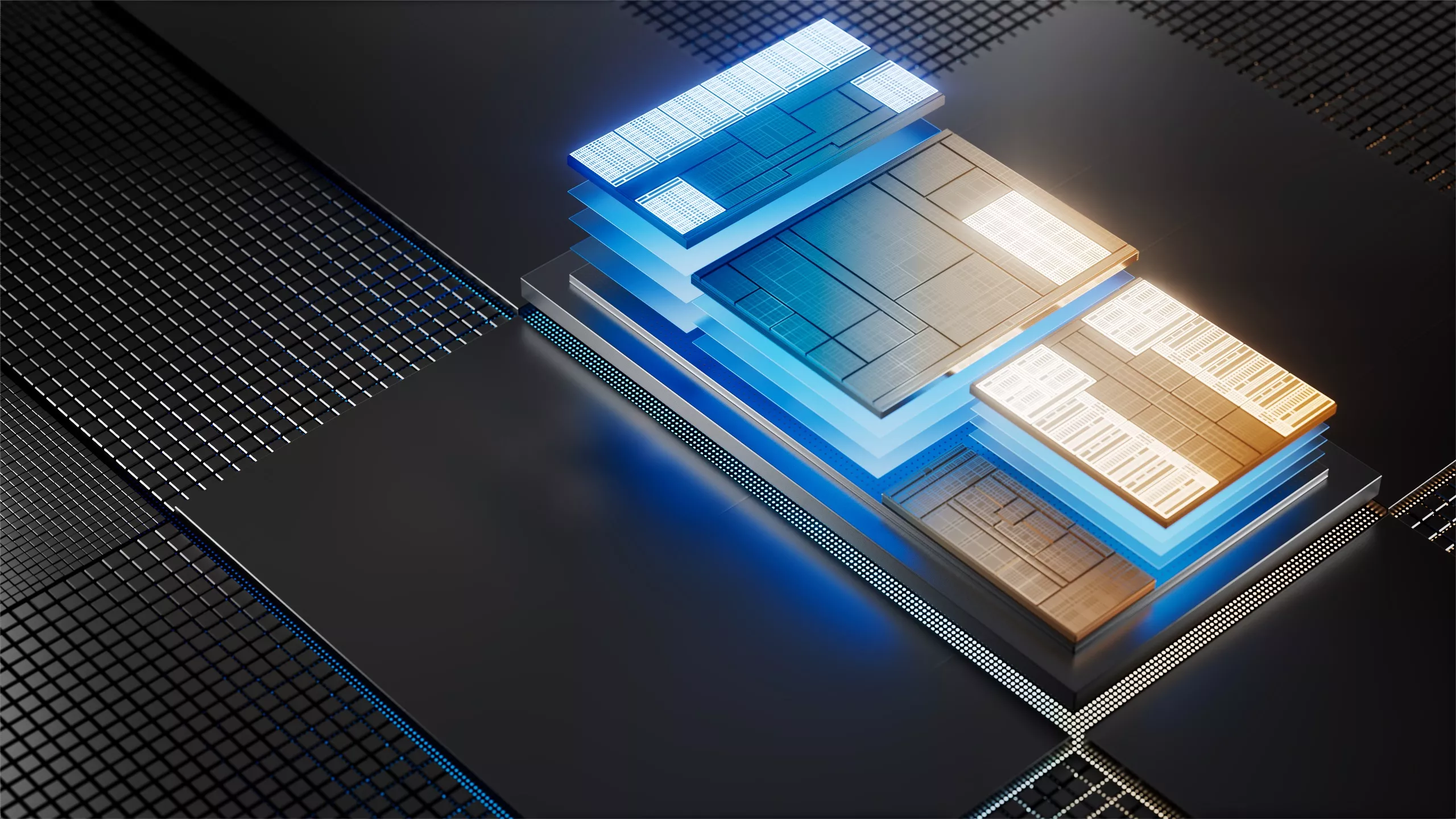

Pour le moment, la tendance est plus à poser tous ces accélérateurs côte à côte que fusionnés

Tour de passe-passe ? Arnaque ? Tout est possible. La firme est — évidemment — avare en détails, mais le même principe a mené Intel a déposer, il y a quelques années, un brevet sur le concept de Renting Units : des unités de calcul mobiles entre les cœurs de manière à maximiser le partage de ressources au sein d’un CPU. Votre humble serviteur a également travaillé sur un concept similaire sur FPGA ; vous sentez venir à quel point le bousin est dans l’air du temps ! Toutefois, la firme communique sur une compatibilité avec le jeu d’instructions RISC-V, le bousin prenant donc l’interface d’un CPU classique, avec un back-end permettant « de reconfigurer un tableau [d’unité de calcul] pour une exécution en dataflow ». De quoi évoquer les CGRA, des processeurs imaginés dans les couloirs de labo de recherche constitués d’unités semi-spécialisées, mais reconfigurables ; la chose n’ayant jamais réellement pris du fait de sa complexité — particulièrement à la compilation des programmes — et de gains de performances limités à certaines applications seulement. Notez toutefois qu’une partie de ces idées se retrouvent dans les réseaux systoliques des accélérateurs de machine learning, comme quoi tout finit par se rejoindre !

Au niveau des gus à la tête de la chose, nous retrouvons des anciens de chez Intel, Nvidia, et Texas Instruments, qui ont pour le moment levé 3,7 millions de dollars de fonds… ce qui n’est pas vraiment suffisant encore pour les prétentions de l’entreprise, qui souhaite d’après leur site web proposer des designs allant de l’automobile à l’aérospatial en passant par l’IoT et, bien sûr, l’IA. Reste que le premier Universal Processor est prévu pour 2026 : nous verrons donc assez rapidement si le bousin tient la route ! (Source : Techspot)

Par ici pour le site officiel de la start-up !

<Votre humble serviteur a également travaillé sur un concept similaire sur FPGA>

C'est cool ça !

Et projet cool ! Je me suis toujours demandé pour les FPGA n'étaient pas plus grand publics, je pensais naïvement a des problèmes de licences/foundry d'Intel qui n'y avait aucun interet. Aurais-tu un papier ou deux sur le sujet peut-etre?

Travaillé ne veut pas dire que c'était très au point, ni que ça a vraiment été valorisé. Le projet était de faire automatiquement un design qui fusionnait des unités d'exécution reprenant les motifs de calcul commun à plusieurs applications ; mais ça mettait trop de contrainte sur le contrôleur mémoire pour être efficace, et on payait énormément en interconnect ; mais c'est pet-être lié à l'archi des FPGA.

La réponse est simple : qu'est-ce que le grand public en ferai ? C'est encore plus complexe à programmer qu'un CPU ou un GPU donc, clairement, ça serait "juste" une carte accélératrice... Or il n'y a pas d'applis suffisamment déployée qui justifierait un FPGA grand public (autrement que pour tricher en jeu avec un accès direct à la RAM et injecter des fausses valeurs). Il n'y a que Apple qui en avait mis un dans un Mac Pro pour déporter de l'encodage vidéo, je ne sais pas ce que ça a donné mais comme ça n'est plus disponible, je pense que ça n'a pas été une franche réussite.

D'abord pour rebondir sur les FPGA, on les a souvent vu pour des opérations très spécialisées qui demandaient des mises à jour hardware (décodeur dans les lecteurs DVD, G-SYNC), mais leur coût de fabrication les rendent peu attractifs à la production de masse (et ce n'est pas très compressible). Pour ce qui est des performances, c'est encore un débat, il suffit de voir certains papiers qui démontrent en inférence comment des modules/puces de chez NVIDIA se font exploser dans le machine learning, juste en exploitant les propriétés de ces puces.

Bon, par contre l'humble serviteur ne dit pas que c'est pas très productif actuellement (et ne mens pas, t'es venu dans notre équipe exposer le problème 😜), vouloir tout mettre dans un même SoC est une contrainte incroyable, et exploiter FPGA ou CGRA apportera tout autant son lot de soucis. En vrai c'est très chouette, mais à ce jour quand on voit la galère à déployer les systèmes Versal chez AMD (ce qui s'en rapproche le plus dans l'idée) tellement le boulot autour est immense, je vois mal comment une startup (tout autant que les gens soient expérimentés) constituée d'une poignée de personne va révolutionner le game, ça sent plutôt l'idée de se faire racheter au plus vite par un plus gros poisson.

J'ai fait mon PhD en physique des plasmas, "pas très au point" et "pas trop valorisé" je connais...

De loin j'ai l'impression que les archis des LLM pourraient rapidement changer, il y a eu des essais avec des int uniquement pour économiser de l’énergie. Aujourd'hui j'aurais du mal à mettre 50k dans un GPU pour faire du FP16 alors que du FP4 ou int pourrait bien marcher. Je suis peut-etre pingre et/ou optimiste sur l'évolution des LLM...

Pour l'entrainement, c'est encore compliqué, quoique en FP8 ça vient petit à petit. Par contre, pour de l'inférence, le INT8/4 est très utilisé aujourd'hui, suffisamment efficace la majorité du temps. Pour ce qui est d'optimiser la perf, mon avis est qu'on va trop vite côté fabricant avant que la recherche ait fixé quelque chose d'efficace et rentable.

AMD avait déposé un brevet peu de temps après le rachat de Xilinx pour faire un truc du style. Mike Clark avait même déclaré qu'il ferait un truc avec Xilinx dans Ryzen. Très évasif malheureusement, j'espère qu'il ne parlait pas de XDNA mais d'un truc un peu plus sexy.

Non ça n'est de sûr pas XDNA, XDNA est l'inverse : une techno tirée initialement d'unités spécialisées (AI Engines) mises sur certains types de FPGA, ensuite reprises dans des CPU. Je pense qu'il y a des soucis de performances à mettre des bouts de FPGA dans des CPU : la techno FPGA n'est à mon avis pas la bonne pour ça car trop en retrait en matière de performance (car trop générique). L'avenir est probablement un hybride avec des unités reconfigurables pour pouvoir faire plusieurs choses, mais pas n'importe quoi comme un FPGA. Si l'on réfléchit un peu, les unités AVX peuvent fonctionner en FP16, FP32 et FP64, c'est déjà une certaines sorte de reconfiguration très primaire.

C'est exactement ce à quoi je pensais pour du grand public.

Peut-etre meme aller jusqu'à du FP8 ou FP4 selon les évolutions de la quantization des LLM.